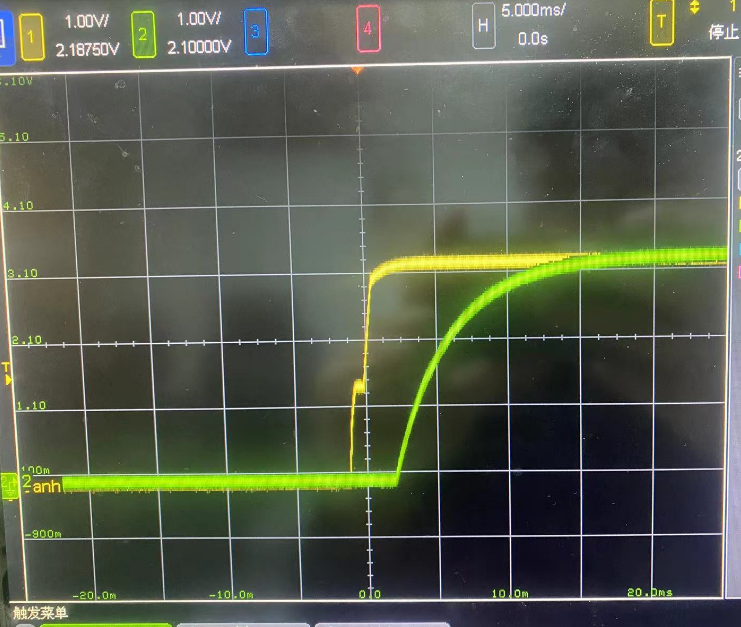

在MCU上电过程中,因为电源的设计或者其他器件上电导致上电波形有阶梯等情况,比如下面这个VDD波形:

那如何判断这个波形是否会影响MCU启动呢?

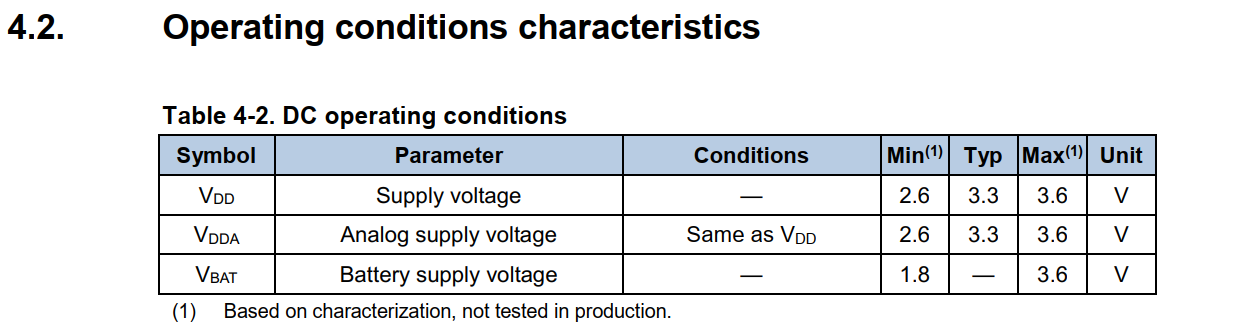

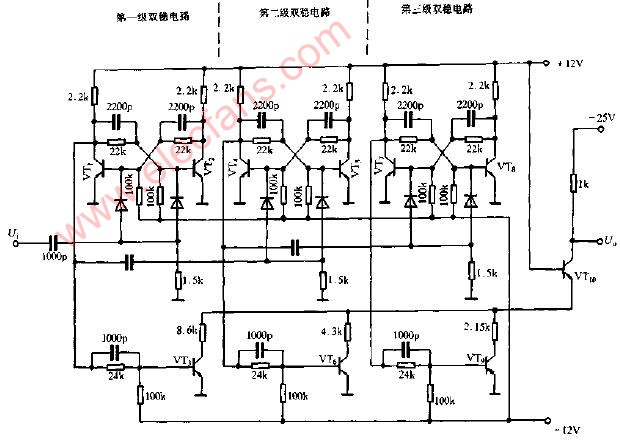

以GD32F303为例,首先我们看一下DATASHEET,VDD和VDDA的供电范围是2.6V-3.6V:

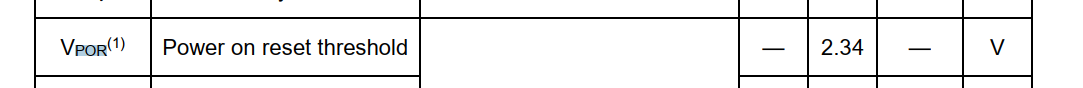

MCU上电复位的POR电压是2.34V:

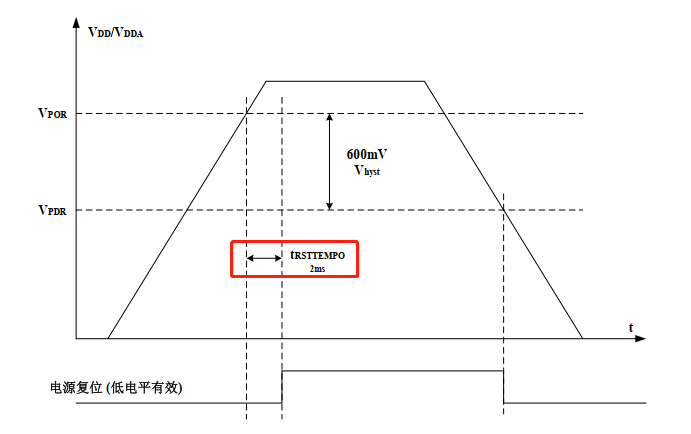

再查阅用户手册上电复位描述可知,MCU VDD电压到达POR电压值时会有2ms的迟滞时间再拉高启动:

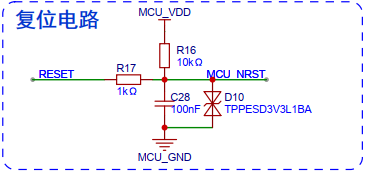

同时MCU最小系统中NRST引脚也有RC电路,会延迟NRST拉高到VIH

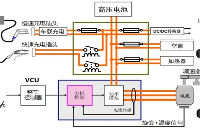

所以我们可以抓取VDD波形时同时抓取NRST波形:

可以看到NRST达到它的VIH电压时VDD波形已经稳定了,此时MCU启动电源是可靠的,我们可以忽略电源的阶梯和爬升对MCU的影响。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电源

+关注

关注

184文章

17710浏览量

250021 -

单片机

+关注

关注

6036文章

44555浏览量

634856 -

mcu

+关注

关注

146文章

17141浏览量

351058

发布评论请先 登录

相关推荐

LTM4644上电波形多次震荡的原因?

接电源地,电容用来调节上电斜率。

1.0V上电波形有多次震荡,通过排查发现是22nF电容问题导致,想问一下,这个波形震荡与SS管脚这个电容容

发表于 03-06 07:57

如何处理由电源引起的MCU启动失败?

,从而出现器件闩锁,系统不能启动的情况。 掉电缓慢也会导致MCU等数字器件内部掉电时序的混乱,特别是对于需要多路电源的MCU处理器,它们对于上电

发表于 05-31 11:33

AM3358上电模式对处理器的性能是否有限制?上电时序的间隔时间是否有严格要求?

相对于其他上电模式,这种上电模式对处理器的性能是否有限制,如工作频率的限制。2. 图示中VDD_CORE和VDD_MPU都是1.1V的,若两者电压不同该如何

发表于 06-04 06:24

7200 EN引脚的上电波形异常

`新人求助!在测7200芯片时发现,EN引脚有一个 掉电波形,确定了EN脚的电压是从主板芯片产生的,会比5V时序偏后。我把R5去掉之后,波形就很好,我分析应该是这个5V的分压影响了EN,但是不明白怎么会出现一个下冲波形,如果芯片

发表于 09-11 17:37

电源上电缓慢时,MCU如何继续完成相应操作?

的电源设计来说,这个时间甚至可能会远远大于500ms。这样的话就不能很好地满足芯片的上电时间要求,从而导致系统无法启动,或者器件内部上

发表于 09-01 07:00

上电缓慢或有阶梯?如何判断上电波形是否满足MCU要求

上电缓慢或有阶梯?如何判断上电波形是否满足MCU要求

评论