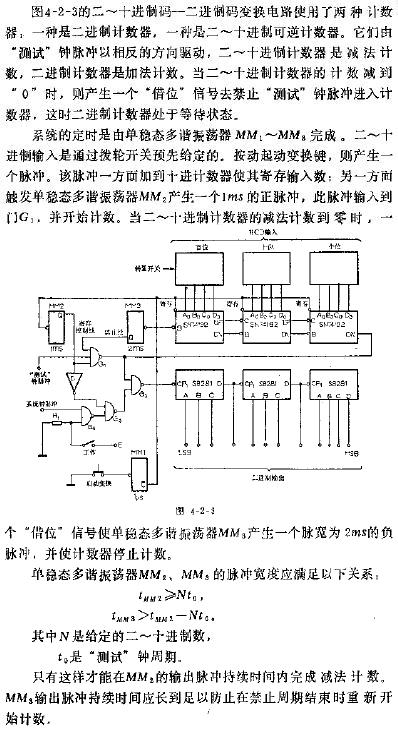

总体方案设计

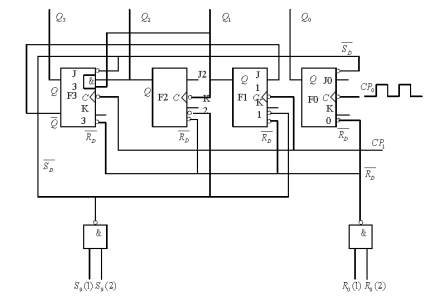

本设计使用EWB进行仿真,使用74LS48、七段译码器、LED、开关、异或门、或门、非门、与非门等。电路按功能分为三个部分:减数部分:减数变成补码(原码取反加1);被减数部分:被减数与减数的补码相加;差部分:被减数减减数的结果显示。四位二进制减法器的总体仿真图如图所示。

图9 四位二进制减法器的总体仿真图

被减数模块的设计

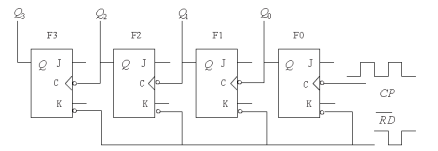

本模块由开关、74LS48、VCC(+12 V)、GND、七段译码器构成,用开关控制输入信号( 被减数),5、6、7、8 从高位到低位,用74LS48和七段译码器构成显示电路。四位二进制减法器的被减数模块的仿真图如图10所示。

图10 四位二进制减法器的被减数模块的仿真图

减数模块的设计

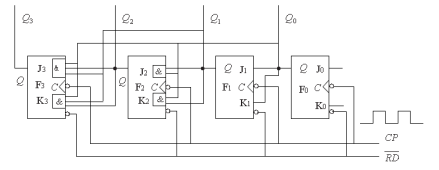

本模块由开关、74LS48、VCC(+12 V)、GND、七段译码器、异或门、或门、非门、与非门构成。用开关控制输入信号(减数),1、2、3、4 从高位到低位,将输入信号的原码变成补码供计算使用,用74LS48 和七段译码器构成显示电路。四位二进制减法器的减数模块的仿真图如图11所示。

图11 四位二进制减法器的减数模块的仿真图

差模块的设计

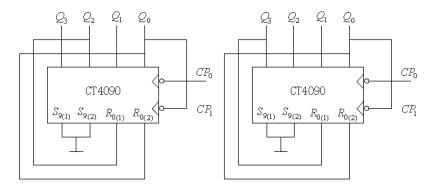

本模块由VCC(+12 V)、GND、七段译码器、74LS48、LED 构成。从右到左依次是从高位到低位,并用74LS48和七段译码器构成显示电路。四位二进制减法器的差模块的仿真图如图12所示。

图12 四位二进制减法器的差模块的仿真图

-

二进制

+关注

关注

2文章

801浏览量

41779 -

显示电路

+关注

关注

6文章

97浏览量

33287 -

减法器

+关注

关注

1文章

26浏览量

16891 -

GND

+关注

关注

2文章

540浏览量

38929 -

74ls48

+关注

关注

1文章

13浏览量

11827

发布评论请先 登录

相关推荐

4位二进制乘法器电路

如何理解二进制运算规则 二进制是如何运算的

集成四位二进制计数器

本的二进制加法/减法器,本的二进制加法/减法器原理

DM74LS83A四位快速进位二进制加法器的数据手册免费下载

四位二进制减法器的设计与实现

四位二进制减法器的设计与实现

评论