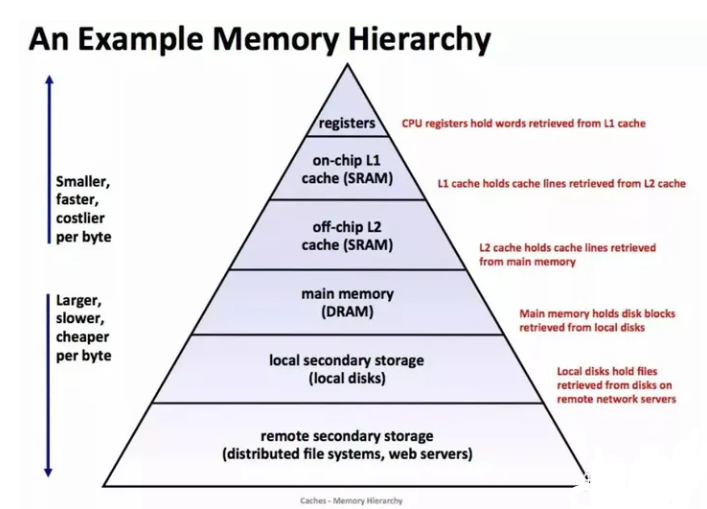

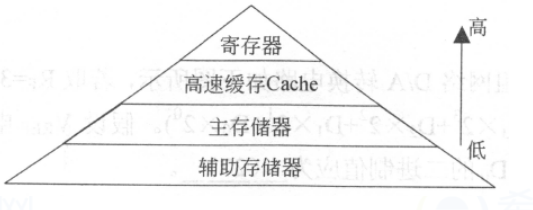

存储器层次结构可以从图片中清晰的看出来,图片中共分为六级,越向上的层次,存储器速度越快,容量更小,造价越高。

L0层为寄存器,寄存器从硬件的角度来说即触发器( flip-flop ), 通常一个触发器可以由两个锁存器( latcher )和逻辑块组成,触发器为边沿有效,锁存器为电平有效。寄存器集成在CPU内部,制作在CPU内的寄存器不可能容量太大,另一方面实际上CPU并不需要太多的寄存器,寄存器太多反而可能会减慢运行速度。目前的主流的片内寄存器数量为32个(或者64个?)。汇编语言中操作的寄存器也就是指的这些。寄存器由于在片内,避免了线延迟。

L1-L2为两级高速缓存( cache ),这两级存储为SRAM,s即static,指静态,最常见的SRAM为6T结构。高速缓存主要解决CPU计算速度和主存读写速度不匹配的问题,如果没有这两级,有关于内存的读写指令(如load和store)将会严重影响整体速度。高速缓存也一般集成在CPU上。目前主流CPU已经存在3级高速缓存。

L3为主存,即我们电脑中所谓的内存,为DRAM,d即dynamic,即动态,DRAM常见的有1T和3T结构,通过电容存储信号,需要经常刷新不然电荷会漏光。DRAM速度要低于SRAM,但可以明显看出1T只用了6T六分之一的晶体管,节省了六分之一的面积。

L4为磁盘内存,也就是我们所说的硬盘。以上的RAM都是掉电失去信息的,而硬盘中的内容掉电不会失去。目前机械硬盘主流的存储技术为闪存flash,基于EEPROM。

L5层为远端内存,比如网络服务器,这些的读写速度主要取决于网络延时。

为什么要采用这样的分层结构呢?

采用存储器层次结构的主要原因有以下几点:

性能与成本的平衡:不同类型的存储器在性能(如访问速度)和成本(包括制造成本、功耗等)之间存在权衡。高速存储器(如SRAM、Cache)访问速度快,但制造成本高、容量小;而低速存储器(如磁盘、DDR SDRAM)虽然访问速度慢,但制造成本低、容量大。通过构建层次结构,可以充分利用各种存储器的优势,实现性能与成本的平衡。

局部性原理:程序在执行过程中通常会表现出时间局部性和空间局部性。时间局部性指的是程序在某一时刻访问了某个数据后,在不久的将来还可能再次访问该数据;空间局部性则指的是程序在某一时刻访问了某个数据后,在不久的将来还可能访问其附近的数据。利用这些局部性特性,可以在高速缓存中存放最近访问过的数据和指令,从而提高访问速度。

减少平均访问时间:通过合理设计各级存储器的容量和访问速度,可以使得大部分数据访问都在高速缓存或主存储器中完成,从而显著减少平均访问时间。

管理复杂性:随着技术的发展,存储器的类型和容量都在不断增加。采用层次结构可以简化存储器的管理复杂性,使得系统更容易扩展和升级。

采用存储器层次结构是为了充分利用各种存储器的优势,实现性能与成本的平衡,同时利用程序的局部性特性来减少平均访问时间,并简化存储器的管理复杂性。这也是现代计算机系统中广泛采用存储器层次结构的原因。

审核编辑:黄飞

-

DRAM

+关注

关注

40文章

2337浏览量

184552 -

存储器

+关注

关注

38文章

7573浏览量

165319 -

cpu

+关注

关注

68文章

10971浏览量

214377 -

内存

+关注

关注

8文章

3085浏览量

74704 -

网络服务器

+关注

关注

0文章

31浏览量

11022

发布评论请先 登录

相关推荐

全面解析存储器层次结构原理

存储器的层次结构主要体现在什么地方?为什么要分这些层次?

MCP存储器,MCP存储器结构原理

高速缓冲存储器基础知识详细介绍

存储器层次结构如何解释?

存储器层次结构如何解释?

评论