数字减法器电路的基本原理

对于两个二进制数 x 和 y,用“x-y”表示他们的二进制差,其结果有如下四种情形:

(1)0-0=0;(2)1-0=1;(3)1-1=0;(4)10-1=1。

对于上述四种情形中的 “10-1=1”的特殊情形,也即是当 x=10(即十进制的 2),y=1 时,它们的二进制差为 1,这表明在二进制减法中,作差过程存在向前一位借位的情形。

串行进位减法器电路

一个 n 位串行进位减法器是由 n 个全减器的借位位首尾相连、依次串联在一起形成的,在串行进位减法器中,其借位从最低有效位( Least Significant Bit,LSB)传到其最高有效位(Most Significant Bit,MSB)需要很长的的时间(电路的延时)。

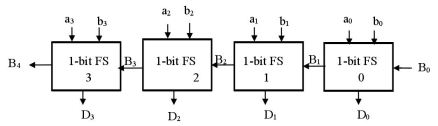

图1 四位串行进位减法器逻辑电路图

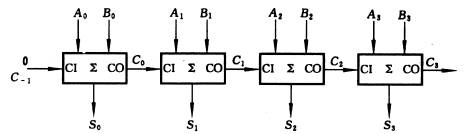

图2 四位串行进位减法器的符号

图1、图2分别是一个四位的串行进位减法器逻辑电路图和符号,其中 a i 、bi和 Bi是输入位,D i 、Bi+1是输出位,且 Bi+1作为更高位的输入位。

串行进位减法器电路的主要优点是:结构简单、便于连接和 IC 版图设计的实现;但其缺点是:执行运算速度较慢。这是因为串行进位减法器电路每一位的相减必须等到它前一位的计算结果,最高位相减必须要等到它前面的所有位都完成相减才能进行。

由于全减器只有在它的输入位有效时它的输出结果才是有效的,最左端的电路是最后响应的,这样全减器的输出结果才是正确的。

因此,串行进位减法器电路总的延时取决于每一个全减器电路的信号传输延时,而信号的传输延时又与逻辑门的工艺有关,所以串行进位减法器电路的时间延时和电路中逻辑门的工艺相关。

-

逻辑电路

+关注

关注

13文章

494浏览量

42626 -

二进制

+关注

关注

2文章

795浏览量

41653 -

减法器

+关注

关注

1文章

26浏览量

16845 -

全减器

+关注

关注

0文章

4浏览量

4866

发布评论请先 登录

相关推荐

串行进位减法器电路设计

串行进位减法器电路设计

评论