有群友提问,下面的代码为什么在DC里可以综合成DFF,而在FPGA上却综合成了latch。

always@(posedgeclk,negedgerstn,negedgesetn) if(!rstn) a <= 1'b0; else if(!setn) a <= 1'b1; else a <= a;

我们可以看到这段代码有两个特别之处:

同时有异步复位和异步置位

除了复位和置位,数据要保持

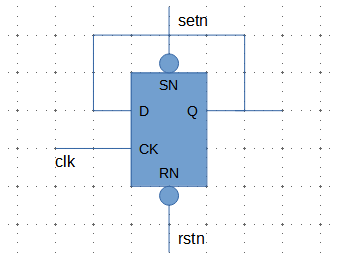

我们可以画出这段代码的逻辑图,如下图。这图也就是DC综合出来的结果。

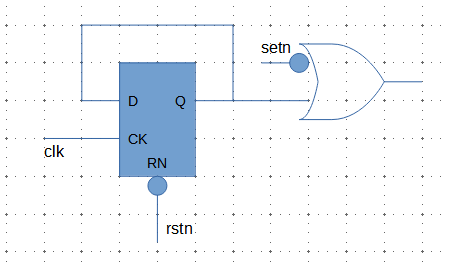

那在FPGA上为什么会变成latch呢?有人说FPGA平台没有latch,但quartus里确实报了生成latch的warning。我们来试着把电路等价变换,先把setn端简化掉:

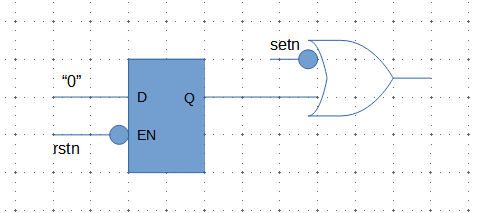

我们看到上图左边dff的逻辑,当rstn==0时,dff输出0,否则就保持。这不就是latch的逻辑吗?整理出下图:

由此可见FPGA平台综合成latch也是有可能的。

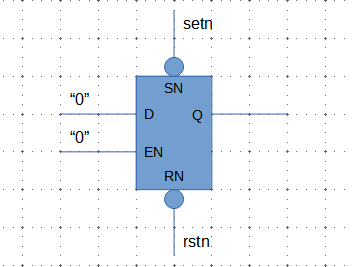

后来让群友直接看看FPGA平台综合出来的电路图,看看究竟是什么样的电路。群友回复如下:

哎,真是神奇!时钟都优化没了,直接用了一个带复位和置位的latch。看了这个电路的逻辑,确实与一开头的RTL等价的,并且还不需要数据loop了,挺简洁的。

所以得出结论,FPGA平台之所以与DC有差异,只是综合策略或者说是综合引擎优化算法的问题。综合结果都是可以用的。

审核编辑:刘清

-

FPGA

+关注

关注

1630文章

21796浏览量

605620 -

时序电路

+关注

关注

1文章

114浏览量

21738 -

异步复位

+关注

关注

0文章

47浏览量

13338 -

dff

+关注

关注

0文章

26浏览量

3442

原文标题:时序电路为什么综合成了latch

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA的设计主要是以时序电路为主吗?

组合电路和时序电路的讲解

什么是时序电路?

什么是同步时序电路和异步时序电路,同步和异步电路的区别?

时序电路为什么在FPGA上综合成了latch?

时序电路为什么在FPGA上综合成了latch?

评论