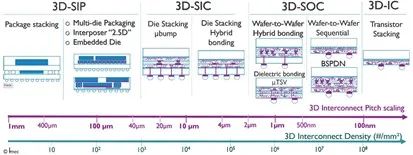

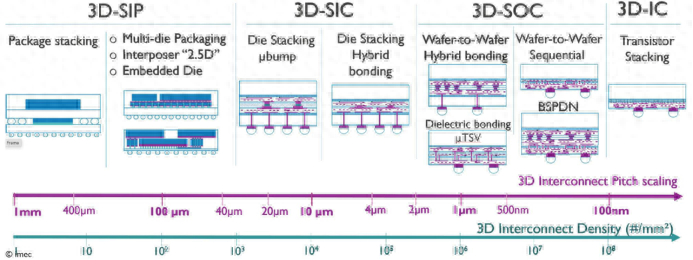

3D集成是实现多芯片异构集成解决方案的关键技术,是业界对系统级更高功耗、性能、面积和成本收益需求的回应。3D 堆叠正在电子系统层次结构的不同级别(从封装级到晶体管级)引入。因此,多年来已经开发出多种 3D 互连技术,涵盖各种互连间距(从毫米到小于 100 纳米)并满足不同的应用需求。这种“3D 互连景观”如下图所示。形势是高度动态的,每种技术都会及时扩展到更小的互连间距。

在该技术“谱系”接近尾声时,我们发现了晶圆间混合键合,有望实现高互连密度和小互连寄生效应。这种“混合”铜对铜和电介质对电介质键合技术使用铜镶嵌技术来定义键合表面,可能允许非常精细的间距缩放。

直到最近,晶圆间混合键合的大批量制造主要局限于信号处理电路层上的堆叠图像传感器领域。最近,该技术被用于在 3D NAND 层之上集成 CMOS 外围电路。这些商业应用利用了该技术每平方毫米集成一百万个互连的能力,这是通过约 1μm 的紧密铜互连间距实现的。该技术的另一个优点是能够“混合搭配”不同的材料和功能以及不同代的 CMOS 技术。

在未来的几年里,我们预计应用领域将显着扩大。借助系统技术协同优化 ( STCO ),电路分区将发生在设计层次结构的更低级别 - 考虑电路块甚至标准单元。我们看到了逻辑存储器应用的首次发布——例如逻辑之上的 SRAM——这一直是开发先进晶圆到晶圆混合键合技术的主要驱动力之一。

为了在这些情况下充分发挥晶圆间混合键合的潜力,研究人员必须成功地将互连间距缩小到远低于 1μm。

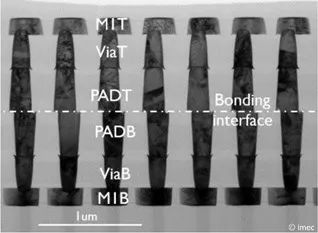

当今的晶圆到晶圆混合键合工艺流程从两个经过完全处理的 300mm 晶圆开始,具有完整的前端生产线 (FEOL) 和后端生产线 (BEOL)。该流程的第一部分类似于片上BEOL 镶嵌工艺,其中在键合电介质中蚀刻出小空腔 - 主要使用SiO₂。空腔填充有阻挡金属、晶种和铜。

接下来是化学机械抛光 ( CMP ) 步骤,该步骤针对晶圆间的高均匀性进行了优化,以产生极其平坦的电介质表面,同时为铜焊盘实现几纳米的凹槽。精确对准后,通过使晶圆在晶圆中心接触,在室温下进行两个晶圆的实际接合。抛光的晶圆表面粘附会产生强大的晶圆间吸引力,从而产生键合波,从而封闭从中心到边缘的晶圆间间隙。在该室温键合步骤之后,晶片在更高的温度下退火以获得永久的电介质-电介质和铜-铜键合。

随着应用领域的扩展,更先进的混合键合实现不断涌现。如前所述,目前的趋势是使键合工艺越来越靠近前端,以实现逻辑叠逻辑或存储器逻辑叠层等功能。这不仅需要更精细的互连间距,而且还需要在键合步骤之后进行更多的后处理。

一个非常具体的例子是背面供电网络 (BSPDN),其中晶圆间键合是关键步骤。在 BSPDN 处理中,第一个晶圆的正面被键合到载体晶圆上。然后减薄第一片晶圆的背面,并通过 n-TSV 图案化、金属填充和背面金属化完成该工艺。在此示例中,BEOL 处理的一部分(即集成用于电力传输的“最宽”互连线)是在晶圆键合工艺之后执行的。

这些应用提出了更严格的扩展需求,对当前的工艺流程提出了挑战。主要缺陷涉及铜对铜的对准精度、键合前的晶圆纯度和拓扑结构,以及小互连间距下电介质和铜焊盘的键合强度。

在 2023 年 IEEE 国际电子设备会议 (IEDM 2023) 上,imec 报告了一些重要创新,这些创新为前所未有的400nm 互连间距铺平了道路。这项工作是一项综合研究的结果,该研究检查了晶圆间混合键合的各个方面。

01设计改进以补偿缩放和对齐限制

Imec研究人员首次提出了一种采用六边形网格和圆形铜垫的 test vehicle design ,而不是传统的方形网格和方形或圆形垫设计。新设计具有多项优点。它允许铜焊盘以尽可能最密集的方式封装,所有相邻焊盘之间的距离相等。因此,随着进一步缩放,这种配置使得更容易控制铜焊盘密度,同时最大化铜焊盘尺寸和间距。该团队还在研究使用相等或不相等焊盘设计的影响。在后一种情况下,顶部晶圆的临界铜焊盘尺寸设计得比底部晶圆更小。不等焊盘设计具有一些优点,包括更显着的键合重叠公差、更低的寄生电容以及在小互连间距下更高的介电击穿强度。

02表面形貌的精确控制

在两个晶圆键合之前,两个晶圆的表面必须极其平坦和清洁,以实现可靠的混合键合工艺。因此,CMP 是一个要求非常高的工艺步骤。它还确保了铜焊盘的均匀 凹进,这意味着铜在键合之前保留在介电表面下方几纳米处。这是在退火后获得无空隙接合所必需的。通过在布局设计中将先进的 CMP 工艺与虚拟焊盘相结合,研究人员成功地精确控制了整个晶圆上的铜焊盘高度和表面拓扑。

03SiCN 电介质具有更好的粘合强度和可扩展性

imec 此前提出SiCN 作为小互连间距的首选电介质。与SiO₂表面相比,SiCN 表面表现出更高的键合能,这意味着需要更多的能量来破坏键合。此外,SiCN 还可作为 Cu 和晶圆钝化层的扩散阻挡层,阻止气体扩散,从而形成热稳定性更高的键合界面。当缩小混合键合互连间距时,这些特性变得越来越重要。基于纳米压痕(一种评估结合强度的新兴技术)的测量证实,SiCN-SiCN 结合强度显着优于 SiO₂-SiO₂结合强度。只需 250°C 的键合后退火即可获得高键合强度,并且在更高温度下不会降低。

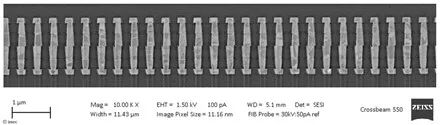

上述见解用于执行先进的晶圆到晶圆 Cu/SiCN 键合工艺。实际的键合是使用配备先进对准功能的商业高质量晶圆键合机进行的,这是该工艺成功的关键工具。300 毫米晶圆成功键合,产生了前所未有的400 纳米间距的铜互连线。

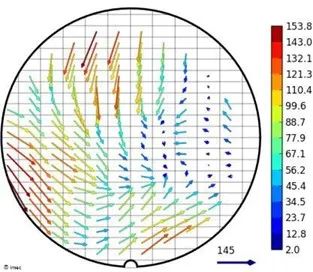

结果表明,成功控制了 Cu/SiCN 表面形貌、精确对准(导致覆盖层厚度低于 150nm)以及良好的电气性能(即低单接触电阻)。

该团队还首次研究了键合覆盖层与可靠性(即介电击穿和良率)之间的关系。结果证实,在小互连间距下,不均匀设计的铜焊盘比相同的焊盘具有更高的介电击穿强度。该团队还得出结论,对于这些 400nm 互连间距,覆盖层控制需要小于 100nm,才能在大批量制造中获得足够的良率。因此,满足未来3D-SOC设计的需求对下一代晶圆键合设备的叠合精度提出了严格的要求。

晶圆间混合键合已成为一种很有前景的 3D 集成技术,可实现不断增加的 I/O 密度以及功能芯片之间更高效的连接。为了实现逻辑存储器等应用(其中晶圆间键合发生在靠近前端的位置),必须将铜互连间距的缩放推至其最终极限。网格设计的改进、表面形貌的增强控制、SiCN作为电介质的使用、对键合机制的基本理解以及改进的覆盖控制被认为是在400nm(及以下)实现电气功能和可靠的Cu互连的关键推动因素。这些结果为开发未来具有更小互连间距的晶圆间键合工艺奠定了基础。

转载:半导体行业观察

审核编辑:汤梓红

-

芯片

+关注

关注

455文章

50732浏览量

423270 -

晶圆

+关注

关注

52文章

4895浏览量

127939 -

键合

+关注

关注

0文章

60浏览量

7865

原文标题:混合键合,重要突破

文章出处:【微信号:芯长征科技,微信公众号:芯长征科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

晶圆到晶圆混合键合的前景和工艺流程

晶圆到晶圆混合键合的前景和工艺流程

评论