CMOS(Complementary Metal-Oxide-Semiconductor)电路是一种常见的电子逻辑门电路技术,由一个PMOS(P型金属氧化物半导体)和一个NMOS(N型金属氧化物半导体)管道组成。在CMOS电路中,输入信号的高和低电平取决于输入信号的电压和电路中的配置。

对于CMOS门电路来说,判断输出电平的关键是输入电压。在理想的情况下,当输入电压为高电平时,输出为低电平;当输入电压为低电平时,输出电平为高电平。这是因为CMOS电路的输入管道是一个开关,当输入电压为高电平时,考虑到电平的传输,输出电压为低电平;当输入电压为低电平时,输出电压为高电平。

然而,在实际的CMOS电路中,存在微小的漏电流。当输入电压为高电平时,漏电流逐渐增加,使得输出电压变大。相反,当输入电压为低电平时,漏电流逐渐减小,导致输出电压变小。因此,判断输出电平时应该考虑输入电压和漏电流之间的关系。

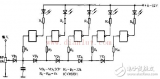

为了更好地理解CMOS门电路的输入和输出电平关系,我们可以具体分析不同类型的CMOS门电路,如与门(AND)、或门(OR)和非门(NOT)。在这里,我们将以与门为例进行讨论。

与门是一种基本的布尔逻辑门电路,有两个输入和一个输出。当且仅当所有输入都为高电平时,输出为高电平。对于CMOS与门电路,输入电压为低电平(0V)表示逻辑“0”,输入电压为高电平(VDD)表示逻辑“1”。当两个输入都为高电平时,输出为高电平;否则,输出为低电平。

具体地说,当一个输入为高电平时,该输入管道将打开,流经漏电流,导致输出电压稍微上升,但仍然为低电平。当两个输入都为高电平时,两个输入管道都打开,漏电流增加,使得输出电压显著上升,接近高电平。因此,输出电平为高电平,表示所有输入都为高电平。

当任何一个输入为低电平时(逻辑“0”),相应的输入管道关闭,不会存在漏电流,输出电压保持为低电平。只有当两个输入都为高电平时,输出电平才为高电平。

需要注意的是,CMOS门电路的输出电平受到供电电压的影响。通常情况下,供电电压VDD为高电平,对于大多数应用而言,VDD为正常操作电压的一半。更高的供电电压意味着更高的输出电平。

综上所述,CMOS门电路的输入和输出电平关系由输入信号的电压和漏电流之间的相互作用确定。当输入电压为高电平时,输出电平通常是低电平,但存在微小的漏电流增加输出电平。当输入电压为低电平时,输出电平通常是高电平,但漏电流较小导致输出电平略微降低。根据不同类型的CMOS门电路,如与门、或门和非门,我们可以确定输出电平取决于输入电平的组合方式。当输入组合满足门电路的逻辑关系时,输出电平为高电平;否则,输出电平为低电平。

-

门电路

+关注

关注

7文章

199浏览量

40123 -

CMOS电路

+关注

关注

0文章

49浏览量

11496 -

漏电流

+关注

关注

0文章

260浏览量

16992 -

高电平

+关注

关注

6文章

146浏览量

21326

发布评论请先 登录

相关推荐

转载-------TTL和CMOS门电路的区别

CMOS电平转换电路详解

CMOS电路什么输入为高电平 cmos门电路输出电平判断

CMOS电路什么输入为高电平 cmos门电路输出电平判断

评论