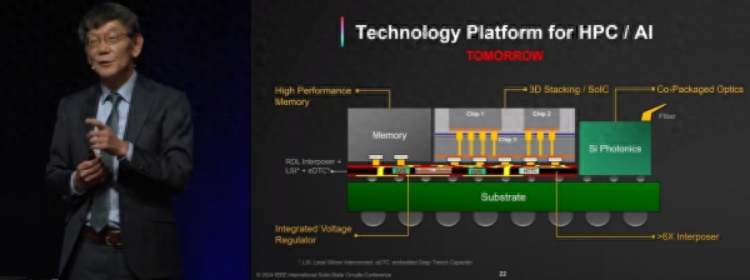

近期,台积电将其高性能计算与 AI 芯片封装技术亮相于国际固态电路大会(简称 ISSCC 2024),据悉,此技术有望将芯片晶体管数目由现有的1000亿级跃升至1万亿级。

台积电高级研发副总裁张晓强指出,本项新技术主要针对AI芯片性能增强。新型HBM高带宽存储器与Chiplet架构小芯片的引入需求大量组件及IC基板,由此引发的连通性及能源消耗等问题难免产生。他特别强调,借助硅光科技与光纤替代传统I/O电路,实现高效率的数据传输;此外,通过异质芯片堆叠和混合键合,最大限度优化I/O。值得注意的是,这项封装技术将运用集成稳压器应对供电问题,但具体商用时间尚未透露。

台积电透露,当前全球前沿芯片最多可容纳1000亿晶体管,然而新的封装平台能使之增加到1万亿级别。尽管该封装内将搭载集成稳压器解决供电问题,但未来商业化仍待进一步确认。此外,张晓强还暗示台积电的3nm制程技术很可能迅速应用于汽车领域。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

存储器

+关注

关注

38文章

7538浏览量

164586 -

AI芯片

+关注

关注

17文章

1918浏览量

35303 -

chiplet

+关注

关注

6文章

437浏览量

12650

发布评论请先 登录

相关推荐

台积电超大版CoWoS封装技术:重塑高性能计算与AI芯片架构

一、技术前沿探索:从微小到宏大的CoWoS封装技术演进 在半导体技术的浩瀚星空中,每一次技术的革新都如同星辰般璀璨夺目。去年台积电在欧洲开放创新平台

台积电分享 2nm 工艺深入细节:功耗降低 35% 或性能提升15%!

下),同时其晶体管密度是上一代3nm制程的1.15倍。这些显著优势主要得益于台积电的全栅极(Gate-All-Around, GAA)纳米片

台积电推出“超大版”CoWoS封装,达9个掩模尺寸

圆上芯片)封装技术,该技术将提供高达9个掩模尺寸的中介层尺寸和12个HBM4内存堆栈。新的封装方法将解决性能要求最高的应用,并让AI(人工智

台积电CoWoS产能将提升4倍

在近日于台湾举行的SEMICON Taiwan 2024国际半导体展会上,台积电展示了其在先进封装技术领域的雄心壮志。据

台积电加速扩产CoWoS,云林县成新封装厂选址

台积电,作为全球领先的半导体制造巨头,正加速推进其CoWoS(Chip On Wafer On Substrate)封装技术的产能扩张计划。据最新消息,

台积电跨制程整合晶体管架构并引入CFET,发布新一代芯片技术

张晓强强调,半导体产业的黄金时代已然来临,未来AI芯片的发展几乎99%都依赖于台积电的先进逻辑技术和先进

台积电总裁缺席技术论坛,看好AI和高性能计算前景

台积电2024年技术论坛于5月23日在中国台湾举行,但由于总裁魏哲家缺席,由亚太业务处长万睿洋代为发言。他表示,人工智能(AI)正引领第四次

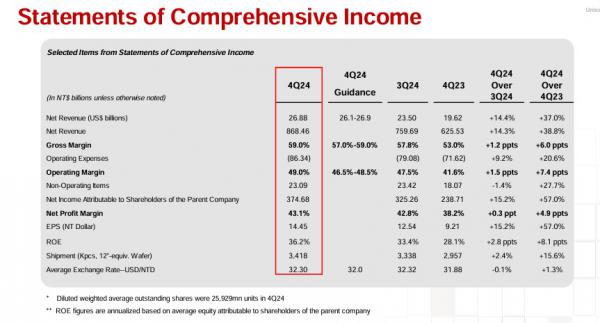

台积电运营挑战最强第2季 高性能计算、 AI应用订单强劲

市场信心满满,预计得益于高性能计算和人工智能应用订单的强劲表现,台积电本季度的美元营收有望超越

世界第一AI芯片发布!世界纪录直接翻倍 晶体管达4万亿个

和相同的价格下,WSE-3的性能是之前的世界记录保持者Cerebras WSE-2的两倍。 该公司称,WSE-3芯片是专为训练业界最大的AI模型而构建的,台

台积电创新推出万亿晶体管封装平台,专注于高性能计算和AI芯片应用

台积电创新推出万亿晶体管封装平台,专注于高性能计算和AI芯片应用

评论