在Verilog中,Function和Task是用于模块化设计和重用代码的两种重要元素。它们允许开发人员将复杂的操作分解为更小的功能单元,并在需要时调用它们。虽然Function和Task在某些方面非常相似,但它们在功能和使用方式上有一些重要的区别。

- 定义和声明方式不同:

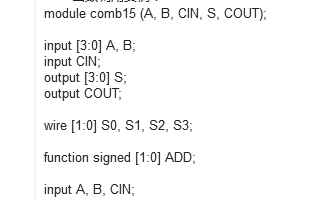

- Function:使用关键字"function"来定义和声明。函数可以有一个或多个输入参数,可以有一个返回值。函数必须在声明之后直接定义,不能在其他函数或任务内部定义。

- Task:使用关键字"task"来定义和声明。任务可以有一个或多个输入参数,没有返回值。与函数不同,任务可以在模块的任何位置定义,也可以在其他函数或任务内部定义。

- 数据类型的使用:

- Function:函数可以接受和返回任何Verilog支持的数据类型。这些数据类型包括整数、浮点数、布尔值和自定义数据类型。函数可以将参数传递给其他函数或任务,并且可以在函数内部使用本地变量。

- Task:任务可以接受和返回任何Verilog支持的数据类型。任务也可以将参数传递给其他函数或任务。但是任务无法在内部定义本地变量。

- 返回值的处理方式不同:

- Function:函数必须通过"return"关键字返回一个值。函数的返回值可以直接赋值给其他变量,或者作为表达式的一部分使用。函数可以有多个返回语句,但只有在第一个返回语句时,函数的执行流程会跳到调用函数的位置。

- Task:任务没有返回值,不需要"return"关键字。任务的执行流程会一直持续到最后一个语句执行完成,然后返回到调用任务的位置。

- 函数和任务的调用方式不同:

- Function:函数可以在任何地方被调用,包括组合逻辑和时序逻辑。函数可以在赋值语句、条件语句和循环语句中使用。函数的返回值可以直接赋值给变量,或者作为其他表达式的一部分使用。

- Task:任务只能在时序逻辑中被调用。任务的调用通常发生在"always"块或"initial"块内。在任务的调用语句后,任务中的所有语句会按照顺序执行。任务不能在赋值语句等其他地方被使用。

- 并行和顺序执行:

- Function:由于函数可以在任何位置被调用,它在代码中可以并行执行。函数内的语句会根据调用顺序依次执行,但在特定调用之间不会相互影响。

- Task:任务的语句按照顺序执行。任务内的语句在调用任务时按照定义的顺序被执行,并且不会并行执行。任务中的语句可以定义为组合逻辑或时序逻辑。

- 用途和场景不同:

- Function:函数主要用于进行计算、逻辑运算或数据处理。它们可以在Verilog模块中广泛使用,用于数值分析、数据转换、状态机控制等。

- Task:任务主要用于表示基本的行为或操作,例如时钟信号的生成、触发事件、输出操作等。它们通常用于时序逻辑中,用于描述模块的行为和操作。

总结起来,Function和Task在Verilog中具有不同的定义和声明方式、数据类型的使用、返回值的处理方式、调用方式、并行与顺序执行以及用途和场景。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Verilog

+关注

关注

28文章

1355浏览量

110584 -

Function

+关注

关注

0文章

14浏览量

9953 -

函数

+关注

关注

3文章

4350浏览量

63106 -

模块化

+关注

关注

0文章

334浏览量

21481

发布评论请先 登录

相关推荐

转载---verilog中task和function的区别

;另外,function定义中声明的所有局部变量寄存器都是静态的,即function中的局部寄存器在function的多个调用之间保持他们的

发表于 03-13 21:53

炼狱传奇-task_function之战

1. task(任务)与function(函数)的不同任务与函数主要有以下四点不同:l函数只能与主模块共用一个仿真时间单位,而任务定义自己的仿真时间单位。l函数不能启动任务,任务可以启动其他任务

发表于 05-13 11:19

Verilog函数中function里的过程语句该怎么写

Verilog用函数方式描述一个4选1选择器,function里的过程语句该怎么写啊我这么写报错:functions can't contain non-blocking

发表于 04-17 06:35

Verilog的task和function说明语句

如果传给任务的变量值和任务完成后接收结果的变量已定义, 就可以用一条语句启动任务。任务完成以后控制就传回启动过程。如任务内部有定时控制, 则启动的时回可以与控制返回的时

发表于 01-05 15:50

•13次下载

简谈FPGA verilog中的task用法

大家好,又到了每日学习的时间了,今天我们来聊一聊FPGA verilog中的task用法。 任务就是一段封装在“task-endtask”之间的程序。任务

简谈FPGA verilog中的function用法与例子

大家好,又到了每日学习的时间了,今天我们来聊一聊FPGA verilog中的function用法与例子。 函数的功能和任务的功能类似,但二者还存在很大的不同。在 Verilog HDL

Verilog设计过程中的一些经验与知识点

“ 本文主要分享了在Verilog设计过程中一些经验与知识点,主要包括块语句、阻塞赋值和非阻塞赋值 以及结构说明语句(initial, always, task, function)。”

verilog中的task用法

任务就是一段封装在“task-endtask”之间的程序。任务是通过调用来执行的,而且只有在调用时才执行,如果定义了任务,但是在整个过程中都没有调用它,那么这个任务是不会执行的。调用某个任务时可能

在Verilog中利用函数将重复性的行为级设计进行提取

在 Verilog 中,可以利用任务(关键字为 task)或函数(关键字为 function),将重复性的行为级设计进行提取,并在多个地方调用,来避免重复代码的多次编写,使代码更加的简

verilog同步和异步的区别 verilog阻塞赋值和非阻塞赋值的区别

Verilog中同步和异步的区别,以及阻塞赋值和非阻塞赋值的区别。 一、Verilog中同步和异

verilog function函数的用法

Verilog 是一种硬件描述语言 (HDL),主要用于描述数字电子电路的行为和结构。在 Verilog 中,函数 (Function) 是一种用于执行特定任务并返回一个值的可重用代码

verilog task和function区别

verilog中的task和function都是用于实现模块中的可重复的功能,并且可以接收参数和返回结果。但是它们在编写和使用上有一些

verilog中initial和always的区别

Verilog是一种硬件描述语言(HDL),用于设计和模拟数字电路。在Verilog中,关键字initial和always都是用于描述电路行为的特殊语句。它们被用来生成仿真模型,并控制模拟器的启动

verilog中function和task的区别

verilog中function和task的区别

评论