verilog中的task和function都是用于实现模块中的可重复的功能,并且可以接收参数和返回结果。但是它们在编写和使用上有一些区别。下面将详细介绍task和function的区别。

- 语法结构:

task和function都可以具有输入参数列表,用于接收外部传递的参数。但是task可以没有返回值,而function必须有返回值并且要明确指定返回的数据类型。

- 用途:

- task主要用于执行一系列的操作或任务,它可以包含多个语句,可以有输入参数,但是没有返回值。task通常用于一组连续的语句块,用于组织和封装一系列的操作。例如,在时序逻辑中,可以使用task来实现状态转换。

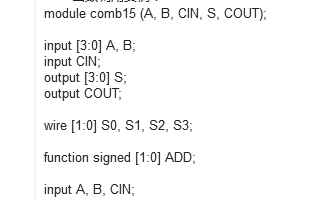

- function主要用于执行特定的计算或运算,并返回一个结果。function可以包含多个语句,也可以有输入参数。function通常用于将一组操作封装成一个函数,可以通过调用函数获得运算结果。例如,在组合逻辑中,可以使用function来实现一些计算和逻辑运算。

- 调用方式:

- task通过调用task名称来执行,可以在任何地方使用task进行调用,并可以在调用处返回一个任务。

- function通过调用function名称来执行,可以将函数的返回值赋值给一个变量,或者直接使用函数的返回值,用于其他计算和运算。

- 变量声明:

- task中声明的变量作用域范围为整个模块,所有的任务都可以访问这些变量。

- function中声明的变量作用域范围为函数体内,即只能在函数内部访问这些变量。

- 并发控制:

- task可以被多个模块同时调用,可以并发执行,但是task内部的语句是按照顺序执行的。

- function只能在一个模块内被调用,并且在同一时间只能被一个模块调用。

- 时间控制:

- task中可以使用

#和wait语句来实现时间控制和延迟。 - function中不允许使用

#和wait语句,因为function本身的目的是进行计算和运算,而不是进行延迟控制。

综上所述,task和function在用途、语法结构、调用方式、变量作用域、并发控制和时间控制方面都有一定的区别。根据实际需求选择使用task或function,能更好地实现所需的功能。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

模块

+关注

关注

7文章

2695浏览量

47431 -

Verilog

+关注

关注

28文章

1351浏览量

110074 -

参数

+关注

关注

11文章

1829浏览量

32195 -

Function

+关注

关注

0文章

14浏览量

9907 -

函数

+关注

关注

3文章

4327浏览量

62571

发布评论请先 登录

相关推荐

转载---verilog中task和function的区别

本帖最后由 hxing 于 2014-3-13 22:25 编辑

task--- 任务function --- 函数任务可以有input、output和inout,数量不限;函数只有input

发表于 03-13 21:53

verilog HDL学习笔记

Verilog起源于C语言,但有很多不同于C语言之处。下面就列举一下任务和函数的关系。任务:task 任务名端口及数据类型声明;其他语句; endtask函数:function 返回值位宽及类型说明

发表于 10-01 13:57

炼狱传奇-task_function之战

1. task(任务)与function(函数)的不同任务与函数主要有以下四点不同:l函数只能与主模块共用一个仿真时间单位,而任务定义自己的仿真时间单位。l函数不能启动任务,任务可以启动其他任务

发表于 05-13 11:19

Verilog函数中function里的过程语句该怎么写

Verilog用函数方式描述一个4选1选择器,function里的过程语句该怎么写啊我这么写报错:functions can't contain non-blocking

发表于 04-17 06:35

Verilog的task和function说明语句

如果传给任务的变量值和任务完成后接收结果的变量已定义, 就可以用一条语句启动任务。任务完成以后控制就传回启动过程。如任务内部有定时控制, 则启动的时回可以与控制返回的时

发表于 01-05 15:50

•13次下载

简谈FPGA verilog中的task用法

大家好,又到了每日学习的时间了,今天我们来聊一聊FPGA verilog中的task用法。 任务就是一段封装在“task-endtask”之间的程序。任务是通过调用

简谈FPGA verilog中的function用法与例子

大家好,又到了每日学习的时间了,今天我们来聊一聊FPGA verilog中的function用法与例子。 函数的功能和任务的功能类似,但二者还存在很大的不同。在 Verilog HDL 语法中也存在

Verilog设计过程中的一些经验与知识点

“ 本文主要分享了在Verilog设计过程中一些经验与知识点,主要包括块语句、阻塞赋值和非阻塞赋值 以及结构说明语句(initial, always, task, function)。”

verilog中的task用法

任务就是一段封装在“task-endtask”之间的程序。任务是通过调用来执行的,而且只有在调用时才执行,如果定义了任务,但是在整个过程中都没有调用它,那么这个任务是不会执行的。调用某个任务时可能

function与invoke的区别

std::function和std::invoke是两个不同的东西,功能也不同。std::function 是一个函数对象的封装器,可以用来封装任意类型的可调用对象,比如函数指针、lambda表达式等

verilog同步和异步的区别 verilog阻塞赋值和非阻塞赋值的区别

Verilog中同步和异步的区别,以及阻塞赋值和非阻塞赋值的区别。 一、Verilog中同步和异步的区别 同步传输和异步传输是指数据在电路中

verilog中function和task的区别

在Verilog中,Function和Task是用于模块化设计和重用代码的两种重要元素。它们允许开发人员将复杂的操作分解为更小的功能单元,并在需要时调用它们。虽然Function和

verilog function函数的用法

Verilog 是一种硬件描述语言 (HDL),主要用于描述数字电子电路的行为和结构。在 Verilog 中,函数 (Function) 是一种用于执行特定任务并返回一个值的可重用代码块。函数在

verilog task和function区别

verilog task和function区别

评论