共读好书

刘文喆 陈道远 黄炜

摘要:

塑封器件具有体积小、成本低的优点,逐步替代气密性封装器件,广泛地应用于我国军用产品中。军用塑封SIP(System In Package)产品集成度高、结构复杂、可靠性要求高等特点,对塑封工艺带来了挑战,目前国内工业级塑封产品不能完全满足军用可靠性要求,工业级塑封产品常在严酷的环境应力试验下表现出失效。本文针对工业级塑封 SIP 器件在可靠性试验过程中出现的失效现象进行分析研究,通过超声检测、芯片切面分析等手段,结合产品应力试验结果,分析导致塑封产品失效的关键原因,并针对失效机理提出优化改进方案。

引言

塑封器件具有体积小,重量轻,成本低,电性能指标优良等优点,在军用电子元器件领域应用日益广泛[1] 。

塑封器件分层是其典型的故障模式,封装材料热膨胀系数的不同以及被粘接材料表面能低,是造成塑封电路分层的内部原因。在塑封器件失效案例中因塑封分层导致的失效是比较隐蔽、不易被发现的,但其对塑封器件长期可靠性带来了较大隐患,例如塑封器件分层后水汽进入内部,对芯片的铝电极产生腐蚀,导致电极开路失效。

本文选取一款复杂结构塑封 SIP(System In Pack-age)产品,其较常规塑封单片电路结构更为复杂,内部器件类型多样、器件尺寸及高度不一致等因素对其塑封工艺带来极大挑战。本文采用多样品多应力条件试验验证的方式,分析影响塑封 SIP 继承模块封装可靠性的关键环境因素,通过对环境进行特殊的控制和工艺优化可以解决塑封分层问题,为塑封器件的可靠应用提供有效支撑。

1 产品简介

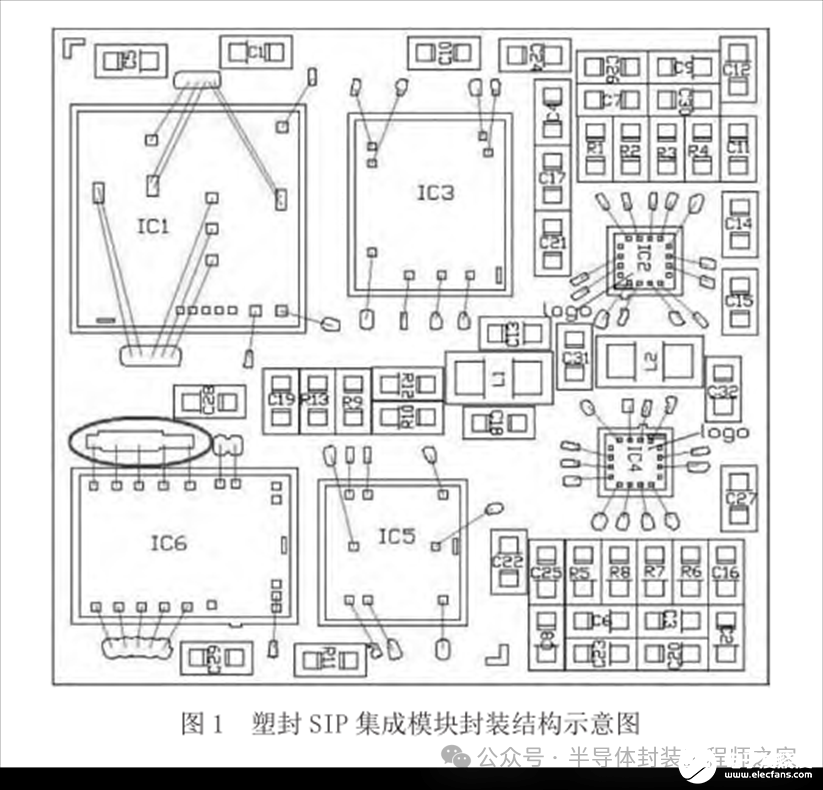

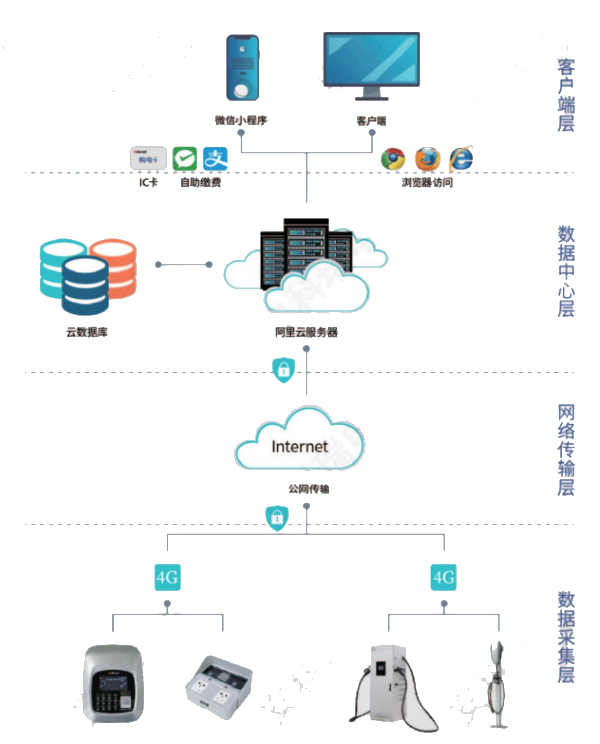

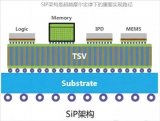

该款塑封 SIP 集成模块由 6 款芯片、3 款无源器件和有机基板组成,无源器件包括电阻、电容和磁珠,采用塑封工艺进行封装。其封装结构图如图 1 所示。

为达到军用塑封产品可靠性指标,该款塑封 SIP 集成模块产品需经历的可靠性环境试验包括温度循环、预处理(烘焙、湿浸、回流焊、清洗、烘干等)、高温贮存、强加速稳态湿热(H AST)。

2 失效原因分析

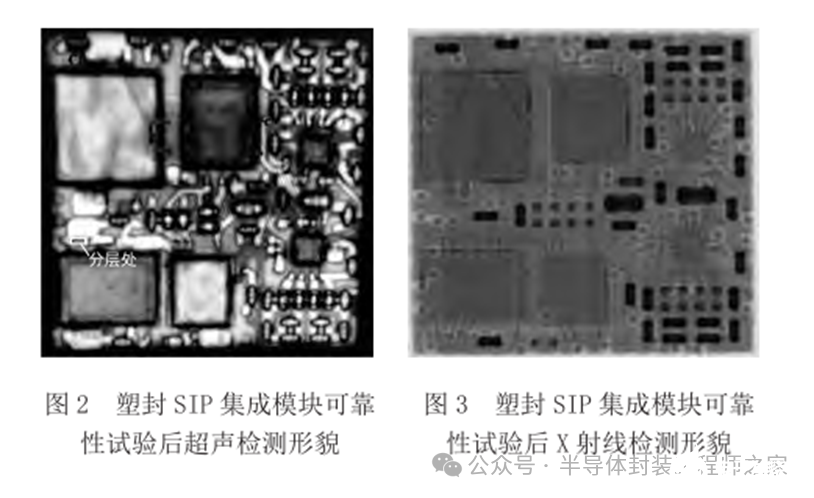

该产品经历烘焙(125 ℃,24 h)、湿浸(60 ℃,60 % RH ,40 h)、回流焊(3次)、温度循环(-40 ℃/60 ℃,5 次)并常温烘干后,分两组分别进行温度循环(-55 ℃ /150 ℃,100 次)、强加速稳态湿热(H A ST)(130 ℃ /85 % RH ,96 h)试验,试验后采用超声检测方法检测塑封结构变化情况。检测结果显示所有试验样品均出现塑封分层现象,分层区域为 IC6 键合焊盘处,如图 1、2 标记处所示。

对故障件进行 X 射线检测,未发现明显异常,形貌如图 3 所示。因此,采用破坏性切片分析的手段,对超声检测不合格区域进行定位,切片形貌可明显观察到基板上键合焊盘处与塑封料间存在分层,分层程度轻微,高度在 1 μm 以内,形貌如图 4 所示。

试验过程中产品经历一定的温度、湿度影响,为评估影响塑封器件分层的关键因素,对该款塑封 SIP 集成模块结构设计、封装工艺、经历应力条件进行分析排查。

2.1 结构设计

该款塑封 SIP 集成模块外形尺寸为 10 m m ×10 m m×1.8 m m ,选用QFN48塑封封装实现,采用6层有机基板,芯片与基板的互联采用 25 μm 金丝球焊,实现内部各个器件的连接和信号扇出。

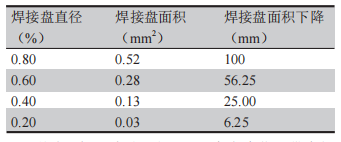

分层处焊盘上 5 个键合点属于同一电源网络,焊盘设计时按照区域方式设计,区域宽度为 1.5 m m *0.2 m m ,如图 1 标记处所示,为该模块中面积最大的焊盘。该区域焊盘塑封料与键合区域间的接触面较大,焊盘接触面材料为 Au 较为光滑,易形成空洞,与塑封料间附着力减小,引起接触面塑封分层,且金属与塑封料之间的界面面积越大,分层的可能性越大。

该款结构设计焊盘面积偏大,与塑封料界面处存在一定分层的风险。

2.2 封装工艺

该款塑封 SIP 集成模块选用 SUM ITOM O G760L 塑封料进行封装,该塑封料为行业内主流材料。基板选用M GC 材料基板,该基板材料成熟,为通用大批量基板材料。

在材料选型及封装过程控制上不存在风险。

2.3 应力条件分析

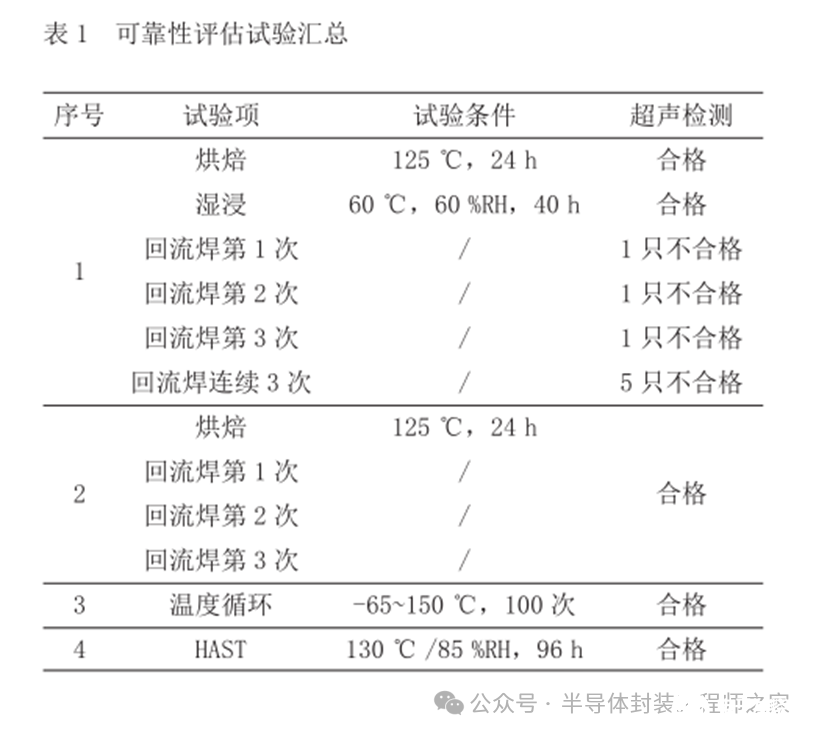

为判断预处理中湿浸试验(湿度应力)、回流焊试验(温度应力)、温度循环(温度应力)、强加速稳态湿热(温湿度应力) [2] 分别对该款塑封 SIP 集成模块超声检测分层的影响,选取合格样品,分组进行可靠性评估试验,每分组 5 只样品,试验条件及结果如表 1所示。

上述试验结果显示,第2分组试验条件不进行湿浸,烘焙后直接投入回流焊,随后进行超声检测,检测结果显示超声无分层情况,表明分层主要受湿浸试验影响,塑封材料吸附了水汽,在回流焊过程中受高温影响,水汽加速释放,导致塑封料与金属接触面分层。

3 失效机理分析

塑封器件是以树脂类聚合物为材料封装的器件,由于塑封料与焊盘及基板材料的热膨胀系数不完全一致,热应力作用下塑封器件内不同材料的连接处会产生应力集中,应力水平超过其中任何一种封装材料的屈服强度或断裂强度导致器件分层;同时,树脂类材料本身并非致密具有吸附水汽的特性,封装体与引线框架的粘接界面等处也会引入湿气进入塑封器件,塑封器件中水汽含量过高时会引起塑封料与基板界面上的树脂离解,即温度、湿度应力会导致塑封器件分层。

4 纠正措施建议

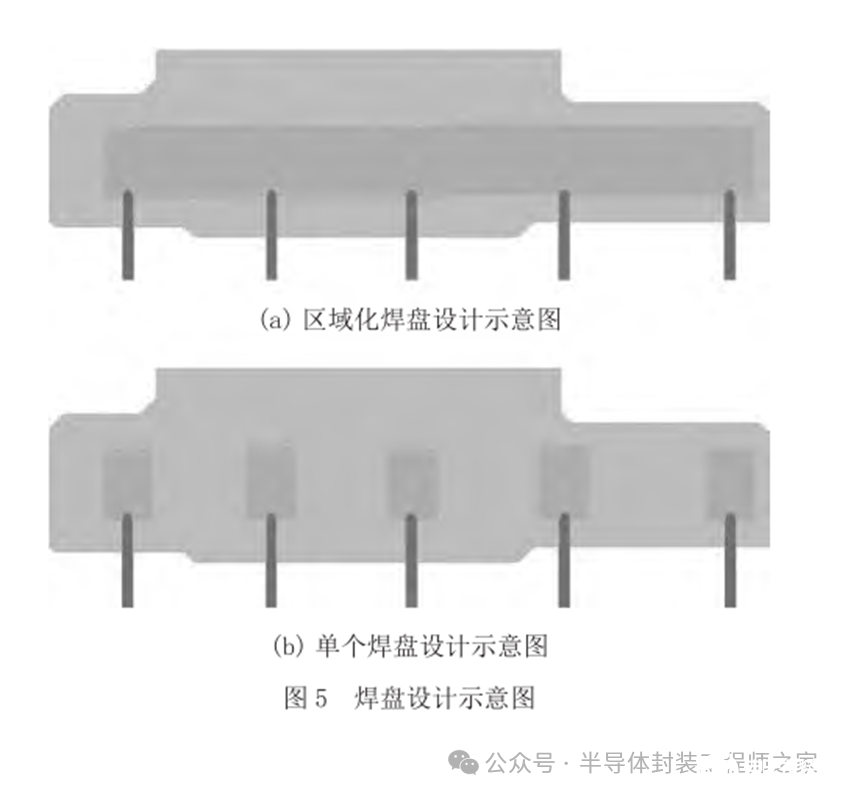

为避免较大面积焊盘经历环境试验后出现的塑封器件分层情况,建议改进焊盘设计,将原区域化设计焊盘(图5(a))优化为单个焊盘设计(图 5(b)),优化后单个焊盘尺寸为 0.15 m m ×0.1 m m ,由该款塑封 SIP 集成模块中其余较小面积焊盘试验后均无分层情况可以判断,该优化方案可行。

结合本次产品失效情况,提出如下塑封产品结构可靠性设计注意事项:

塑封器件分层不仅与塑封原材料选择、工艺控制相关,与器件结构设计也息息相关。在高可靠性塑封产品结构设计时,考虑产品电性能基础上,需加强可靠性设计,尽量避免使用较大面积整体区域化焊盘设计。当塑封料附着于较大面积整体区域化焊盘时,粘接力下降,经历温、湿度应力试验后易出现轻微分层形貌,对产品长期使用可靠性产生影响。

5 结论

面对复杂结构的塑封模块产品设计,其可靠性与塑封原材料选择、工艺控制、器件结构设计均相关[3] ,较大面积区域设计将降低产品可靠性,在经历一定温度、湿度应力试验后表现出分层,甚至直接引起产品失效。在高可靠性产品结构设计时,需考虑结构设计的可靠性。

审核编辑 黄宇

-

SiP

+关注

关注

5文章

506浏览量

105374 -

封装

+关注

关注

127文章

7948浏览量

143121 -

集成模块

+关注

关注

0文章

51浏览量

12387

发布评论请先 登录

相关推荐

航空发动机转子系统可靠性分析的最新进展

关于分布式电源和电动汽车的配电网可靠性分析

UPS电源的安全性和可靠性分析

PCB高可靠性化要求与发展——PCB高可靠性的影响因素(上)

基于可靠性设计感知的EDA解决方案

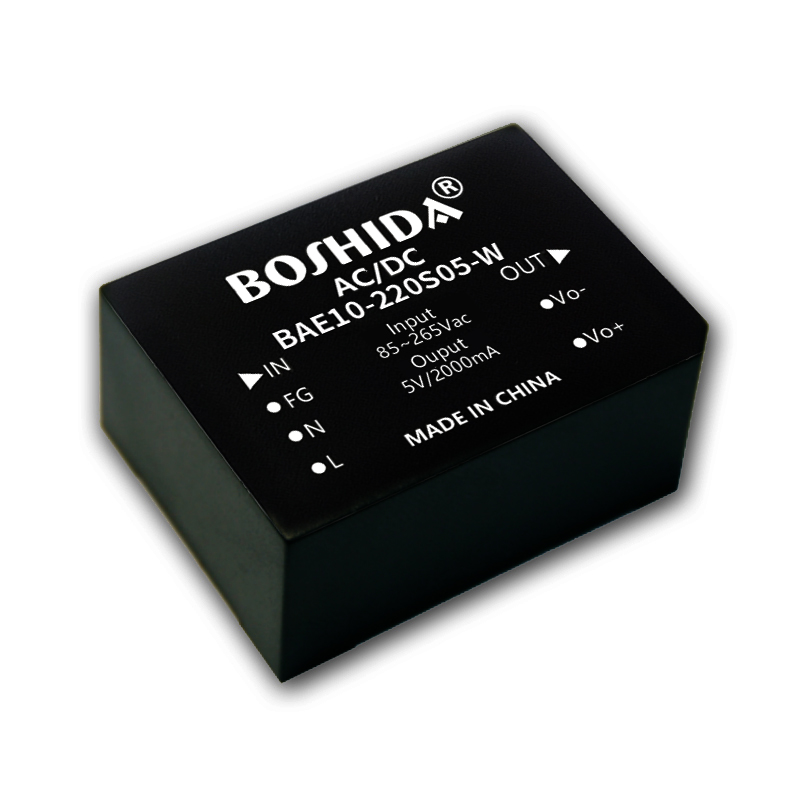

AC/DC电源模块的可靠性设计与测试方法

半导体封装技术的可靠性挑战与解决方案

SMT加工厂的贴片加工工艺及可靠性分析

化学镀镍钯金电路板金丝键合可靠性分析

BOSHIDA 模块电源的应用领域分析 稳定电源供电 提高设备的可靠性和稳定性

Sip技术是什么?Sip封装技术优缺点

塑封SIP集成模块封装可靠性分析

塑封SIP集成模块封装可靠性分析

评论