QFN封装引脚间距较小问题:产生原因与解决方案

QFN封装引脚间距较小问题是什么?

产生QFN封装引脚间距较小问题,为什么?

解决QFN封装引脚间距较小问题要怎么办?

QFN封装的引脚间距较小是指在该封装中,相邻引脚之间的距离相对较小。这种设计有助于减小整体封装的尺寸,使芯片的集成更加紧凑,从而在有限的空间内容纳更多的引脚和电路。这也是QFN封装被广泛用于需要小型化和高集成度的应用的原因之一。

小间距的引脚可以提供以下优势:

紧凑性:

引脚间距较小允许在有限的空间内容纳更多的引脚,从而实现紧凑的封装设计。

电气性能:

小间距有助于减少引脚之间的电感和串扰,对于高频应用具有一定的优势。

热性能:

小间距有助于提高散热性能,因为在相同的底部封装面积上有更多的引脚可以用于散热。

信号完整性:

较小的引脚间距可以降低信号传输的损失,对于高速信号和高频应用更有利。

需要注意的是,虽然小间距可以提供上述优势,但也增加了焊接和布局的复杂性,因此在设计和制造过程中需要特别注意。焊接过程需要更高的精度,而布局需要更谨慎地考虑信号完整性和热管理。

"QFN封装"是什么?

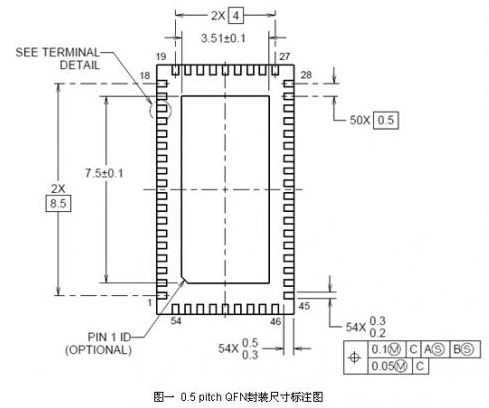

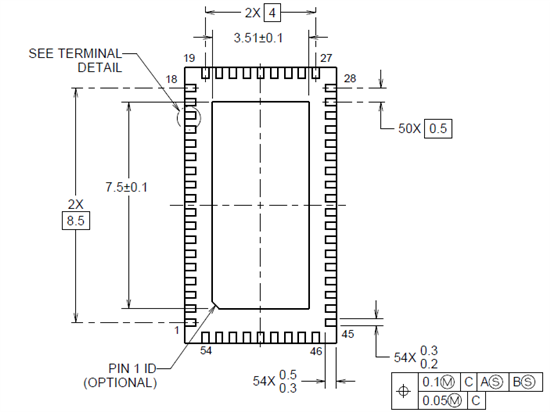

QFN是Quad Flat No-leads的缩写,它是一种集成电路封装的形式。QFN封装通常是一种无引脚焊盘的封装,也被称为“裸露焊盘”或“底部焊盘”封装。与传统的封装相比,QFN封装的特点是它没有外露的引脚,而是将引脚隐藏在封装的底部。

QFN封装的主要特点包括:

无引脚外露:

QFN封装没有传统封装中突出的引脚,而是将引脚放置在封装的底部,通过焊盘连接到电路板上。

紧凑设计:

由于没有引脚外露,QFN封装可以设计得非常紧凑,从而占用更少的空间。

散热性能好:

由于QFN封装的底部通常是金属的,因此它具有良好的散热性能,有助于提高芯片的热稳定性。

适用于高频应用:

由于QFN封装的设计,它对高频应用有较好的适应性,减少了因引脚长度和电感等因素引起的信号失真。

QFN封装在电子产品中广泛应用,特别是在需要小型化、高性能和散热要求较高的应用中,如移动设备、通信设备和各种嵌入式系统。

QFN封装引脚间距较小问题会导致什么?

焊接困难:

引脚间距较小可能导致焊接过程的复杂性增加。在组装过程中,对焊点的精确控制要求较高,需要更高的生产精度,否则可能导致焊接质量不稳定,例如焊接不良或短路。

布局设计挑战:

较小的引脚间距使得布局设计更为复杂。在电路板设计中,需要特别注意信号完整性、阻抗匹配和防止串扰,以确保电路性能稳定。

维修困难:

由于引脚间距较小,对QFN封装的芯片进行维修变得更加困难。手工焊接和重新焊接可能需要更高的技术水平。

散热挑战:

尽管较小的引脚间距有助于提高散热性能,但也可能使散热更为具有挑战性。在高功率应用中,需要特别注意散热设计,以确保芯片工作在安全的温度范围内。

高频应用的损耗:

对于极高频或高速数字应用,小引脚间距可能导致信号传输损耗增加,需要更加精密的布局和设计。

总体而言,虽然QFN封装引脚间距较小的设计提供了许多优势,但在选择和应用时,设计工程师需要在小型化、性能、制造工艺和可维护性之间进行权衡,并确保在应用中的合适性。

出现QFN封装引脚间距较小问题是为什么?

01小型化和高集成度:

QFN封装的设计旨在实现小型化和高度集成的电子器件。通过减小引脚间距,芯片制造商可以在有限的空间内容纳更多的引脚,从而实现更紧凑的封装。

02空间效率:

较小的引脚间距使得QFN封装能够更有效地利用底部封装面积,因为引脚可以更紧密地排列。这对于现代电子设备中有限的空间非常重要,例如智能手机、平板电脑和其他便携式设备。

03散热性能:

QFN封装通常具有金属底部,可以提供较好的散热性能。通过减小引脚间距,可以在有限的底部空间内增加更多的焊盘,提高了封装的散热效果,有助于维持芯片的温度在可接受的范围内。

04高频应用:

小引脚间距有助于减小引脚之间的电感和串扰,这对于高频应用非常重要。在无线通信、射频(RF)和其他高频电路中,QFN封装的设计可以提供更好的性能。

解决方案

精密制造工艺:

提高制造工艺的精度是确保引脚间距小的QFN封装焊接质量的关键。使用高精度的制造设备和工艺能够减小焊接误差,提高焊点的可靠性。

精确的布局设计:

在电路板布局设计阶段,工程师需要仔细考虑引脚的布局,确保信号完整性、阻抗匹配和防止串扰。使用先进的设计工具可以帮助进行精确的布局规划。

高精度的焊接技术:

采用高精度的焊接技术,如回流焊或波峰焊,以确保引脚焊接的质量。在生产过程中,控制温度和焊接时间,以防止焊点过度或不足。

自动化生产:

自动化生产线可以提高制造过程的一致性和精度。使用自动化设备,如表面贴装技术(SMT)设备和焊接炉,可以减小人为因素对生产过程的影响。

良好的散热设计:

对于QFN封装,由于底部通常是金属的,散热性能较好。设计工程师应该注重良好的散热设计,确保芯片在工作时能够有效散热,避免温度升高。

封装选择:

在一些特殊情况下,可以考虑选择具有稍大引脚间距的QFN封装型号,以降低设计和制造的难度,尽管可能会略微增加封装的体积。

这些解决方法的选择取决于具体的应用和设计要求。在实际应用中,工程师需要综合考虑设计复杂性、生产成本、性能和可维护性等因素,以找到最合适的平衡点。

审核编辑:汤梓红

-

集成电路

+关注

关注

5403文章

11698浏览量

364678 -

QFN封装

+关注

关注

0文章

134浏览量

16890 -

引脚

+关注

关注

16文章

1303浏览量

51342

原文标题:QFN封装引脚间距较小问题,怎么办?

文章出处:【微信号:CEIA电子智造,微信公众号:CEIA电子智造】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

小间距QFN封装PCB设计串扰抑制问题分析与优化

什么是小间距QFN封装PCB设计串扰抑制?

怎么抑制PCB小间距QFN封装引入的串扰

针对PCB设计中由小间距QFN封装引入串扰的抑制方法

PCB设计中由小间距QFN封装引入串扰的抑制方法分析

PCB小间距QFN封装引入串扰的抑制方法资料下载

小间距QFN封装PCB设计串扰抑制的分析

SMT加工产生冷焊的原因以及解决方案

宇凡微QFN20封装介绍,QFN20封装尺寸图

罗彻斯特电子QFN解决方案

QFN封装引脚间距较小问题的产生原因与解决方案

QFN封装引脚间距较小问题的产生原因与解决方案

评论