在Verilog中,repeat语句不需要使用begin和end块。repeat语句是一种循环控制语句,允许重复执行一个代码块指定的次数。它的一般语法如下:

repeat (n) statement;

其中,n是一个常量或者表达式,指定代码块需要循环执行的次数。statement表示需要重复执行的语句。

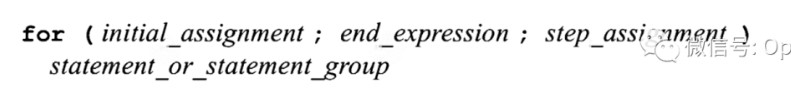

与其他循环控制语句相比,如for和while,repeat语句的语法较为简单。它是一种方便的循环结构,特别适用于当循环次数是已知的固定值时。

下面是一个使用repeat语句的例子,可以更好地理解它的用法:

module example;

reg [3:0] count;

reg [3:0] data;

always @ (posedge clk)

begin

repeat (4) begin

data <= data + 1;

end

end

endmodule

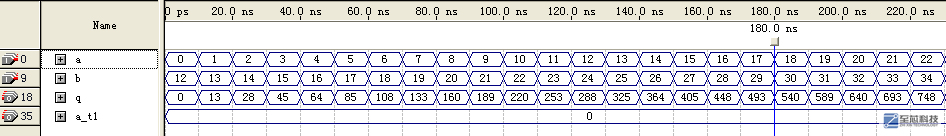

在上述例子中,定义了一个4位的计数器变量count和一个4位的数据变量data。在每个时钟的上升沿,通过repeat语句重复执行一个代码块,这个代码块将data变量加1,循环执行4次。这样,每4个时钟周期,data变量的值将增加4。

需要注意的是,repeat语句不具备循环条件判断功能,只是简单地重复执行指定的次数。因此,不需要使用begin和end块来组织代码块,只需在repeat语句后面直接跟上要执行的语句即可。

总结起来,repeat语句是一种Verilog中的循环控制语句,用于重复执行指定次数的代码块。它的语法简单,不需要使用begin和end块,直接在repeat语句后跟上要执行的语句即可。

-

Verilog

+关注

关注

28文章

1351浏览量

110119 -

循环

+关注

关注

0文章

92浏览量

15986 -

代码

+关注

关注

30文章

4790浏览量

68647 -

语法

+关注

关注

0文章

44浏览量

9824

发布评论请先 登录

相关推荐

重点介绍所有综合编译器都支持的for和repeat循环

中断服务中调用FreeRTOS系统函数,是否必须用FromISR结尾?

vhdl与verilog语法比较

大神看看那里出了问题啊,红绿黄交通灯行为的Verilog模块

verilog 语法错误: A begin/end block was found with an empty body.

零基础学FPGA(四)Verilog语法基基础基础(中)

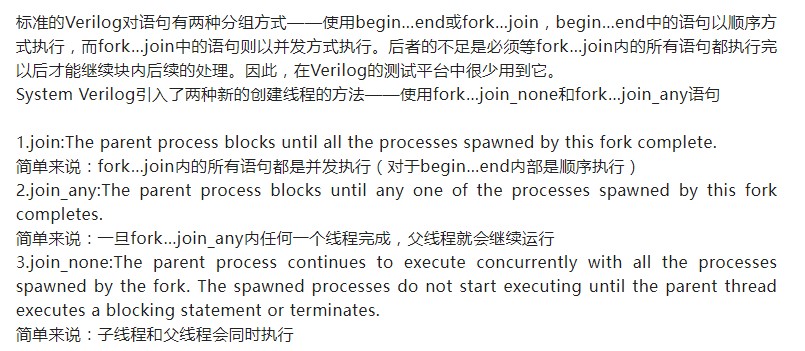

begin ...... end 与 fork ...... join 语句的 区别 ------ 转载

关于Verilog中always块敏感信号的疑问与讨论。

verilog中generate语句的用法分享

简谈FPGA verilog中的repeat用法与例子

verilog中repeat必须用begin和end吗

verilog中repeat必须用begin和end吗

评论