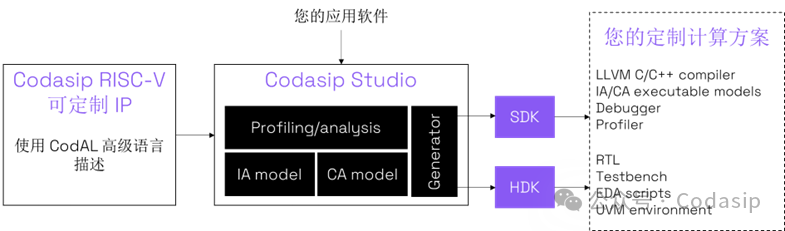

→ Codasip Studio and RISC-V 处理器核

从标准处理器核开始,无需“冷启动”

• 基于已开发的嵌入式或应用处理器核 (如L31等)

• 高质量水准,达量产标准

• 完全符合RISC-V规范

通过Codasip Studio实现您需要的差异化

• 可配置/可定制

• 使用CodAL体系结构描述语言(类C高级语言)

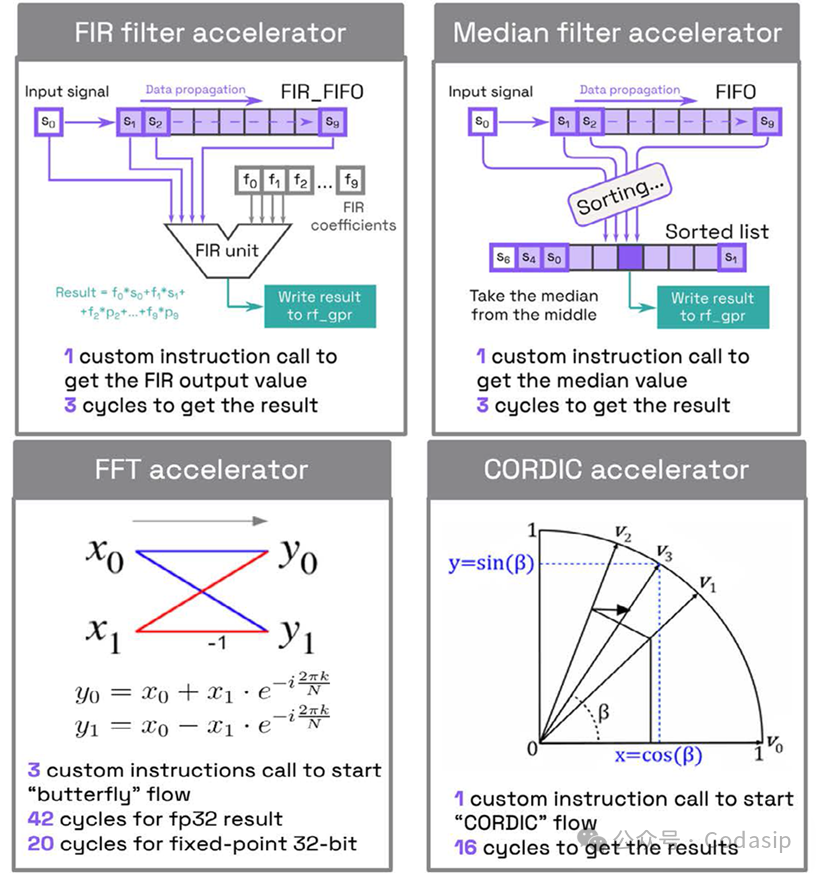

→ 用CodAL实现DSP加速器

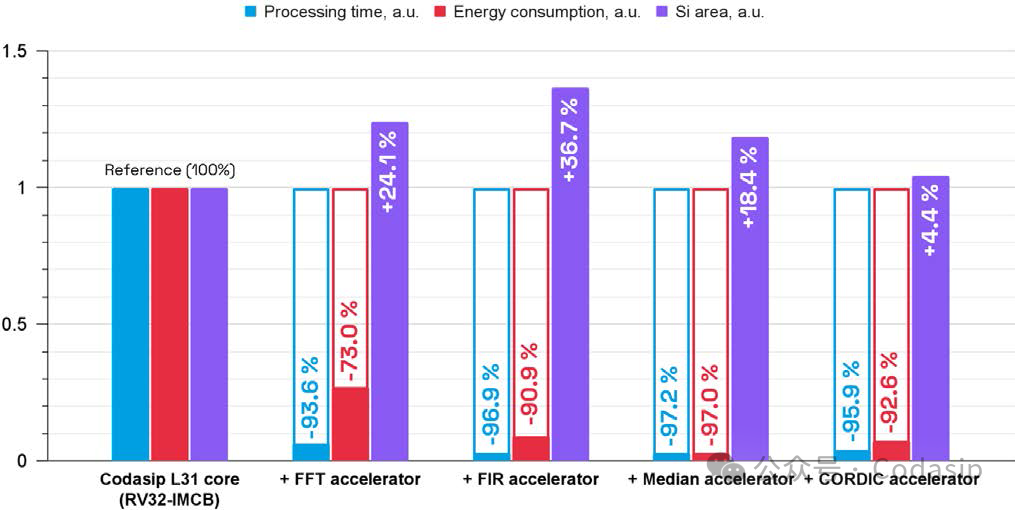

→ DSP定制如何影响PPA

基于嵌入式RISC-V核定制专用DSP,以处理如上四种代表性的DSP算法为例。性能和能耗分别提升和缩减为14.4倍和0.27倍(FFT),14.4倍和0.1倍(FIR)、30倍和0.03倍(Median filtering)和24.3倍和0.08倍(Cordic),通过增加有限的面积即得到了此效果。

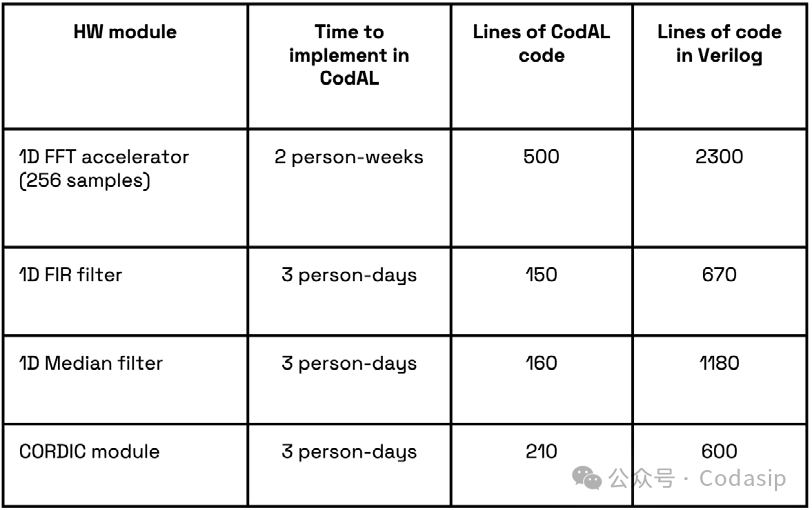

使用CodAL和Codasip Studio,通过“开箱即用”的SDK和HDK等自动生成工具,结合精练的内核描述,轻松实现RISC-V的定制,缩短产品开发周期。下表列出了实现上述的DSP定制的预估代码量和工作量。

审核编辑:刘清

-

处理器

+关注

关注

68文章

19461浏览量

231411 -

dsp

+关注

关注

554文章

8060浏览量

350859 -

嵌入式

+关注

关注

5096文章

19199浏览量

308272 -

加速器

+关注

关注

2文章

809浏览量

38161 -

RISC-V

+关注

关注

45文章

2334浏览量

46741

原文标题:基于嵌入式RISC-V处理器核 轻松实现DSP扩展设计

文章出处:【微信号:Codasip 科达希普,微信公众号:Codasip 科达希普】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

晶心科技推出突破性的RISC-V 27系列处理器及向量扩展指令处理器

risc-v与esp32架构对比分析

学习RISC-V入门 基于RISC-V架构的开源处理器及SoC研究

如何入门RISC-V嵌入式

UltraSoC宣布提供业界首款RISC-V嵌入式处理器产品

Codasip RISC-V处理器增加Veridify安全算法 增强嵌入式系统的安全性

IAR Embedded Workbench将支持RISC-V太空级处理器NOEL-V

专家力荐|《嵌入式系统原理与开发——基于RISC-V和Linux系统》新书发售

基于嵌入式RISC-V处理器核轻松实现DSP扩展设计

基于嵌入式RISC-V处理器核轻松实现DSP扩展设计

评论