1简介

冗长的编译和仿真,对于稍大的工程,编译加上仿真可能需要1个小时以上并且占用大量内存,而跑回归更是消耗大量的时间以及内存资源,本文主要给大家带来VCS使用技巧,DPO,DPO全称是Dynamic Performance Optimizer,主要用于优化编译和仿真(时间/内存),减少资源的使用,属于VCS的高级功能。仅需要很少的命令即可引入当前工程,体验来看,优化基本都在30%以上(数据来自亦安自己的测试,具体以实际为准)。

2DPO的特性

接入工程简单,只需要简单的命令

深度优化编译和仿真,包含时间和内存的优化

3该怎么使用DPO

目前该功能可能需要较高版本VCS DPO才比较完善。

使用逻辑非常简单:第一步,学习(learn)以及合并(merge)。第二步,应用(apply)。例如有500个case,我们先在learn模式跑完case,然后merge,之后便可以在应用(apply)模式下跑项目。最终会有比较好的编译和仿真优化,一般情况下,工程没有巨大改变,不需要重新learn。

我们打开VCS_HOME目录下,doc/examples/dpo/dpo_use_model,官方给了一个demo,Makefile如下(部分),主要涉及参考,学习,合并,获得建议,应用,报告。涉及的命令非常的简单,如果想更深入了解请参阅手册。该目录下执行make即可跑demo。

dpo_reference: vcs-sverilog-full64-ntb_optsuvm-1.2ubus_tb_top-debug_access+all-lca-lcomp_ref.log-dpo-dpo_optsapps=vcsgd+user_tag=reference ./simv+UVM_NO_RELNOTES+UVM_TESTNAME=test_2m_4s-lsimv_ref.log dpo_learn: rm-rfsimvsimv.daidircsrcvc_hdrs.h*.keyvcs.cfg vcs-sverilog-full64-ntb_optsuvm-1.2ubus_tb_top-debug_access+all-lca-lcomp_learn.log-dpo-dpo_optsmode=learn+apps=default,lint,upfopt,pgates+user_tag=learn+dbdir=dpo_learndb-dpo_optscfg=cfg ./simv+UVM_NO_RELNOTES+UVM_TESTNAME=test_2m_4s-lsimv_learn.log merge_db: dporgmerge-ddpo_learndb dump_reco: dporgdump-ddpo_learndb echo"#####EnablingallrecommendationsdumpedbyDPOfromdpo_reco.csv#####" sed-i"s/^N,/Y,/g"dpo_reco.csv dpo_apply: rm-rfsimvsimv.daidircsrcvc_hdrs.h*.keyvcs.cfg vcs-sverilog-full64-ntb_optsuvm-1.2ubus_tb_top-debug_access+all-lca-lcomp_apply.log-dpo-dpo_optsreco_file=dpo_reco.csv+apps=default,fgp,lint,upfopt,pgates+user_tag=apply+learn_dbdir=dpo_learndb+cfg=cfg ./simv+UVM_NO_RELNOTES+UVM_TESTNAME=test_2m_4s-lsimv_apply.log dpo_report: dporgreport-ddpo_dbdir

4查看DPO报告

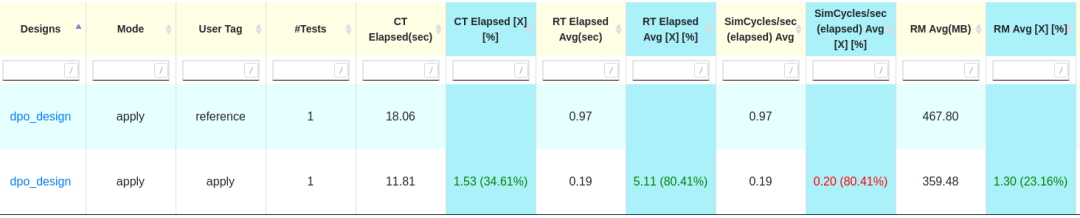

dporgReport目录下用浏览器打开即可,可以打开相关的报告。可以看到相关的优化比率,CT(Compile Time),RT(Run Time),RM(Memory)。

5DPO设置的权衡

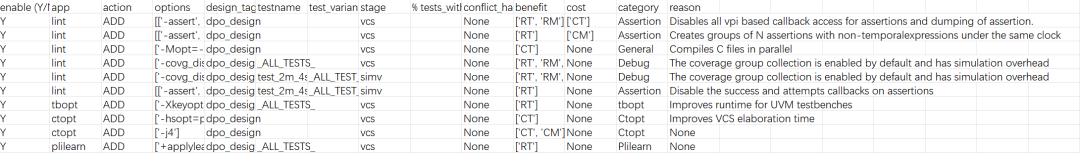

任何事情的选择很难是各个方面都会带来优势,所以需要结合自己的项目去权衡应该优化那些方面,哪里是关键的设计,那么选择优化该方向。相关建议可以在文件dpo_reco.csv打开查看。

审核编辑:黄飞

-

内存

+关注

关注

8文章

3020浏览量

74019 -

VCS

+关注

关注

0文章

79浏览量

9602

原文标题:如何让你的仿真编译性能优化?(VCS 高级特性)

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

VCS仿真指南(第二版).pdf

基于linux系统实现的vivado调用VCS仿真教程

优化编译和仿真的VCS使用技巧

优化编译和仿真的VCS使用技巧

评论