IGBT和碳化硅(SiC)模块的开关特性受到许多外部参数的影响,例如电压、电流、温度、栅极配置和杂散元件。

测试设置

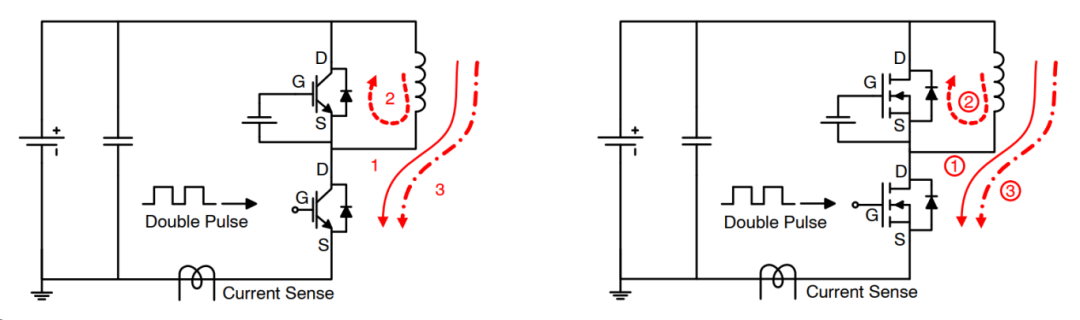

双脉冲测试 (Double Pulse Test ,DPT) 采用不同的设置来分析SiC和IGBT模块的开关特性。如表1所示,对于直流链路环路电感影响分析,可在直流链路电容和模块之间添加母线来进行。对于栅极环路电感影响分析,如表10所示,在栅极驱动板和模块之间添加外部插座或电线。

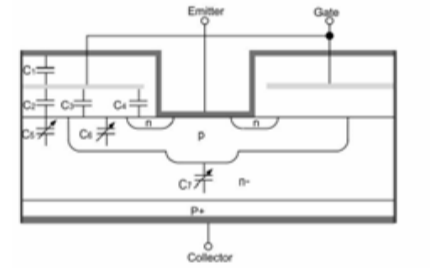

为了研究模块的开关特性,本次测试使用 900V、1.7mQ EliteSiC Power功率模块 (NVXR17S90M2SPC)和 750V Field Stop 4 VE-Trac Direct模块 (NVH950S75L4SPB) 作为待测器件(DUT)。

图 1. 双脉冲测试设置

IGBT的开关特性与栅极环路电感(LG)的关系

栅极环路电感会对开关特性造成影响。针对NVH950S75L4SPB模块,在满足以下条件的情况下进行了双脉冲测试。

DUT: 低边FS4 750V 950A IGBT 模块 (NVH950S75L4SPB)

VDC = 400 V

IC = 600 A

VGE = +15/−8 V

RG(on) = 4.0 Q

RG(off) = 12.0 Q

Tvj= 25℃

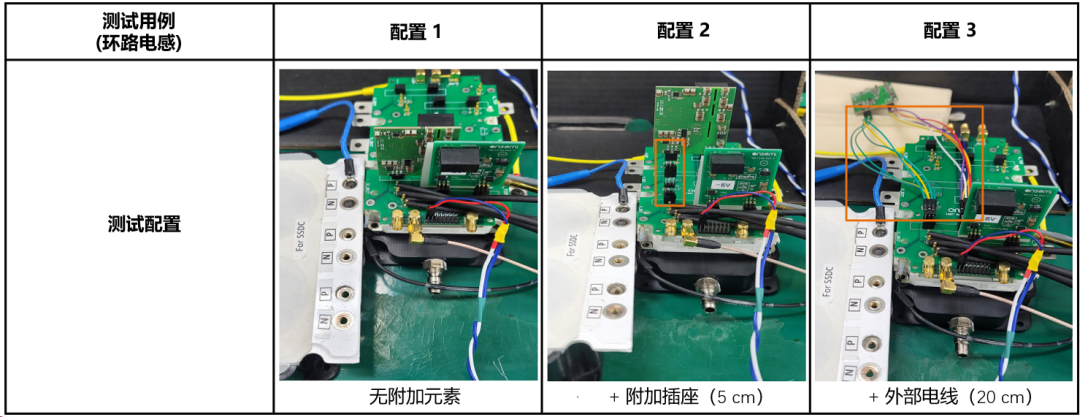

表10显示了三种不同的栅极环路电感与开关特性之间的测试配置。在栅极驱动器和模块之间添加了外部插座或延长线,以模拟在栅极环路上增加的电感。

表 10. 栅极环路电感测试设置

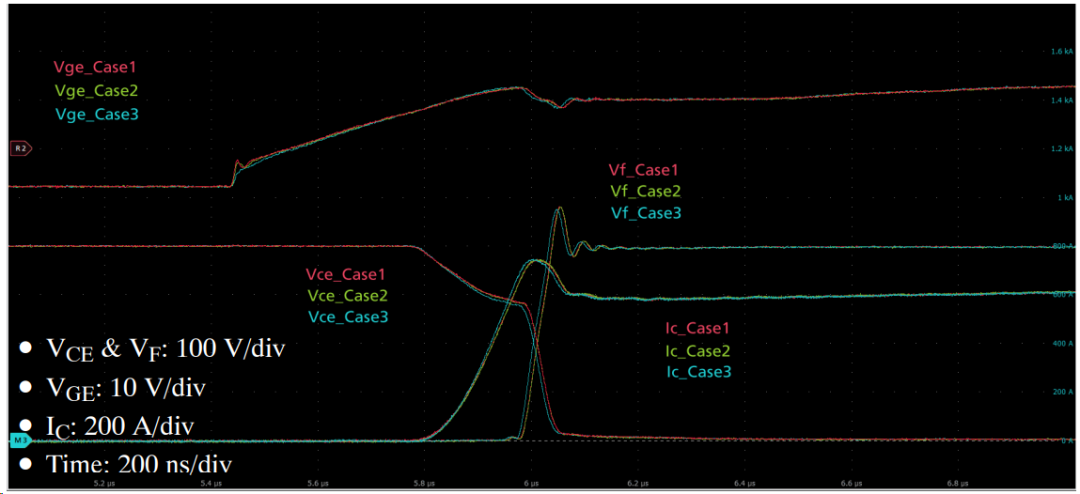

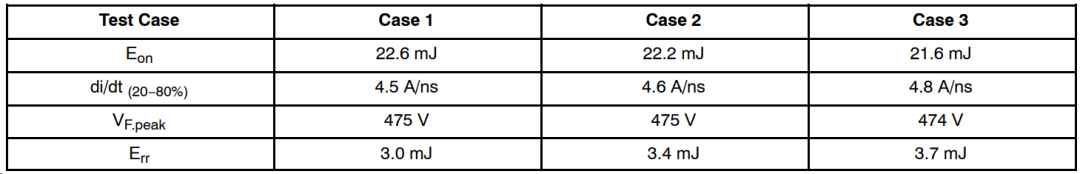

图10显示了在IGBT导通阶段,不同栅极环路测试配置下的波形对比,总结的特性如表11中所述。较长的栅极环路测试设置显示出较低的Eon值以及更快的di/dt。栅极环路电感主要由栅极环路长度引起。在开始导通时,栅极环路电感能够减缓升流(rising current)速度。

当栅极电压达到米勒平台时,环路电感充当电流源(current source),该电流源通过向栅极提供更多电流来加快di/dt的变化。相较于直流链路环路,栅极环路长度对导通特性的影响较小。同时,更高的栅极环路电感会增加栅极电压的过冲,这可能会因 RG 而失去可控性。

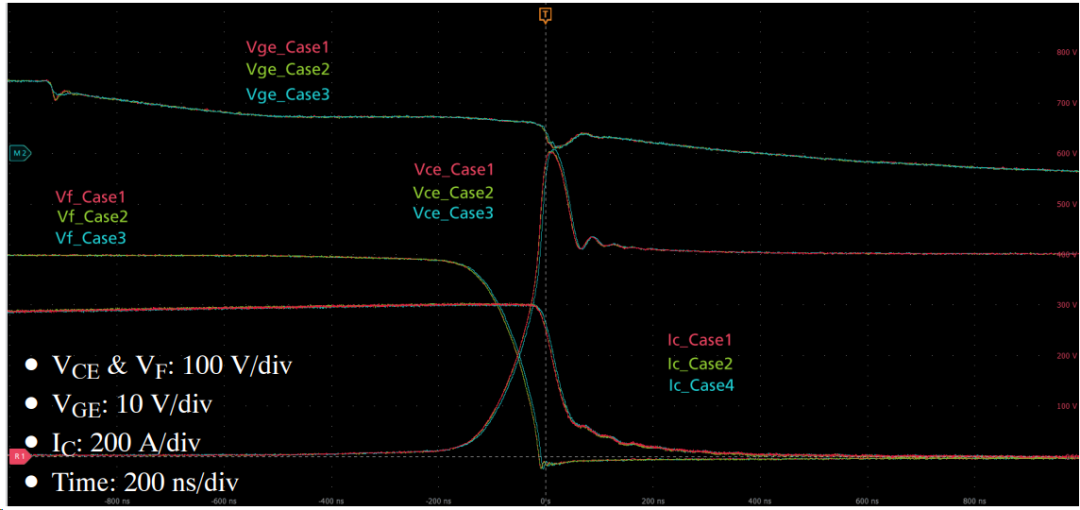

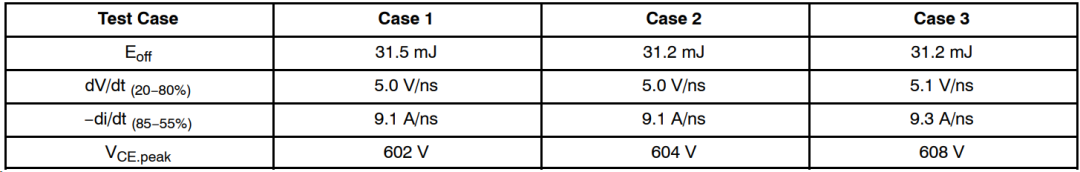

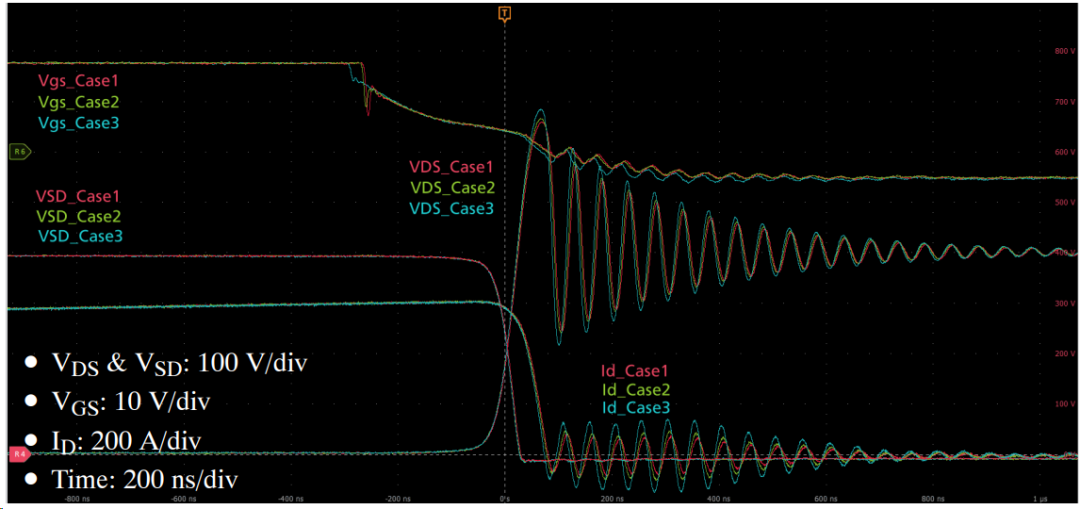

图11展示了在IGBT关断期间,不同栅极环路电感设置下的波形对比。总结出的特性如表12所述。关断特性相比于导通特性受到的影响较小。在关断初期,由栅极回路电感引起的下冲电压略有不同,但并不会对关断特性造成实质性影响。当栅极电压达到米勒平台阶段时,dV/dt和di/dt会因下冲电压而略有变化,但在短时间内会被栅极灌电流迅速恢复。

图 10. IGBT导通波形与栅极环路电感(LG)的关系

表 11. 总结:IGBT导通特性与栅极环路电感

图11展示了在IGBT关断期间,不同栅极环路电感设置下的波形对比。总结出的特性如表12所述。关断特性相比于导通特性受到的影响较小。在关断初期,由栅极回路电感引起的下冲电压略有不同,但并不会对关断特性造成实质性影响。当栅极电压达到米勒平台阶段时,dV/dt和di/dt会因下冲电压而略有变化,但在短时间内会被栅极灌电流迅速恢复。

图 11. IGBT关断波形与栅极环路电感(LG)的关系

表 12. 总结:IGBT关断特性与栅极环路电感(LG)

SiC MOSFET开关特性与栅极环路电感(LG)的关系

本小节分析了不同栅极环路电感(LG)对SiC MOSFET 开关特性的影响。在与表 10 相同的测试条件下,对 NVXR17S90M2SPC 模块进行了双脉冲测试,测试条件如下。

DUT: 低边NVXR17S90M2SPC

VDC = 400 V

IC= 600 A

VGE= +18/−5 V

RG(on)= 3.9 Q

RG(off)= 1.8 Q

Tvj= 25℃

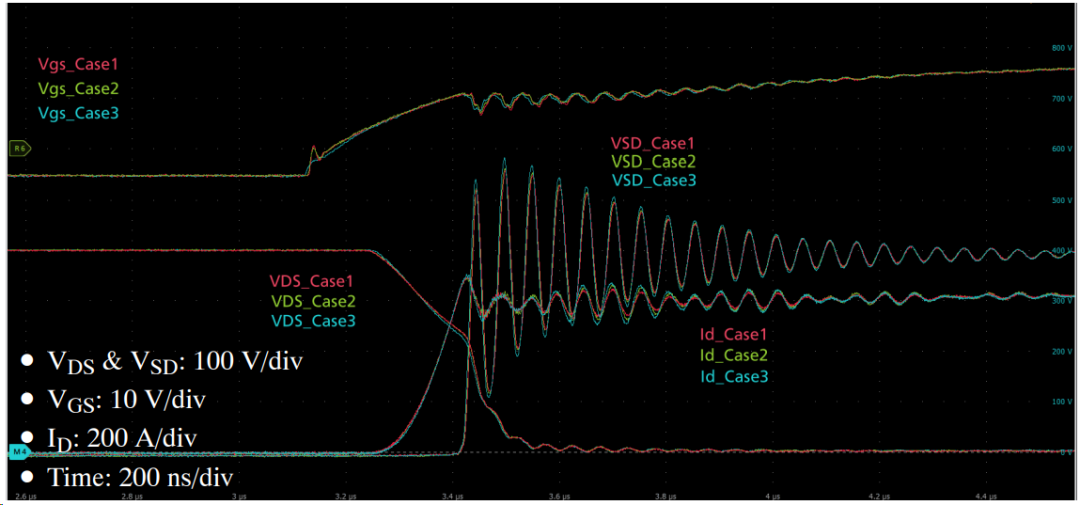

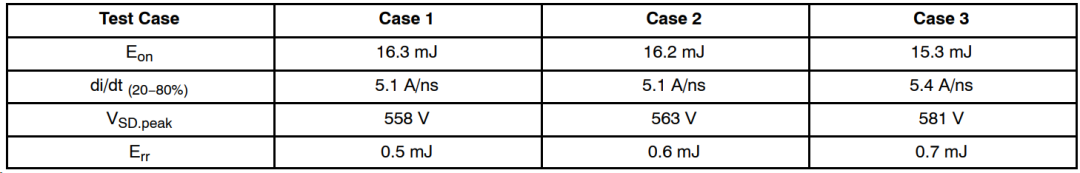

图 12 显示了 SiC MOSFET 导通期间,栅极环路测试不同设置下的波形比较,表 13 对其特性进行了总结。与 IGBT 的情况一样,较长的栅极环路测试条件下,较快的 di/dt 导致较低的 Eon 和较高的 VSD_peak峰值电压。

图 12. SiC MOSFET导通波形与栅极环路电感(LG)的关系

表 13. 总结:SiC MOSFET 导通特性与栅极环路电感

图13展示了在SiC MOSFET关断期间,不同栅极环路电感设置下的波形对比。总结出的特性如表14中所述。在测试时,若使用较高的栅极环路电感,即使VDS过冲电压增大,也会反应出较快的di/dt及较低的Eoff。关断后,可作为电磁干扰(EMI)噪声源的ID振荡幅度取决于栅极环路的长度。

图 13. SiC MOSFET关断波形与栅极环路电感(LG)的关系

表 14. 总结:SiC MOSFET关断特性与栅极环路电感

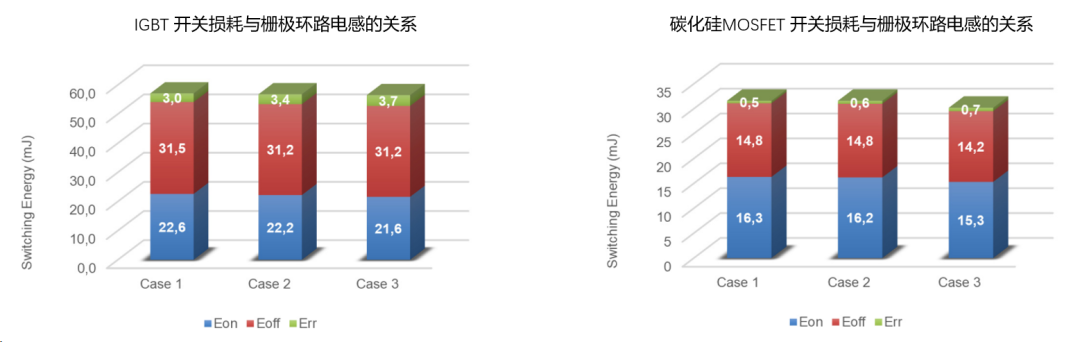

总结

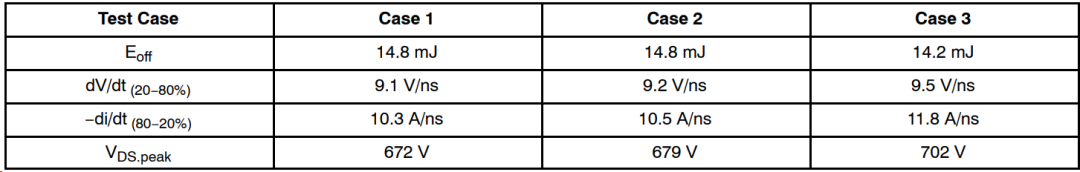

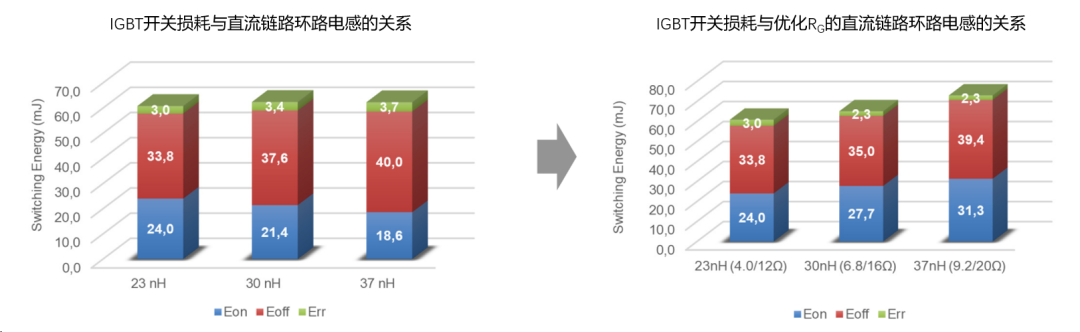

在本应用笔记中分析了电感对IGBT和SiC MOSFET模块开关特性的影响。较高的直流链路环路电感设置会在Eoff和Err较高时导致较低的Eon。此外,结果显示,在23nH和37nH测试设置之间的总开关损耗差距小于2mJ。这可能会让人误认为杂散电感对开关损耗影响不大。

然而,为了符合RBSOA和EMC的要求,调整外部栅极电阻(RG)或其他系统参数很有必要,尽管这样做会牺牲 di/dt 的可控性并且增加开关损耗。图14和图15展示了在优化外部RG前后,直流链路环路电感条件下IGBT和SiC的开关损耗情况。在优化外部RG之前,采用较高的直流链路环路电感设置,总开关损耗相似,但在针对系统性能优化外部RG之后,当直流链路环路电感从23nH变为37nH时,IGBT和SiC案例中的总损耗分别增加了20%和92%。

图 14. IGBT 总损耗比较

图 15. SiC MOSFET 总开关损耗比较

较高的栅极环路电感设置在米勒平台效应后,通过电感效应带来稍快的导通瞬态。从开关损耗的角度来看,其影响比直流链路环路电感要小一些。由于不希望出现栅极过冲现象,较高的栅极环路电感会导致栅极控制能力降低。从短路情况来看,这种电感会拉高栅极电压,因此,通过增加栅极电压可以缩短短路耐受时间。此外,较长的栅极环路可以充当天线,电磁噪声抗干扰能力差,并且可能对其他电路产生干扰。

IGBT 开关损耗与栅极环路电感的关系

总之,最小化直流链路和栅极环路电感对于IGBT/SiC的开关应用是必要的,在满足可控性和电磁兼容性的同时获得更低的开关损耗。

审核编辑:刘清

-

驱动器

+关注

关注

52文章

8071浏览量

145715 -

电磁兼容

+关注

关注

54文章

1833浏览量

97757 -

IGBT

+关注

关注

1261文章

3737浏览量

247833 -

SiC

+关注

关注

29文章

2718浏览量

62326 -

功率模块

+关注

关注

10文章

447浏览量

45001

原文标题:栅极环路电感对SiC和IGBT功率模块开关特性的影响分析

文章出处:【微信号:onsemi-china,微信公众号:安森美】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

栅极环路电感对IGBT和EliteSiC Power功率模块开关特性的影响简析

栅极环路电感对IGBT和EliteSiC Power功率模块开关特性的影响简析

评论