借助Cadence和Intel代工厂的联手,我们成功开发并验证了一套高度整合的先进封装工艺。押宝于嵌入式多晶粒互连桥接(EMIB)技术,以解决日益复杂的异构集成多芯粒结构。此举意味着Intel客户可以高效利用先进封装技术,助推高性能计算(HPC)、人工智能和移动设备计算等领域的设计空间革新发展。

Cadence Allegro® X APD(用以实现元件布局、信号/电源/接地布线、设计同步电气分析、DFM/DFA及最后制造输出)、Integrity™ 3D-IC Platform 及其对应的Integrity System Planner(负责系统级设计聚合、规划和优化)、Sigrity™ 与Clarity™求解器(处理3D电磁提取、双参数生成、早期和签核信号完整性、直流/交流电源分析以及封装模型提取)、Celsius™求解器(用于初始期和定案期的热签核/应力分析)、Virtuoso® Studio(聚焦于EMIB桥接的信号/电源/接地布线问题)以及Pegasus™ Verification System(主要用于DRC和SystemLVS的检验)等组件共同构成这套先进封装流程。

“面对工程师们对多芯粒架构和先进封装的关注度不断提升,至关重要的是提供适当的设计工具和方法”,Cadence定制IC和PCB事业部研发副总裁Michael Jackson强调道,“Cadence和Intel的合作通过提供经EMIB认证的参考流程,引领了一条通往异构集成解决方案的康庄大道。这套精心设计的流程将帮助双方客户轻松应对现代电子设计的挑战,稳立科技市场前线。”

“对于得到无缝设计流程,尽早进行热、信号完整性和电源建模至为关键,”Intel代工厂副总裁Rahul Goyal评论道,“在项目初始阶段就纳入这些考量会让工程师能同时进行设计与验证工作,从而避免可能出现的后继工程拖延。此外,这种前置处理还有助于确认设计的可行性,保证工程永远遵循预定的规范。”

这次战略合作的目标在于全面助力客户,借助Intel技术降低其设计抗险能力。

-

DFM

+关注

关注

8文章

465浏览量

28427 -

求解器

+关注

关注

0文章

78浏览量

4562 -

先进封装

+关注

关注

2文章

434浏览量

292

发布评论请先 登录

相关推荐

PCBA贴片代工全解析:一站式服务流程大揭秘

OLED拼接屏代工厂哪个靠谱?如何考量?

AI与HPC技术推动先进封装行业发展

Intel战略转型新动向:携手AWS深化合作,晶圆代工业务独立运营

软银AI芯片代工转投台积电,Intel代工业务受挫

Cadence与Intel Foundry的战略合作取得重大成果

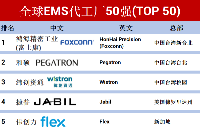

2024年最新全球EMS代工厂50强(TOP 50)

台湾代工厂加大支出,AI PC和服务器成主要驱动力

Cadence携手Intel代工厂研发先进封装流程,助力HPC、AI及移动设备

Cadence携手Intel代工厂研发先进封装流程,助力HPC、AI及移动设备

评论