减少HCI和电迁移的测试时间

许多可靠性“磨损”测试监测的是一个性能参数,该参数随着对数变化的时间长度而稳步下降。在大多数情况下,会测量到10%的退化时间。10%的退化时间是一个基准,因为许多器件在比半导体器件的性能高10%的速度或电压下进行测试。例如,DRAM可能会在45ns的工作时间内被测试,并且能完全正常工作,但随后以较慢的50ns的性能出售。这种“guard-banding" 允许关键性能参数漂移高达10%,且设备不会超出其指定性能。可靠性测试必须证明设备在预期产品寿命 ( 通常为10年或20年 ) 内不会出现超过10%的关键性能参数漂移。

加速应力值可以在较短时间内达到10%的退化时间。然而,需要对失效机制有很好的了解,才能外推出在特定条件下达到10%的退化时间。在大多数情况下,需要在几种不同的应力条件下进行测试,以提取应力条件和退化速率之间的关系。在使用最低应力条件下,增加了测试成本,在有限的测试时间范围内提取需要的参数。

最大应力条件通常受到寄生参数的限制,例如焦耳加热或源极-漏极击穿电压。此外竞争失效机制可以在更高的应力条件下导致测试失效机制的变化 ( 例如:对于电迁移测试,在更高温度下从晶界扩散到体扩散的变化 ) 。这限制了可应用于最高应力条件的加速度。

在了解本期测试技术细节前,我们先来回顾一下今年关于晶圆可靠性测试的云上大讲堂

另一种技术是测量在真实使用条件下达到较小退化百分比的时间。一般退化速率在对数时域中通常是线性的,可以在更短的测试时间内测量到退化较小百分比的变化。在这种测试条件下 “真实条件” 压力水平的使用将只会在一种压力条件下进行测试,并不需要理解压力与时间关系。此外,不会担心较高的应力条件会改变退化速率。然而使用这种技术将需要非常低的仪器噪声水平和非常短的时间分辨率。

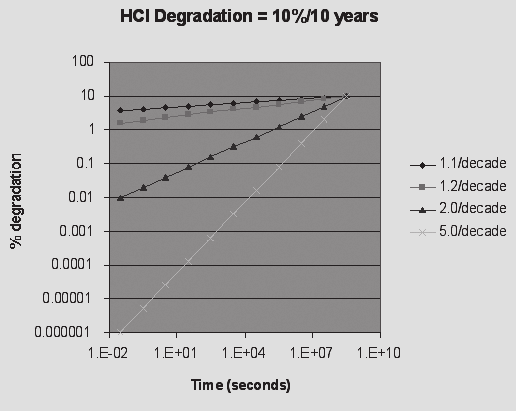

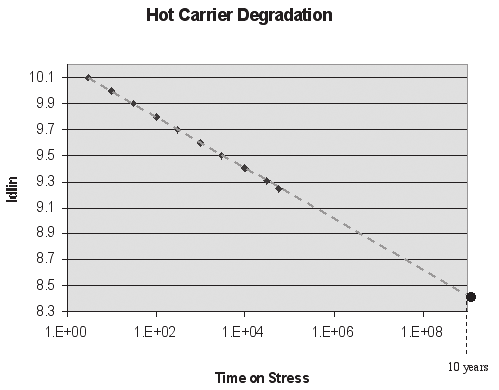

考虑图1中所示的退化速率。在“真实条件应力” 下的晶体管被发现以每年10%年的速度退化。有了这个斜率,十年内退化率低于10%的要求意味着设备在一年内的退化率必须低于9%。这可以扩展到在1/10年或36.5天内需要低于8%的退化。此外,它必须在 3.65天内表现出小于7%的退化,在0.365天或8.76小时内表现出低于6%的退化。如果测试持续时间为 8.76 小时,则必须在40年内外推结果。为了使这种外推具有意义,我们必须能够显示在至少四个数量级的时间内积累的数据。这意味着最小时间分辨率必须为3.15秒。在3.15秒时,我们预计只能测量到2%的退化。准确测量该值需要小于0.2%的测量噪声。

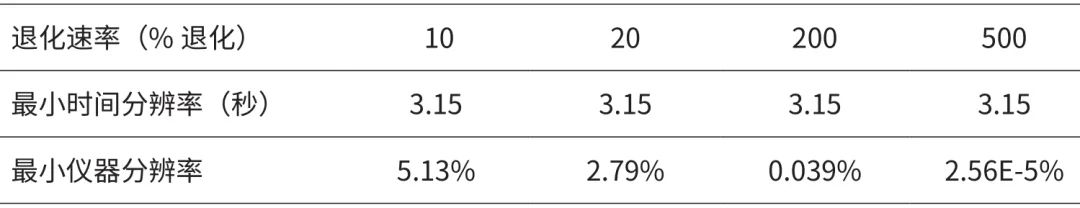

所有这些听起来都很有可能。然而,这些要求显然是退化速率的函数。图1显示了几种不同的退化率,所有这些都导致了十年内10%的退化。表1显示了在8.76小时的应力下测量和外推这些结果的最小时间和最小仪器分辨率。

表1:更高退化率所需的较低仪器噪声

表1清楚地表明,退化速率越陡,在固定的测试持续时间内测量退化所需的仪器噪声就越低。从另一个角度来看,如果给定仪器噪声,则可以使用这些数据来确定最短测试时间。

图1. HCI退化=10%/10年

最小时间点可以从图1中的任何曲线中提取 , 方法是在图上画一条线来表示10倍的仪器噪音。该线与曲线相交的点表示仪表噪声可被视为轻微影响的最短时间。例如,在图1中,噪声水平为0.01%的仪器将具有0.1%的10倍噪声值。在图上画一条0.1%的线,很明显,低的斜率(10%和 20%/十年)的最小应力时间可能非常短。然而,对于200%十年(每十年翻一番),最短时间必须是大约20秒。对于500%的退化斜率,最小应力时间必须为约30000秒或8.3小时。在这一点上,一个无法在十年内达到10%目标设备将显示出10倍的测量噪声。能够很好地预测十年退化的总测试时间必须比这些值长得多。

对于200%/退化斜率,在可以测量退化的第一个精确测量值的点和十年点(3.15亿秒)之间大约有七个数量级。这个差值的一半是3.5个数量级,即最小值的3162倍。这将提供63240秒或17.5小时的最短测试时间。这将允许在3.5个数量级上精确测量退化,并3.5个量级上外推斜率。

对于500%/退化斜率,退化第一次精确测量将在 30000秒时发生。从第一个点到十年点之间只有四个数量级的时间。然后,外推必须只覆盖两个数量级,以实现在不超过测量范围的距离上进行外推的目标。这需要大约三百万秒或 35 天的总测量时间。

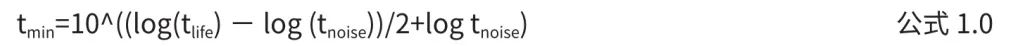

较低的仪器噪声裕度是非常有价值的。如果测量噪声可以从0.01%下降到0.003%,则测试持续时间可以从35天减少到大约16天。显然,仪器噪声、测试持续时间和应用程序寿命之间存在关系。最短测试持续时间为 :

其中 :

公式1.0仅在测试开始后才有用。在测试开始之前,无法知道tnoise的值。该值只能在每个设备的测试过程中测量。测试顺序必须为 :

■1. 在测试开始前,通过对性能参数进行多次测量来测量仪器噪声。噪声定义为单个测量值与测量值平均值之间的差的平方和除以测量次数的平方根。

■2. 开始应力并监测参数直到监测参数中的测量漂移大于测量噪声的十倍。

■3. 一旦晶体管偏移量大于10倍的测量噪声 我们将测量引起这种参数偏移所需的时间。这个“时间到10倍噪声 " 将允许我们根据等式1.0计算总测试时间。该值将是“十倍噪声点” 与预期应用寿命之间距离的一半。这将确保漂移不会在比数据范围更长的范围内外推。

■4. 继续监测样品中的漂移,直到超过计算的测试时间。该点之后的所有点的测量噪声将小于测量的10%。

■5. 根据参数变化百分比对数与时间对数的最小二乘拟合将时间外推至10%漂移,在测量漂移超过10倍时间之间测量噪声和测试的最大持续时间。

许多NMOS FET将在短应力时间内显示出某些测量的性能参数的改善。这使得“真实条件”技术的使用变得复杂。界面空穴陷阱实际上可以增加低栅极场下的沟道迁移率并且在应力的最初几秒期间VT的小幅度降低和增加Idlin或Idsat 。

为了计算这种影响,建议测量参数的最大值(或最小值)并从该拐点而不是从原始(时间零点)计算参数的变化。

示例 1

Idlin在两次测量之间没有应力的情况下,对晶体管的进行了十次测量。记录值为:10.020、10.013、9.990、10.015、10.003、9.985、9.997、10.010、9.990和10.010毫 安。对 于10mA的平均Idlin这给出了与该晶体管的Idlin测量相关联的0.1%的测量噪声。热载流子应力开始于栅极电压为2.3V,漏极电压为 3.7V。以大约3秒、10秒、30秒和100秒的对数时间间隔测量。这些第一个读数点显示的Idlin为10.101mA、10.000mA、9.9mA和9.8mA。该产品的使用寿命为一年。这种压力的最短持续时间是多少 ?

答:测量数据显示,在3秒时的最大Idlin值为 10.101mA。噪声测量值为 0.1%,因此从测量值中减去10倍的噪声将是10.101最大测量值的1%。10秒时的测量值正好比峰值低1%。因此,tnoise是10秒。现在根据公式1.0计算最小试验持续时间。

继续测试趋势开始,测量点为300秒、1000秒,需要3000 秒、10000秒、30000秒和56156秒。如果测量结果与第一次测量中观察到的0.2%/decade变化一致,则读数的记录值为9.7、9.6、9.5、9.4、9.31和9.25mA,用最小二乘法拟合,该数据在十年应力后的Idlin约8.4mA。这将超过十年内10%的目标,该设备将无法通过测试。

自试验不是在加速应力条件下进行的,不会讨论外推模型或异常失效机制。该设备在 “真实条件” 下进行压力测试的。外推中使用的每个测量点都至少是测量噪声的十倍,这样时间外推才是清楚的(图2)。由于数据不是在大于有效数据范围的范围内外推的,因此只要最小二乘拟合良好,时间外推的风险就很低。

图2. HCI的时间外推

应该非常清楚的是,使用这种技术需要低的测量噪声。如果测量噪声约为测量值的1%,则没有时间与该技术相关的节约。10倍噪声的时间将是10%退化的时间,因此无需外推测量值,也无需节省时间。

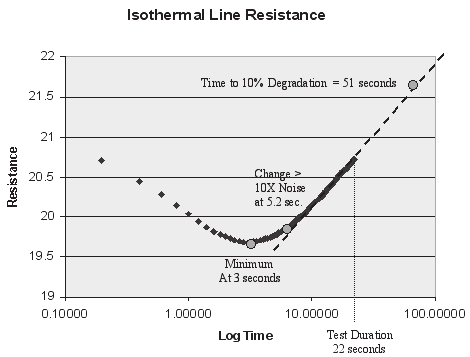

虽然上面的大多数讨论都涉及热载流子寿命外推在使用条件应力的情况下,可以使用相同的技术来最大限度地减少加速试验的时间电迁移测试。再一次预计该设备在对数时域中表现出线性退化。图3显示了金属线的电阻随时间的变化进行等温电迁移测试(JEDEC标准JESD61)。

图3. 等温线电阻

图3再次显示了金属线电阻最初作为时间的函数而下降。这是由于线在高应力温度下的退火效应(晶粒生长、沉淀吸收等)。电阻在三秒读取点达到最小值,然后由于电迁移而开始增加。

本例中的仪器(图3)的测量噪声为0.05%。该噪声的10倍为0.5%。数据显示,在5.2秒的读取点上,测得的电阻变化高于最小值0.5%。该读取点发生在记录最小电阻2.2秒之后。在这一点之后的所有测量都应该显示测量噪声包括小于测量的退化的10%。然后在超过该最小测量点的时间上继续测试一个数量级。测量信号的时间数量级是测量噪声应该允许在该应力水平下精确地外推到10%的退化时间。对于这个例子,测试在22秒后终止。如果测试一直持续到可以测量到10%的退化时间,测试将花费51秒。因此,该技术能够将总测试时间减少2.3倍以上。这对于快速过程控制测试非常重要。

审核编辑:刘清

-

DRAM

+关注

关注

40文章

2311浏览量

183439 -

NMOS

+关注

关注

3文章

294浏览量

34345 -

晶体管

+关注

关注

77文章

9682浏览量

138077 -

半导体器件

+关注

关注

12文章

750浏览量

32036 -

载流子

+关注

关注

0文章

134浏览量

7651

原文标题:白皮书|可靠性测试中,如何减少HCI和电迁移的测试时间?(附直播回放)

文章出处:【微信号:泰克科技,微信公众号:泰克科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

可靠性测试中,如何减少HCI和电迁移的测试时间?

可靠性测试中,如何减少HCI和电迁移的测试时间?

评论