电子发烧友网报道(文/黄晶晶)据报道,三星电子在半导体制造领域再次迈出重要步伐,计划增加“MUF”芯片制造技术,用于生产HBM(高带宽内存)芯片。但是三星在随后的声明中称,关于三星将在其HBM芯片生产中应用MR-MUF(批量回流模制底部填充)技术的传言并不属实。

三星在HBM生产中目前主要采用非导电薄膜(NCF)技术,而非SK海力士使用的批量回流模制底部填充(MR-MUF)封装工艺。报道称之所以要采用MR-MUF是为了解决NCF工艺的一些生产问题。几位分析师也表示,三星的 HBM3 芯片生产良率约为 10-20%,而 SK 海力士的 HBM3 生产良率约为 60-70%。

NCF技术(非导电薄膜技术),是使用热压缩薄膜来连接芯片。可以减少堆叠芯片之间的空间,从而在紧凑的HBM芯片组中堆叠多层芯片。

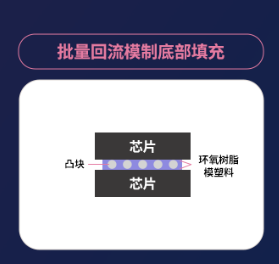

MR-MUF则是将半导体芯片堆叠后,为了保护芯片和芯片之间的电路,在其空间中注入液体形态的保护材料,并进行固化的封装工艺技术。与每堆叠一个芯片时铺上薄膜型材料的方式相较,工艺效率更高,散热方面也更加有效。这种技术为半导体制造带来了更高的集成度和性能提升,尤其在处理大数据和复杂计算任务时,能够显著提升芯片的运行效率和稳定性。

尽管在封装上各自路径不同,不过三星加快了HBM的研发步伐。目前三星已经发布最新的HBM3E 12H产品,将HBM3E DRAM芯片堆叠至12层,是迄今为止容量最大(36GB)的HBM产品。HBM3E 12H提供了高达每秒1280千兆字节(GB/s)的最高带宽。

三星HBM3E 12H采用了先进的热压非导电薄膜(TC NCF)技术,使得12层和8层堆叠产品的高度保持一致。三星电子称,已经开始向客户提供该芯片的样品,并计划在2024年上半年批量生产HBM3E 12H产品。

美光科技也于日前宣布,已开始量产HBM3E,其24GB 8H HBM3E产品将供货给英伟达,并将应用于NVIDIA H200 Tensor Core GPU,该GPU将于2024年第二季度开始发货。美光HBM3E可提供超过1.2 TB/s内存带宽,与竞争产品相比功耗降低约30%。根据产品规划,美光还将推出超大容量36GB 12-Hi HBM3E堆叠。另有消息称SK海力士今年3月量产全球首款HBM3E存储器。

从进度上来看,三星的HBM3E的量产时间略晚于SK海力士和美光科技。但是今年HBM三大家的竞争已经全面转向HBM3E。那么产能也将是一个重要部署。三星电子此前表示,今年将把HBM供应能力保持在行业最高水平,将产能提升至去年的2.5倍,以满足对人工智能芯片不断增长的需求。

SK海力士也同样做好了提升HBM产能的准备。SK海力士2024 年计划投资超过 10 亿美元,扩大在韩国的测试和封装能力。SK海力士负责封装开发的李康旭副社长(Lee Kang-Wook)表示,SK海力士正在将大部分新投资投入到推进MR-MUF和TSV(硅通孔)技术中。

-

DRAM

+关注

关注

41文章

2403浏览量

189581 -

HBM

+关注

关注

2文章

434浏览量

15884 -

三星

+关注

关注

1文章

1782浏览量

34454 -

HBM3

+关注

关注

0文章

75浏览量

510 -

HBM芯片

+关注

关注

0文章

7浏览量

124

发布评论请先 登录

SMT 量产工艺指南:铂芯片传感器回流焊、焊盘设计与良率提升

消息称英伟达HBM4订单两家七三分,独缺这一家

三星2nm良率提升至50%,2027年前实现晶圆代工业务盈利可期

三星发布Exynos 2600,全球首款2nm SoC,NPU性能提升113%

三星公布首批2纳米芯片性能数据

传三星 HBM4 通过英伟达认证,量产在即

三星最新消息:三星将在美国工厂为苹果生产芯片 三星和海力士不会被征收100%关税

曝三星S26拿到全球2nm芯片首发权 三星获特斯拉千亿芯片代工大单

突破堆叠瓶颈:三星电子拟于16层HBM导入混合键合技术

英伟达认证推迟,但三星HBM3E有了新进展

三星电子全力推进2纳米制程,力争在2025年内实现良率70%

受困于良率?三星否认HBM芯片生产采用MR-MUF工艺

受困于良率?三星否认HBM芯片生产采用MR-MUF工艺

评论