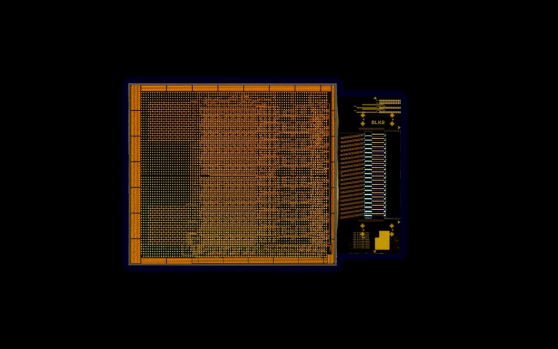

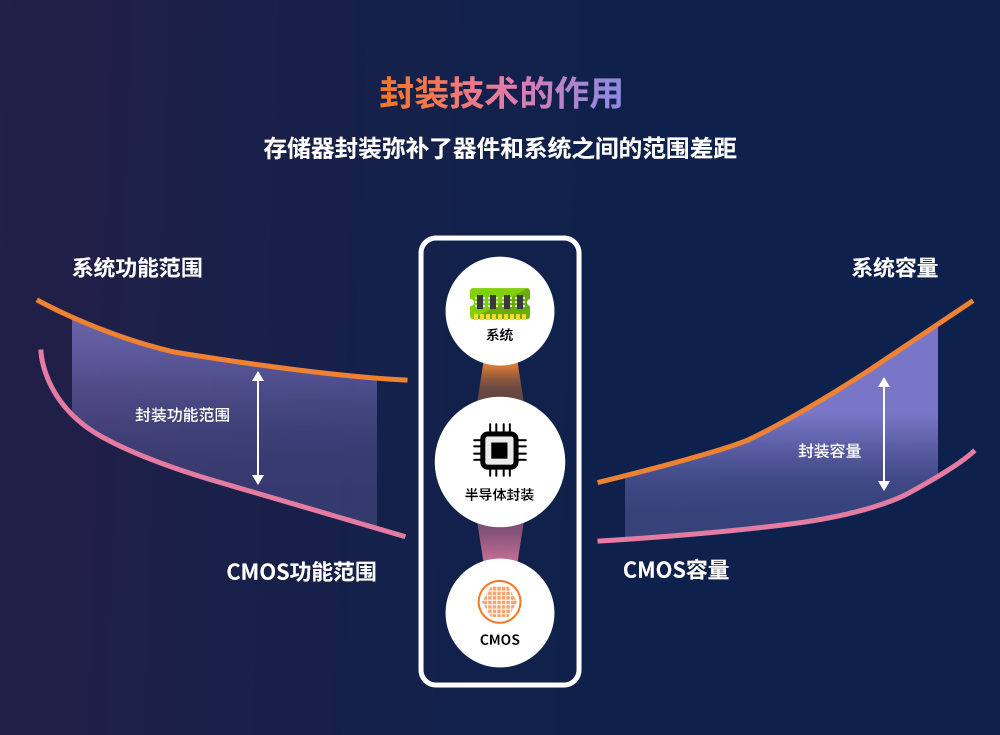

近日,业界领先的电子设计自动化解决方案提供商Cadence宣布与Intel代工厂达成重要合作,共同开发并验证了一项集成的先进封装流程。这一流程将利用嵌入式多晶粒互连桥接(EMIB)技术,有效应对异构集成多芯粒架构日益增长的复杂性,为高性能计算(HPC)、人工智能和移动设备计算等领域的设计空间带来革命性的进步。

EMIB技术作为此次合作的核心,为设计团队提供了一种创新的解决方案,使得从早期系统级规划、优化和分析能够无缝过渡到DRC实现和物理签核,而无需进行数据格式的转换。这一技术的引入,不仅简化了设计流程,还大大提高了设计效率,为设计团队节省了大量宝贵的时间和资源。

Cadence与Intel代工厂的此次合作,意味着Intel的客户将能够充分利用这一先进的封装技术,加速其在高性能计算、人工智能和移动设备计算等领域的设计创新。通过采用EMIB技术,设计团队将能够更好地应对多芯粒架构的复杂性,实现更高效的芯片集成和更出色的性能表现。

此外,这一先进的封装流程还将有助于缩短复杂多芯粒封装的设计周期。在过去,由于数据格式的转换和流程的不连贯,设计团队往往需要花费大量时间在数据转换和流程衔接上。而现在,通过Cadence与Intel代工厂的合作,设计团队将能够直接利用EMIB技术,实现从系统级规划到物理签核的无缝过渡,从而大大缩短设计周期,提高设计效率。

-

Cadence

+关注

关注

64文章

915浏览量

141849 -

intel

+关注

关注

19文章

3480浏览量

185730 -

先进封装

+关注

关注

1文章

370浏览量

220

发布评论请先 登录

相关推荐

强势入局芯粒技术链 东方晶源PanSys产品重磅发布

新思科技针对主要代工厂提供丰富多样的UCIe IP解决方案

英特尔OCI芯粒在新兴AI基础设施中实现光学I/O(输入/输出)共封装

日本Rapidus携手IBM深化合作,共同进军2nm芯片封装技术

Rapidus与IBM深化合作,共推2nm制程后端技术

2024年最新全球EMS代工厂50强(TOP 50)

Cadence与Intel代工厂携手革新封装技术,共推异构集成多芯粒架构发展

Cadence与Intel代工厂携手革新封装技术,共推异构集成多芯粒架构发展

评论