FPGA仿真是一种验证FPGA设计正确性的过程,主要用来分析设计电路逻辑关系的正确性。在FPGA设计中,仿真测试是把FPGA当作一个功能芯片,给一些输入信号,再观测输出信号,看输出信号是不是设计者想要的信号。这个过程由专门的软件完成。

FPGA仿真主要分为功能仿真和时序仿真两类。功能仿真(也称为RTL级行为仿真或前仿真)是在设计实现前对所创建的逻辑进行验证,分析其功能是否正确。布局布线以前的仿真都称作功能仿真,它包括综合前仿真和综合后仿真。综合前仿真主要针对基于原理框图的设计,而综合后仿真既适合原理图设计,也适合基于HDL语言的设计。功能仿真不带有任何的门延时、线延时等,只是理想情况下的仿真,但它的仿真速度快,可以根据需要观察电路输入输出端口和电路内部任一信号和寄存器的波形。

时序仿真则是使用布局布线后器件给出的模块和连线的延时信息,在最坏的情况下对电路的行为作出实际地估价。

总的来说,FPGA仿真在FPGA设计和验证过程中扮演着重要的角色,有助于确保设计的正确性和可靠性。

-

FPGA

+关注

关注

1632文章

21816浏览量

606988 -

芯片

+关注

关注

458文章

51419浏览量

428618 -

仿真

+关注

关注

50文章

4136浏览量

134174

发布评论请先 登录

相关推荐

FPGA核心知识详解(3):那些让FPGA初学者纠结的仿真

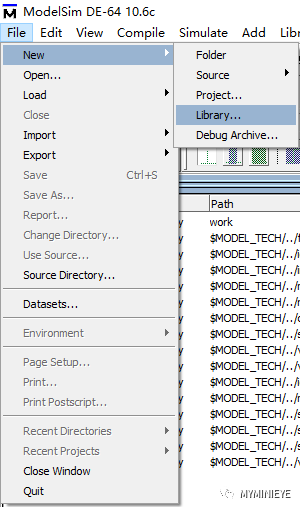

FPGA开发:modelsim仿真流程及波形

fpga仿真是什么

fpga仿真是什么

评论