FPGA(现场可编程门阵列)芯片中的触发器是一种重要的存储元件,它在数字电路设计中起着至关重要的作用。触发器的主要功能是存储和同步数字信号,确保电路在正确的时刻捕获和保持信号状态。

首先,从定义上来说,触发器是一种存储元素,它可以在时钟信号的边沿触发时捕获和存储输入信号的状态。这意味着触发器能够记住某个特定时间点的信号值,并在需要时将其输出。这种特性使得触发器在数字信号处理、时序控制以及状态机实现等应用中非常有用。

其次,触发器在FPGA中的用处广泛而多样。在时序电路设计中,触发器用于实现时序控制,确保电路的稳定性和可靠性。它们可以帮助设计师精确控制信号的传输和存储时间,从而实现复杂的逻辑功能。此外,触发器还可以作为寄存器的组成部分,用于存储数据以备后续处理。

再者,FPGA中的触发器类型多样,每种类型都有其特定的应用场景。例如,D触发器(Data Trigger)通常用于数据的存储与传输;T触发器(Toggle Trigger)可以在时钟信号的上升沿或下降沿改变其输出状态;而JK触发器(Jack Kilby Trigger)则具有更复杂的逻辑功能,可以在时钟信号的边沿根据输入信号的状态改变其输出。

最后,值得一提的是,触发器与寄存器虽然都是FPGA中的存储元件,但它们的功能和应用场景有所不同。触发器主要用于同步存储,而寄存器则可以通过时序组合逻辑实现状态的存储和更新,无需时钟信号的触发。因此,在FPGA设计中,触发器通常用于需要保持存储数据以备下一次计算使用的场景,如数字滤波器、状态机等。

综上所述,FPGA芯片中的触发器是一种关键的存储元件,具有广泛的应用场景和重要作用。它们不仅能够帮助实现复杂的逻辑功能,还可以提高数字电路的稳定性和可靠性。

-

FPGA

+关注

关注

1638文章

21856浏览量

609434 -

芯片

+关注

关注

459文章

51698浏览量

430696 -

触发器

+关注

关注

14文章

2027浏览量

61575

发布评论请先 登录

相关推荐

什么是触发器 触发器的工作原理及作用

jk触发器设计d触发器

施密特触发器,施密特触发器是什么意思

基于CPLD的触发器功能的模拟实现

施密特触发器芯片有哪些_施密特触发器的特点及作用

Virtex-7 FPGA系列的片式触发器资源

FPGA设计的D触发器与亚稳态

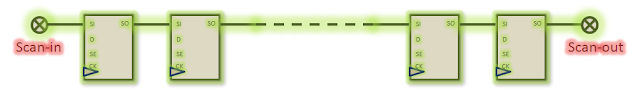

普通触发器如何转换为扫描触发器

FPGA芯片中的触发器是什么?它有哪些用处?

FPGA芯片中的触发器是什么?它有哪些用处?

评论