因为我有相关经验,解释一下令人惊叹的地方。

焊接挑战:

其实对于熟练焊工,焊点不良率控制在1ppm以下倒不是那么令人惊讶(对于一千个焊点的产品,1ppm的焊点缺陷意味着产品缺陷率为千分之一),如果采用有铅焊锡,并不是很难。当然,用无铅焊锡(环保要求,现在正式工厂不让用有铅焊锡)难度会比有铅很高很多。但是个人制作,不需要用无铅焊锡,所以难度大大下降。

对于错件,原因有两个,图纸错误,插件错误。前者可以靠仿真解决,电路图对了,那么插件图也就可以正确。后者靠细心同检查了,也能解决。

最容易错的不是错件,而是错线。

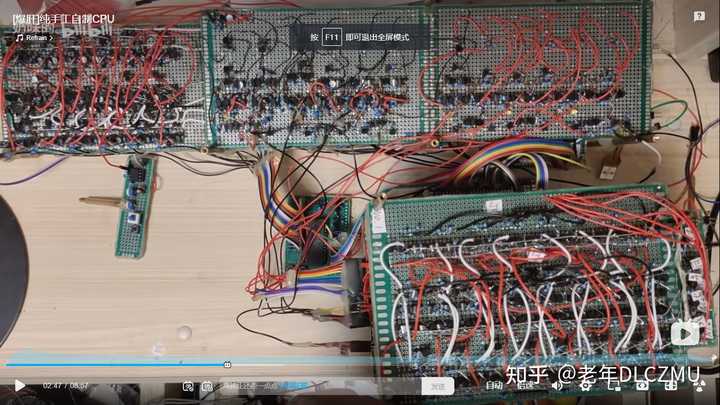

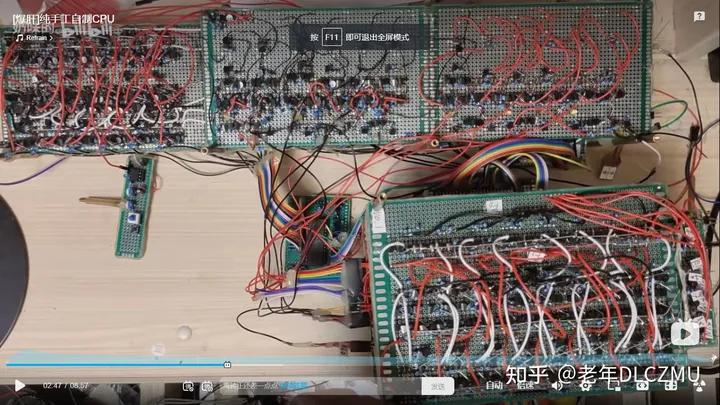

因为从视频中走线看,UP主不用线束,而是散线,所以很难画走线图。

用线束容易有干扰,除非用屏蔽线。我在90年代做高灵敏度磁头放大器、高灵敏度电唱头放大器的时候,曾经面临严峻的信号串扰的挑战。

所以,在各种原型的制作中,有时候为了降低干扰,要求走线很短很紧凑,确实不好用线束。

但是,不用线束不好画走线图,没有走线图的画,这么多焊线太容易眼花导致出错了。

当然,我们可以彩线来防止错线的。彩线种类太多,除了各种单色线(红橙黄绿青蓝色黑白),还有组合花色线(红绿花、黑白花、红白花、绿白花、橙白花。。。。)可以很好的解决这个问题。

这种彩线某宝上可以很方便的购买,一排排的彩排线,不是很贵。

更不可思议的是,从视频中看,该UP主主要用单色线。

其实该UP是有买彩排线,但是从视频中看,该UP主仅仅是当顺序接线用,而不是当乱序接线用。

其实彩排线如果作为顺序线用,相比单色排线优势不大,其优势主要是在乱序接线中。

UP主不知是没有经验,还是自信,居然在乱序接线中用的单色线,而不是用彩线。

干扰挑战:

1、这东西如果想像ENIAC那样工作的话,必须模块化设计,另外,必须解决信号窜扰的问题。

ENICA是用电子管做的,早年的电子管信号的上升沿跟下降沿都很缓慢,并且工作频率仅仅大概是5K左右,串扰不是很严重。

而现在的三极管开关性能远远强于以前的电子管,上升沿跟下降沿都很陡峭,会有严重的高次谐波成分。

如果用现在的三极管,为了让上升沿下降沿变得缓慢,需要用电容滤波。

未见措施:

视频中导线仅仅是裸线而不是屏蔽线,更要命的是这些线都离得很近。

大家别看到有别的设备线离得很近就照抄照搬。

如果是加了驱动的输出信号,因为源阻抗低,对于数字电路来说,并不容易到干扰。

注意,必须是双向低阻,推挽电路(比如CMOS)必须上拉或者下拉,共源电路漏极开路或者共射电路集电极开路接上拉电阻的不行,除非上拉电阻很小(很小的上拉电阻又会造成很大的电流)

但是如果是输入信号,因为阻抗高,哪怕是数字电路,当其他信号快速变化时,假如电平上升或者下降的速度过快,该输入端会收到其他信号上升沿同下降沿的信号,从而产生毛刺。

这些信号毛刺通过电容、施密特电路等等措施处理掉之后,不会影响后面的逻辑。

元件太少:

但是,UP完全没提到施密特电路同电容。实际上从UP说的元件数量,其集成度也不支持做那么多施密特电路。

地弹挑战

很明显,该UP主用的电路不是现在流行的差分电路,而是单端信号电路。(不学电子很多年了,忘了怎么叫了,大家明白意思就行了)

现在大家都用差分电路,所以这个问题可能已经很难碰到了。

单端信号电路有个重大的问题很难解决,该UP主居然提都没提。

这个问题就是地弹问题(rebound,我不知中文怎么讲,我学电子的时候,国内没这个概念。这个概念是90年代跟老外学的。地弹这是我自己的翻译)。

地弹原理:

在非射频电路中,需要形成回路才能形成电流。在单端信号中,从信号线流出去,从地线流回来。

主要,地线可不是大家画原理图中理想的地线。原理图中的地线是没有电抗的(包括电阻、电感)的,实际的地线是有电抗的。信号“流出”的时候,经过地线会产生压降。

本来这不是问题,信号“流出”的时候,也会在信号线上产生压降。数字电路容限大,给数字电路设置合适的阈值就行了,不会是问题。

但是,对于单端信号来说,地线是公用的,这就要了命了,多个信号都会地线上产生压降,这个压降等于瞬时电流x电抗。

对于输入端来说,输入的信号是输出的信号叠加上地线的电压。因为信号众多,信号输入端产生复杂的叠加,产生干扰。

因为集肤效应,导体电感等等因素,频率越高,电抗越大,所以地弹越严重,干扰越严重。

所以,这个也会在输入信号中形成毛刺。并且这个毛刺没经验的人很难发觉(因为你测试的时候,你测到信号是基于参考点的,测到什么信号,取决于你的参考点)

有两种方法可以改善这个问题。

1、合适的防止退耦电容来短路信号回路、

2、大面积敷铜来降低电抗(所谓接地层).

在该三极管CPU视频发布之后一个月,另外有个UP主上传了一个用门电路手搓CPU的视频中,我看到相关的UP采用了这种方法来处理

在本三极管CPU的视频中,我看不到相关措施。

频率挑战:

因为该CPU有如此长的线,信号在这些线上传输会产生复杂的延时、干扰,所以频率不能过高。

做个参照,

@温戈

回答(见文末链接)中提到的ENICA,我记得是5KHz。

该CPU虽然尺寸明显更小,但是设计,工艺明显更差,我觉得很难超过ENICA的工作频率。

再找另外一个参照Intel 4004,这是是英特尔制造的一款微处理器,片内集成了2250个晶体管,晶体管之间的距离是10微米,能够处理4bit的数据,每秒运算6万次,频率为108KHZ,前端总线为0.74MHz(4bit)。4004的最高频率有740kHz,能执行4位运算,支持8位指令集及12位地址集

有人回答说说该CPU的工作频率是“100KHz左右“,我是不太信的。

在视频中这种工艺、设计的水平下,我非常惊讶达到这种频率。

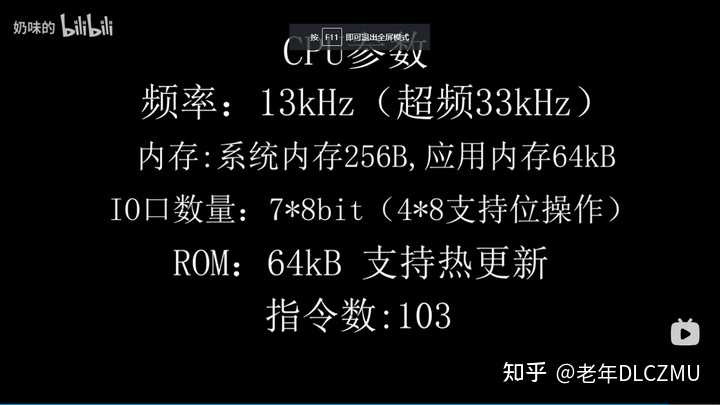

原UP主在另外一个视频中说频率是13KHz,更合乎逻辑。

内存挑战:

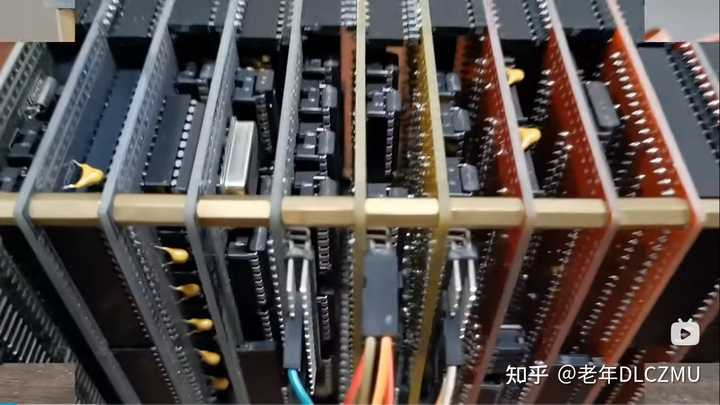

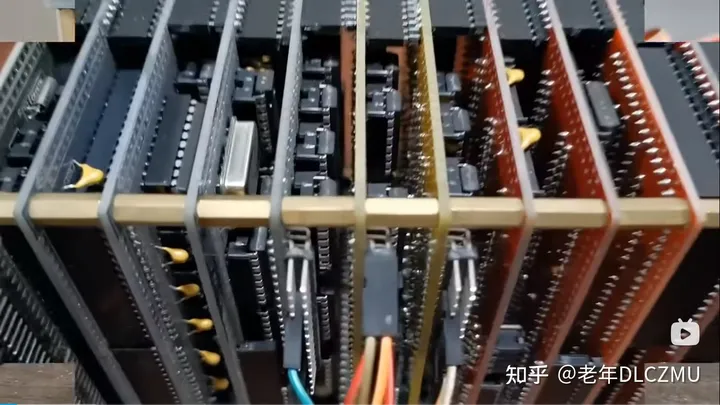

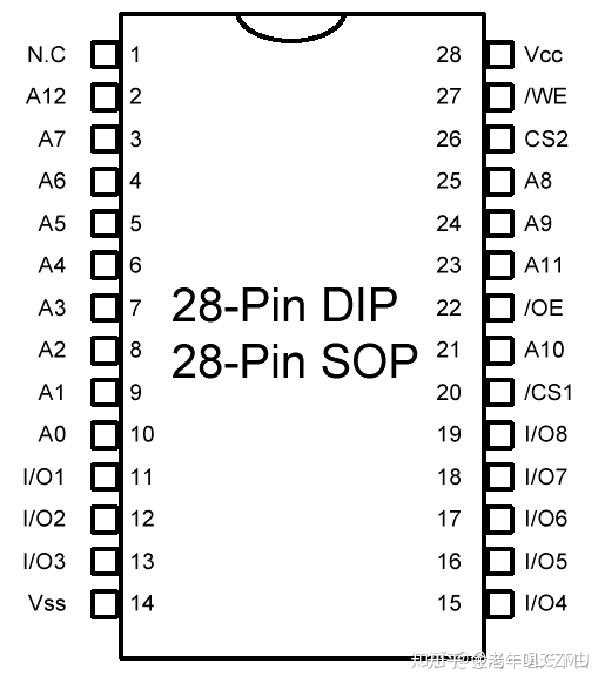

手搓CPU,我直觉上最多用8KB(64Kbit)的HM6264(如下图) 8K*8bit,

芯片图来自文献2, 但原文献所说2V电压不对,100ns,50/100uA, 55mA 4.5V 至 5.5V,通过使用两个芯片使能输入(/CE1、CE2)和低电平有效输出使能 (/OE),

这种RAM不像后来的FP DRAM(Fast Page RRAM)同EDO DRAM(ExtendedDateOut DRAM),是没有地址锁存功能,所以不分行地址、列地址,容量每扩大一倍,就要多一条地址线。

但是很多回答引用的文章说该UP主直接上了512KB的HM628512,当然,这个问题不是很大,多出来的A线直接短接置0或者置1都行。

注意,HM628512的数据位宽是8位的512KB SRAM,该UP主视频写的是64KB.

注意,我们说的英特尔4004、8008等等早期低集成度的CPU是不带内存控制器的。

4位 Intel 4004 微处理器仅仅是 4 芯片组的一部分,这个被称为 Intel MCS-4 的 4 芯片组包括微处理器、ROM、RAM 和用于 I/O 扩展的移位寄存器

代码挑战:

注意,很多答主引用的文章HM628512是ROM,我没看懂。这个ROM做什么用?

ROM要求掉电后数据依然存在,HM628512掉电后数据就没了,这点我没看懂。

从手扣代码的视频来看,代码部分像是用一大堆的拨动开关实现的,

规模挑战:

4004的CPU是2250个晶体管,4位机。

最早的8位微处理器8008是3500 个晶体管,8008可以支援到16KB的内存。

对应的 CTC 8 位板级处理器,内置约 100 个 SSI (Small-scale-integration小规模集成电路)和 MSI(Middle-scale-integration中规模集成电路) TTL 芯片

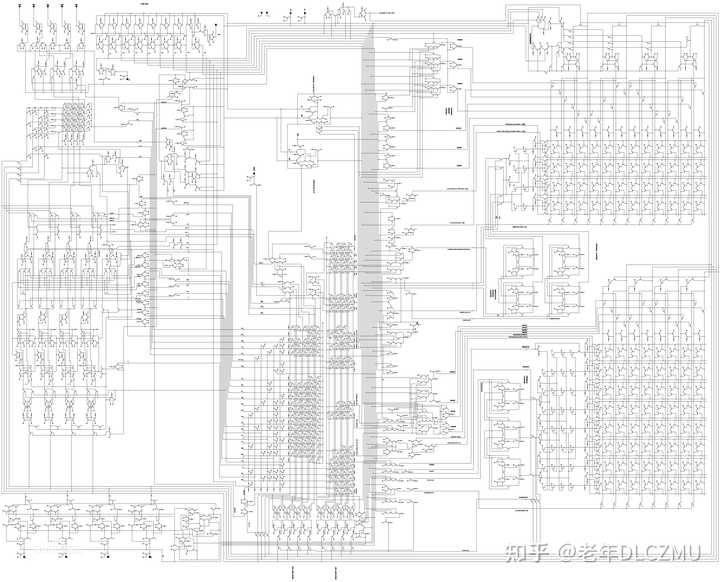

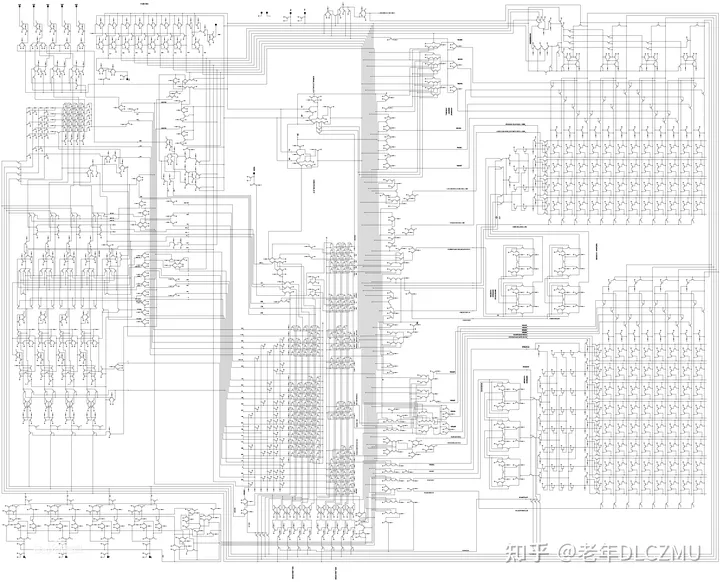

本三极管CPU做的是8位机,1000多个三极管、2000多个二极管,电阻数量2000多,直觉上感觉元器件数量不够。

不过,很多门电路如果用三极管实现,可以简单化,比如一个与非门,可以直接用两个二极管加一个三极管做共射电路实现。但是,会产生我前面提到的问题。

而从原视频中看相关工艺,又似乎并未尝试去解决这些问题。

不知道熟悉电路的

@朱玉龙

大神,

@invalid s

有啥感想。

我的隐忧:

从工艺的角度看,用门电路手搓CPU我倒还是相信,我早年接触的IBM XT的主板上也全是74系列门电路来实现内存控制,IO转换,工艺上没有太大的问题。

并且,那个手搓门电路CPU的UP主还把各种设计文件开源了。

用三极管手搓CPU,也不是不可能,只是我觉得工艺上要非常小心。

看了三极管CPU的视频同大家回答中转载的介绍,因为没有看到其设计文件,总是难以置信。

这感觉就像看到有人手搓迷你版的运载火箭一样。

运载火箭都变成迷你版了,当然也不是不能手搓。但是看到这个迷你版的运载火箭,用的是便宜的水洗煤,这个我就惊讶了。

所以,我一直想排除一种可能:

该三极管CPU最终制作失败了,作者被折腾得精疲力竭,但是又不想白忙,毕竟亚历山大大帝当年也是一剑劈开了Gordian knot。传说:戈尔迪乌斯国王打了一个十分难解的结,即戈尔迪之结(Gordian knot),并称谁能解开便会成为亚洲的统治者,结果亚历山大大帝大刀一挥挥剑将结斩断。

于是:

1、因为纯粹驱动LED对逻辑的准确性没有太严格要求,错了对显示结果的影响也不明显,所以改成了一排排LED的驱动电路,然后用单片机实现了相关功能。

2、因为做流水灯不需CPU,可以用双稳态加延时等等很多方法实现,原作者最后仅仅做了流水灯的一套实现电路

然后作者拍了视频上传说是CPU成功了。

后话:

原UP主花了两年时间做这个奇迹工程,其心血同汗水值得尊重。并且,他在板上安置了大量LED(发光二极管)看起来也像是为了方便查找问题(其实,这种情况下,用发光二极管取代普通二极管是一种很好的调试方法)。

如果该CPU确实其实没有正常运行,我希望它能够早日正常运行。

如果该CPU确实运行正常了,我希望看到更多设计详情以满(da)足(xiao)好(yi)奇(wen)心。

作者:老年DLCZMU

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

审核编辑 黄宇

-

led

+关注

关注

242文章

23235浏览量

660473 -

晶体管

+关注

关注

77文章

9679浏览量

138050 -

中央处理器

+关注

关注

1文章

124浏览量

16515

发布评论请先 登录

相关推荐

什么是中央处理器

中央处理器cpu性能排名

CPU中央处理器操作原理及应用

B 站焊武帝爆火出圈:纯手工拼晶体管自制 CPU,耗时半年,可跑程序

如何看待视频博主耗时半年时间纯手工拼晶体管自制成功中央处理器(CPU)?

如何看待视频博主耗时半年时间纯手工拼晶体管自制成功中央处理器(CPU)?

评论