开发 3D-IC 的传热模型,有助于在设计和开发的早期阶段应对热管理方面的挑战。

开发 3D-IC 传热模型主要采用两种技术:分析法和数值计算法。

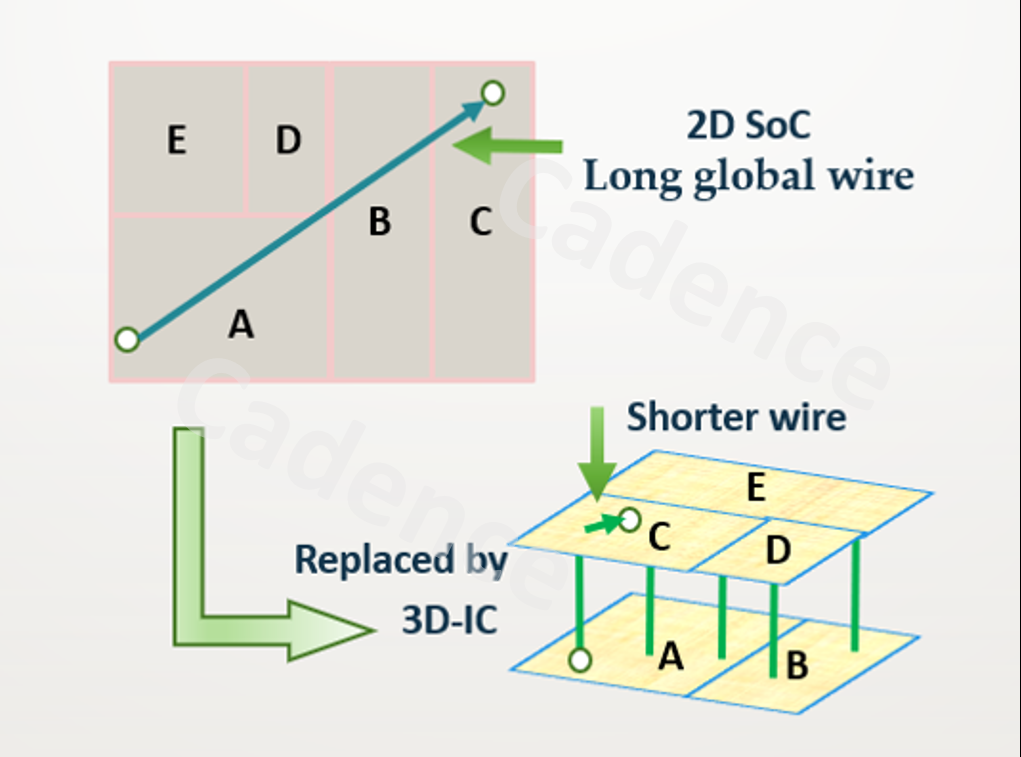

传统的单裸片平面集成电路 (IC) 设计无法满足电子市场对高功率密度、高带宽和低功耗产品的要求。三维 (3D) 集成电路技术将多个芯片垂直堆叠,实现电气互连,具有更出众的优势。3D-IC 电路外形小巧,集成度更高、信号延迟更低,支持异构集成,这些先进的功能使之具有出色的电气性能。

3D-IC 设计的电能耗散水平和热密度较高,这为热管理带来了严峻的挑战。

然而,3D-IC 设计的电能耗散水平和热密度较高,这为热管理带来了严峻的挑战。为了克服 3D-IC 在热管理方面的限制,3D-IC 传热模型应运而生。3D-IC 传热模型有助于开发新的封装工艺。本文将讨论 3D-IC 及其传热模型。

01

3D-IC 技术

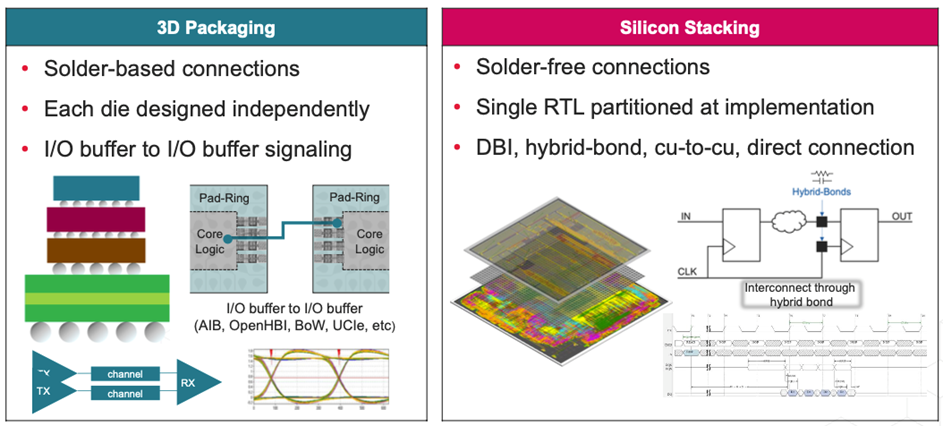

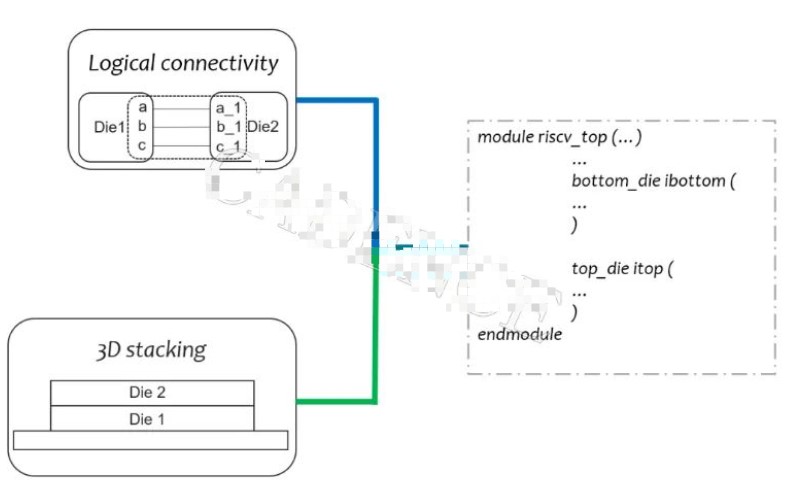

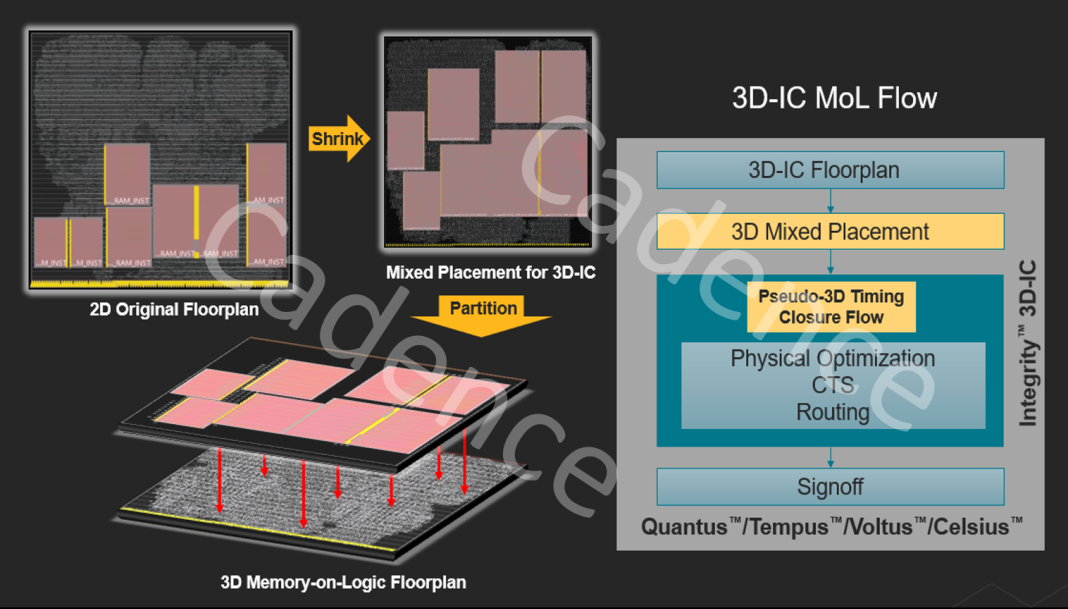

缩小集成电路的总面积是 3D-IC 技术的主要目标。3D-IC 的设计方法是垂直堆叠传统器件层或芯片,这些层和芯片之间实现了电气互连。3D-IC 技术提高了集成器件的功能、性能和封装密度。该技术能够减少信号延迟,提高片上通信速度。在 3D-IC 封装中,逻辑芯片和存储芯片之间的互连变得更短,从而提高了信号传输速度。3D-IC 的垂直集成密度和异构集成度更高,与系统级单芯片和层叠封装等替代方案相比更具优势。3D-IC 的集成方式可以是面对面集成,也可以是背对背集成。

3D-IC 可分为两类

1

3D 堆叠 IC

堆叠 IC 芯片并使用硅通孔 (TSV) 实现芯片互连。TSV 是制造 3D 堆叠 IC 的基本元素。通过 TVS 蚀刻过程钻出一个个孔,在其中填充钨、铜或多晶硅等导电材料。TSV 互连缩短了各层和芯片之间的路径,从而提高了互连密度,同时降低了功耗。

2

真正的 3D-IC

使用晶圆厂工艺在单个芯片上堆叠多个器件层。这种集成电路非常适合在既定的 footprint 区域集成更多晶体管。该技术有助于在最先进的节点上克服单裸片的限制。

02

3D-IC 的优势

1

设计成本低

在 3D-IC 中,所有功能都无需转移到先进的工艺节点,因此降低了设计成本。

2

易于实现高速传输

3D-IC 技术的互连长度更短,从而减少了信号延迟,有助于实现高速通信和传输。

3

电路微型化

层层堆叠有助于在 3D-IC 中集成大量晶体管。晶体管的密集化节省了空间,因此 3D-IC 非常适合紧凑型设备。

4

功耗低

3D-IC 不需要使用高功耗驱动器。相反,它们依赖低功耗的小型输入输出驱动器。3D-IC 的阻抗较低,这一点也有助于减少内部功率损耗。

5

带宽更高

3D-IC 可以提供更高的带宽特性。在 3D-IC 技术中,在处理器顶部堆叠高速缓冲存储器可增加带宽。

6

灵活

堆叠异构技术为 3D-IC 带来了灵活性。利用 3D-IC 中的异构集成技术,可以混合部署不同的制造处理器和节点。这有助于重新使用现有的芯片,而无需重新设计新的芯片,可无风险地降低成本。

03

3D-IC 技术中的传热模型

热管理是 3D-IC 技术面临的最大障碍之一。为了在既定的 footprint 内实现较高的功率密度,需要将器件层堆叠在一起。堆叠层的 footprint 是固定的,通电后会造成发热现象。复杂的结构再加上集成度高,增加了散热量和热密度。3D 堆叠 IC 技术本身就有温度过高的特点,会在 3D-IC 集成中引发灾难性故障。

要使 3D-IC 有效工作,就必须采取适当的散热措施。传统的空气散热方式不足以满足 3D-IC 的要求,需要设计复杂的热管理系统来动态控制 3D-IC 的温度。开发 3D-IC 的传热模型,有助于在设计和开发的早期阶段应对热管理方面的挑战。3D-IC 的传热模型可以解答基本的传热问题,要成功实施 3D-IC 技术,弄清楚这些问题非常重要。

3D-IC 传热模型可用于分析 3D-IC 设计热管理的限制。该模型可充当一种辅助工具,用于针对 IC 冷却和封装方式实施合适的热管理方法,以适应 3D-IC 的散热需要。

用于开发 3D-IC 传热模型的技术主要有两种

1

分析法

分析传热模型,通过求解能量守恒方程和边界条件得出 3D-IC 结构的温度场。该方法可用于研究各种几何和热物理参数对 3D-IC 散热性能的影响。

1

数值计算法

当 3D-IC 具有复杂的结构和与温度相关的特性时,就很难推导出传热方程的精确解。在这种情况下,可对几何体进行离散化处理,求出方程的近似解,以此建立数值计算传热模型。数值计算法能够以可接受的准确度预测温度。

3D-IC 的传热模型可以确定结点温度和内部结构的峰值温度。传热模型还能确定 3D-IC 结构中的热点,帮助工程师设计有效的热管理技术。

视频使用 Celsius Thermal Solver 软件,基于先进3D结构中的实际电能流动执行静态(稳态)和动态(暂态)电热仿真,最大程度地模拟真实系统的行为。

Cadence 软件可以生成传热模型,用于确定每个裸片的温度分布。Celsius Thermal Solver 提供完整的电热协同仿真解决方案,同时满足电子和机械工程师的热分析需求,且适用于从 IC 到实体封装机壳的所有电子系统层级。

-

集成电路

+关注

关注

5387文章

11510浏览量

361538 -

IC

+关注

关注

36文章

5939浏览量

175446 -

3D

+关注

关注

9文章

2872浏览量

107456 -

热模型

+关注

关注

0文章

6浏览量

6961

发布评论请先 登录

相关推荐

如何建立正确的3D-IC设计实现流程和实现项目高效管理的挑战

3D-IC设计之系统级版图原理图一致性检查

Cadence 凭借突破性的 Integrity 3D-IC 平台加速系统创新

新思科技推出3D-IC新技术

Cadence发布突破性新产品 Integrity 3D-IC平台,加速系统创新

Cadence Integrity 3D-IC平台Ô支持TSMC 3DFabric技术,推进多Chiplet设计

Cadence Integrity 3D-IC平台进行工艺认证

Integrity™3D-IC平台助力设计者实现驱动PPA目标

Cadence Integrity 3D-IC自动布线解决方案

3D-IC未来已来

产品资讯 | 3D-IC 设计之自底向上实现流程与高效数据管理

3D-IC 以及传热模型的重要性

3D-IC 以及传热模型的重要性

评论