随着电子技术的进步.FPGA逻辑电路能完成的功能越来越多,同样也带来了一个很大的问题,即逻辑电路的规模越来越大,这意味着RTL代码到FPGA的映射、布局布线所花费的时间也越来越长。

如果代码结构不合理,编写随意,没有考虑到FPGA布局布线的可行性以及时序收敛的问题,那么很可能使时序收敛非常困难,更坏的情况是布局布线失败(即place and route fail)。这种情况在大规模的设计、大规模的FPGA上更为常见,因此有必要专门有一个章来讲RTL代码的设计、电路结构的设计、大规模逻辑电路的技巧以及如何解决此类问题。

布局布线失败

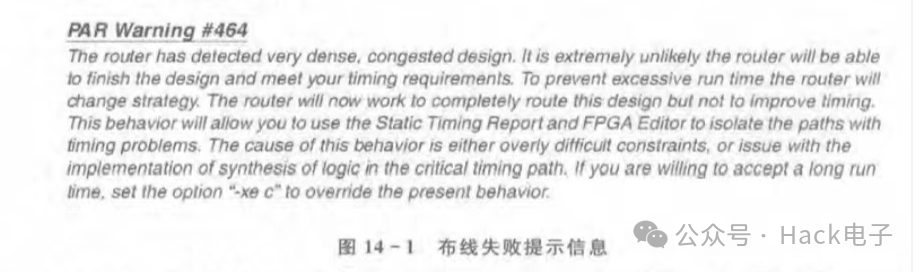

在某些FPGA中,特别是在大规模的FPGA(XilinxVirtex6以上,AlteraStratixIV以上)中实现大规模的设计,如果前期没有对设计的逻辑电路做好结构优化,同时不注意代码风格,那么很可能会带来一个问题:布局布线失败。这种现象困扰着设计者因为一个大型的设计从综合到布局布线通常需要花费十来个小时,有些甚至是一两天的时间,而这种结果意味着这些时间将被极大地浪费。该现象一般在FPGA工具中会出现如图14-1所示的信息。

图14-1 布线失败提示信息

图14-1的大体意思是说布线工具(router)检测到当前是一个非常密集(dense)拥塞(congested)的设计,布线工具有可能没有办法实现布线。这里的密集和拥塞是指什么呢?从字面上意思理解就是FPGA布线工具在进行布线的时候,发现设计的某些部分在布局后器件之间的分布过于密集,连线过于复杂,因此无法完成布线。

这跟PCB的设计有点类似,当PCB的布局不合理或者器件过多的时候,有可能在指定的面积下无法完成布线,只能通过增加PCB面积或者层数来完成。

那么对于FPGA来说到了设计能够布局布线阶段,这已经是一个中期的阶段,此时要重新选型不现实;另外如果FPGA本身已经是最大规模,那么更换FPGA更是不可能。这种情况跟时序不收敛要恶劣得多。

因此,在这个时候,设计者通常面临两种选择:

①删除部分设计需求,除低设计占用的FPGA资源;

②优化逻辑电路的实现架构、代码。

对于第一种选择,设计变更太大,造成的影响太多,而且降低FPGA资源利用率后也不能保证能够布线成功第二种选择是一个比较艰难的选择,这意味着很可能要对前期已经仿真验证好的代码进行大量修改和优化,在进行布局布线测试的过程中又重新仿真验证。

这是一个比较麻烦的过程,但是,这也印证了前期设计规划的重要性,即要求设计者在前期就能够预见到该设计可能遇到的问题,在做逻辑电路架构和编码的时候注意到这种潜在的危险,争取在概要设计和详细设计阶段就把该类风险考虑进去,编码的时候养成良好的编码风格和习惯,最大程度地减少该类事情的出现。

审核编辑:刘清

-

FPGA

+关注

关注

1629文章

21729浏览量

602998 -

逻辑电路

+关注

关注

13文章

494浏览量

42609 -

PCB设计

+关注

关注

394文章

4683浏览量

85547

原文标题:FPGA布局布线失败怎么办(一)

文章出处:【微信号:Hack电子,微信公众号:Hack电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA去耦电容如何布局布线

FPGA的布局布线

FPGA布局布线的可行性 FPGA布局布线失败怎么办

FPGA布局布线的可行性 FPGA布局布线失败怎么办

评论