引 子

1958年9月12日,温和的巨人杰克•基尔比(Jack Kilby)发明了集成电路,当时没有人知道,这项发明会给人类世界带来如此大的改变。

42年后,基尔比因为发明集成电路获得了2000年诺贝尔物理学奖,“为现代信息技术奠定了基础”是诺奖给予基尔比的中肯评价。

科学技术的进步往往是由一连串梦想而推动的,集成电路自然也不例外。

基尔比这位身高两米,性格温和稳重的TI工程师的梦想就是:“用一种半导体材料来制作电路所需的所有器件”。集成电路发明7年后,Intel创始人戈登•摩尔提出了他的预言式梦想:“集成电路上的器件数量每隔十八个月将翻一番”,这就是我们今天所熟知的摩尔定律。

最终,他们都实现了自己的梦想,推动了科技的巨大进步。两个伟大的梦想叠加在一起,也造就了今天的半导体产业。

“所有的器件都可以在一个硅片上集成,器件数量将以指数方式增长”,这就是我对两个伟大的梦想的总结。

六十多年后的今天,整个集成电路产业的发展依然以它们为基石!

从同构到异构

事物的发展有其出现、发展、成熟、终结的过程,技术的发展也是如此。

基尔比认为,在一种材料上做出所有电路需要的器件才是电路微型化的出路,只需要一种半导体材料就能将所有电子器件集成起来,今天,我们称之为同构集成 Homogeneous integration。

在这篇文章里,我们重点讨论的则是另一个技术:异构集成 Heterogeneous integration。

首先,我们了解一下从同构到异构的发展过程。

从基尔比开始,人类就致力于在硅片上制作出电路所需要的所有器件,在摩尔定律的推动下,硅片上的器件数量以指数方式增长。今天,在一平方毫米的硅片上集成的器件数量可轻松超过一亿只,主流芯片都集成了百亿量级的晶体管。

同构集成技术的发展已经如此成熟,同样不可避免地会经历走向终结的过程,在同构集成逐渐成熟并难以再持续发展的过程中,人类必须寻找一种新的集成方式来延续,这就是异构集成。

异构集成中有一个重点概念我们需要理解,这就是Chiplet,Chiplet意为小芯片,就是将现有的大芯片切割成小芯片,然后再进行集成。

为什么要将大芯片切割成Chiplet?要回答这个问题,我们就需要了解Chiplet技术带来的三大技术趋势。

除了将大芯片切割为Chiplet后再进行集成,器件的数量也将不再以指数方式增长,也就是摩尔定律终将走向终结。

笔者认为:“器件将以多种方式集成,系统空间内的功能密度将持续增长”。

关于摩尔定律的终结、系统空间、功能密度定律等详细内容请参看作者著作《基于SiP技术的微系统》。

Chiplet技术

Chiplet顾名思义就是小芯片,我们可以把它想象成乐高积木的高科技版本。首先将复杂功能进行分解,然后开发出多种具有单一特定功能,可进行模块化组装的“小芯片”(Chiplet),如实现数据存储、计算、信号处理、数据流管理等功能,并以此为基础,建立一个“小芯片”的集成系统。

简单来说,Chiplet技术就是像搭积木一样,把一些预先生产好的实现特定功能的裸芯片(Chip)通过先进封装技术集成在一起形成一个系统级芯片,而这些基本的裸芯片就称为Chiplet。

Chiplet芯片可以使用更可靠和更便宜的技术制造,较小的硅片本身也不太容易产生制造缺陷。此外,Chiplet芯片也不需要采用同样的工艺,不同工艺生产制造的Chiplet可以通过SiP技术有机地结合在一起。

Chiplet技术的出现带来了芯片设计的新趋势,我们简单描述为:IP芯片化、集成异构化、IO增量化,简称三大技术趋势。

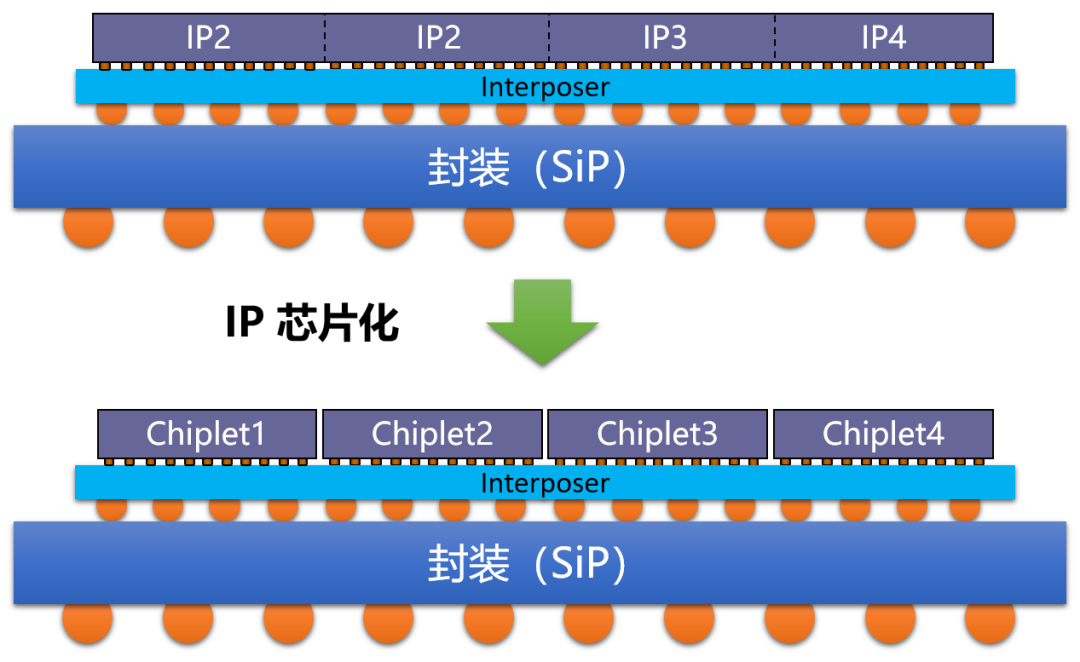

1.IP芯片化

IP(Intellectual Property)是具有知识产权内核的集成电路的总称,是经过反复验证过的、具有特定功能的宏模块,可以移植到不同的半导体工艺中。

到了SoC阶段,IP核设计已成为ASIC电路设计公司和FPGA提供商的重要任务,也是其实力的体现。对于芯片开发软件,其提供的IP核越丰富,用户的设计就越方便,其市场占用率就越高。目前,IP核已经变成SoC系统设计的基本单元,并作为独立设计成果被交换、转让和销售。

IP核对应描述功能行为的不同分为三类,即软核(Soft IP Core)、固核(Firm IP Core)和硬核(Hard IP Core)。

当IP硬核是以芯片的形式提供时,就变成了Chiplet。

我们可以这么理解:SiP中的Chiplet就对应于SoC中的IP硬核,Chiplet 是一种新的 IP 重用模式,就是硅片级别的IP重用。

设计一个SoC系统级芯片,以前的方法是从不同的 IP 供应商购买一些 IP,软核、固核或硬核,结合自研的模块,集成为一个 SoC,然后在某个芯片工艺节点上完成芯片设计和生产的完整流程。有了Chiplet以后,对于某些 IP,就不需要自己做设计和生产了,而只需要买别人实现好的硅片,然后在一个封装里集成起来,形成一个 SiP。

所以,Chiplet 可以看成是一种硬核形式的 IP,但它是以芯片的形式提供的。因此,我们称之为IP芯片化。

2. 集成异构化

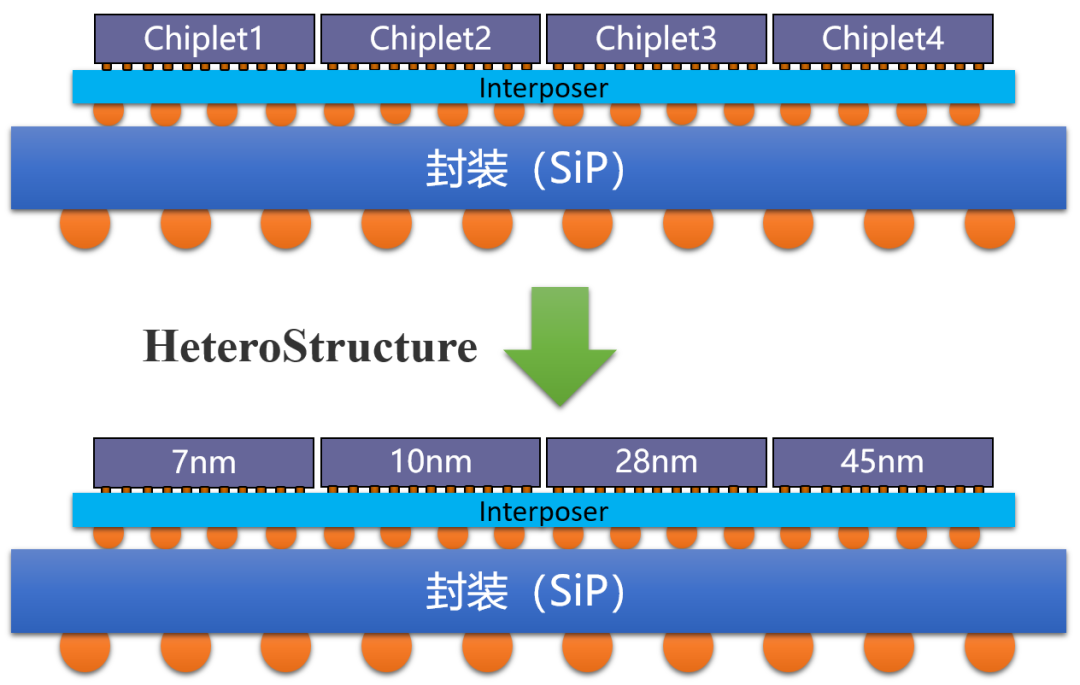

在半导体集成中,Heterogeneous 是异构异质的含义,在这里我们将其分为异构HeteroStructure和异质HeteroMaterial两个层次的含义。

HeteroStructureIntegration

在这篇文章中,异构集成HeteroStructure Integration主要指将多个不同工艺单独制造的芯片封装到一个封装内部,以增强功能性和提高工作性能,可以对采用不同工艺、不同功能、不同制造商制造的组件进行封装。

例如上图所示:将7nm、10nm、28nm、45nm的Chiplet通过异构集成技术封装在一起。

通过异构集成技术,工程师可以像搭积木一样,在芯片库里将不同工艺的Chiplet小芯片组装在一起。

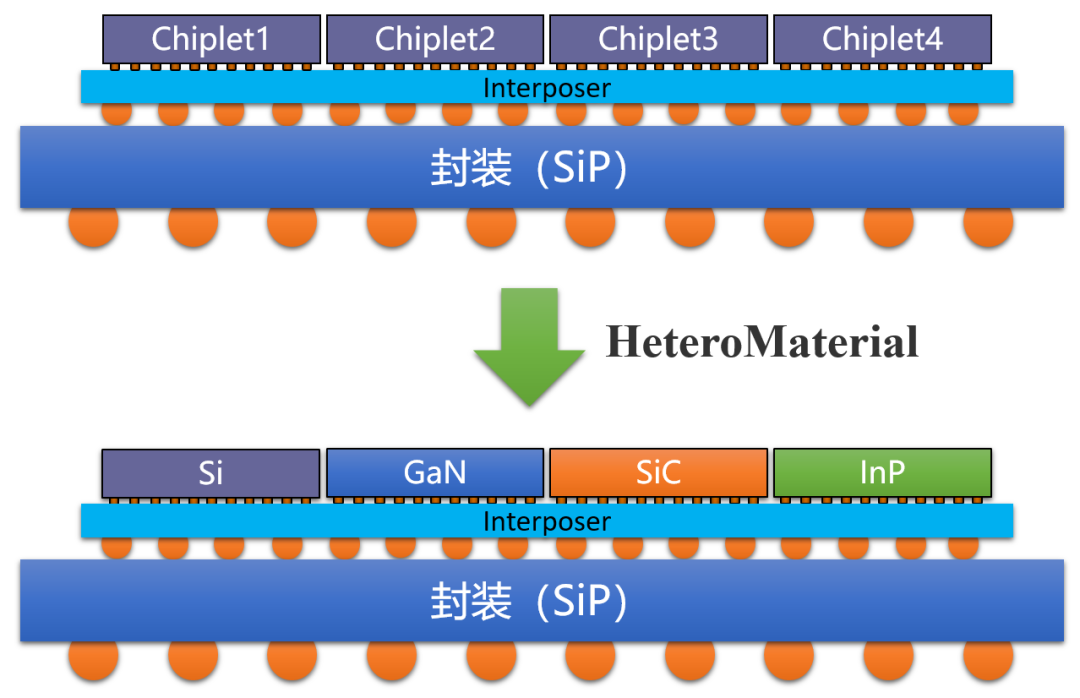

HeteroMaterial Integration

近年来集成硅(CMOS和BiCMOS)射频技术已经在功率上取得巨大的进步,同时也将频率扩展到了100GHz左右。然而还有众多应用只能使用像磷化铟(InP)和氮化镓(GaN)这样的化合物半导体技术才能实现。磷化铟能提供最大频率为1太赫兹的晶体管,具备高增益和高功率,以及超高速混合信号电路。而氮化镓能使器件具备大带宽、高击穿电压、以及高达100GHz的输出频率。

因此将不同材料的半导体集成为一体——即异质集成HeteroMaterial Integration,可产生尺寸小、经济性好、设计灵活性高、系统性能更佳的产品。

如下图所示,将Si、GaN、SiC、InP生产加工的Chiplet通过异质集成技术封装到一起,形成不同材料的半导体在同一款封装内协同工作的场景。

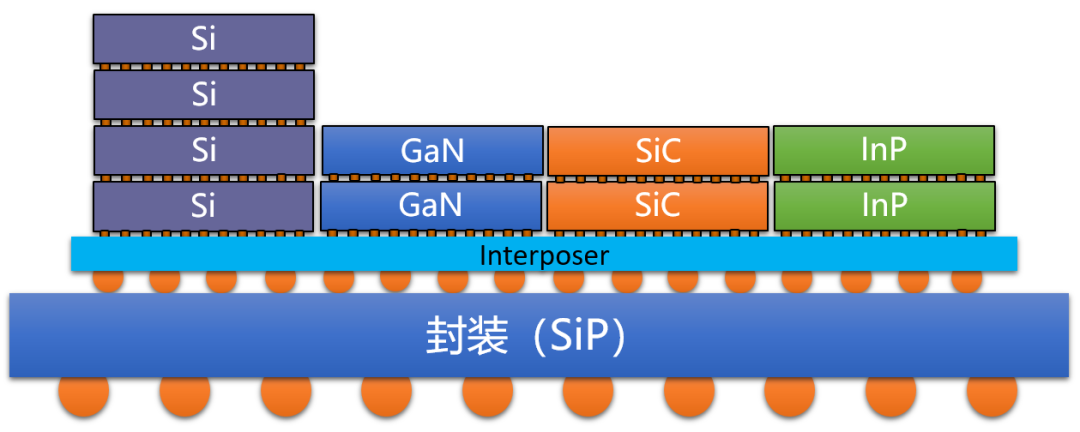

在单个衬底上横向集成不同材料的半导体器件(硅和化合物半导体)以及无源元件(包括滤波器和天线)等是Chiplet应用中比较常见的集成方式。

需要读者注意的是,目前不同材料的多芯片集成主要采用横向平铺的方式在基板上集成,对于纵向堆叠集成,则倾向于堆叠中的芯片采用同种材质,从而避免了由于热膨胀系统等参数的不一致而导致的产品可靠性降低,如下图所示。

3. IO增量化

如果说前面讲的是Chiplet技术的优势,那么,IO增量化则给Chiplet带来了挑战。

IO增量化体现在水平互联(RDL)的的增量化,同时也体现在垂直互联(TSV)的增量化。

在传统的封装设计中,IO数量一般控制在几百或者数千个,Bondwire工艺一般支持的IO数量最多数百个,当IO数量超过一千个时,多采用FlipChip工艺。在Chiplet设计中,IO数量有可能多达几十万个,为什么会有这么大的IO增量呢?

我们知道,一块PCB的对外接口通常不超过几十个,一款封装对外的接口为几百个到数千个,而在芯片内部,晶体管之间的互联数量则可能多达数十亿到数百亿个。越往芯片内层深入,其互联的数量会急剧增大。

Chiplet是大芯片被切割成的小芯片,其间的互联自然不会少,经常一款Chiplet封装的硅转接板超过100K+的TSV,250K+的互联,这在传统封装设计中是难以想象的。

由于IO的增量化,Chiplet的设计也对EDA软件提出了新的挑战,Chiplet技术需要EDA工具从架构探索、芯片设计、物理及封装实现等提供全面支持,以在各个流程提供智能、优化的辅助,避免人为引入问题和错误。

Cadence、Synopsys、Siemens EDA(Mentor)等传统的集成电路EDA公司都相继推出支撑Chiplet集成的设计仿真验证工具。

总 结

从基尔比开始,同构集成技术经过六十多年的发展,已经相当成熟,并逐渐走向极致,同时,摩尔定律以指数增长的趋势也难以为继,人类必须寻找一种新的集成方式来进行延续,这就是异构集成。

异构集成以更灵活的方式让功能单位在系统空间进行集成,并让系统空间的功能密度持续增长,只是这种增长不再以指数方式增长。

异构集成的单元可称之为Chiplet,Chiplet技术给集成电路产业带来了新的变化,该技术既有新的优势也带来了新的挑战。

总结一下,Chiplet带来的三大技术趋势就是:IP芯片化、集成异构化、IO增量化。

审核编辑:刘清

-

集成电路

+关注

关注

5464文章

12688浏览量

375744 -

信号处理

+关注

关注

49文章

1160浏览量

105251 -

ASIC设计

+关注

关注

0文章

33浏览量

11097 -

sip封装

+关注

关注

4文章

69浏览量

16040 -

chiplet

+关注

关注

6文章

499浏览量

13650

原文标题:Chiplet带来的三大技术趋势

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

医疗电子技术新趋势—便携与无线

2012电源管理新趋势

2012电源管理新趋势

千策良品了解的产品设计新趋势是什么?J

电导技术——蓄电池测试的新趋势

2020年智能制造进入高速发展阶段,呈现哪九大新趋势

chiplet是什么意思?chiplet和SoC区别在哪里?一文读懂chiplet

中国首个原生Chiplet小芯片标准来了

Chiplet技术给EDA带来了哪些挑战?

Chiplet技术的发展现状和趋势

梯云物联|电梯行业三大发展新趋势:智慧转型、维保机遇与技术创新

Chiplet技术的出现带来了芯片设计的三大新趋势

Chiplet技术的出现带来了芯片设计的三大新趋势

评论