在这个信息化飞速发展的时代,如果说哪样东西是现代电子设备的心脏,那非半导体芯片莫属了。手机、电脑、汽车,乃至那些我们肉眼看不见的传感器,里面都有它的身影。但你知道吗,制造这些小巧而复杂的半导体芯片,是一项极其挑战性的技术工作,它涉及到的科技可真是既深又宽,咱们一起来探个究竟吧。

01

半导体芯片的设计阶段,电子设计自动化(EDA)工具扮演着至关重要的角色。EDA工具是一系列软件工具的总称,它们使得芯片设计师能够利用计算机辅助设计(CAD)技术来设计和分析整个半导体制造过程中的电子系统,包括集成电路(IC)和印刷电路板(PCB)。

使用EDA工具,设计师可以进行从逻辑设计、电路设计、布局设计到最终的验证和仿真的全过程设计。这些工具不仅提高了设计的效率,还大大减少了由于人为错误导致的缺陷,确保了设计的准确性和可靠性。EDA工具的使用,从根本上改变了芯片设计的方式,使得设计复杂度的大幅提升成为可能。

在芯片设计流程中,设计师首先需要完成电路的逻辑设计,这通常涉及到硬件描述语言(HDL),如Verilog或VHDL。这些语言允许设计师以代码形式描述电路的逻辑功能,而不是传统的图形方式。随后,这些逻辑描述会被转换成电路图,然后是物理布局,即决定各个电路元件在硅片上的具体位置。

系统级仿真是芯片设计流程中的另一个关键步骤。在这个阶段,设计师会使用EDA工具来模拟和验证电路设计在系统层面的行为。这包括对电路的时序、功耗、热特性和信号完整性等进行分析,确保设计在理论上是可行的。系统级仿真可以在实际制造芯片之前发现潜在的问题,从而节省时间和成本。

02

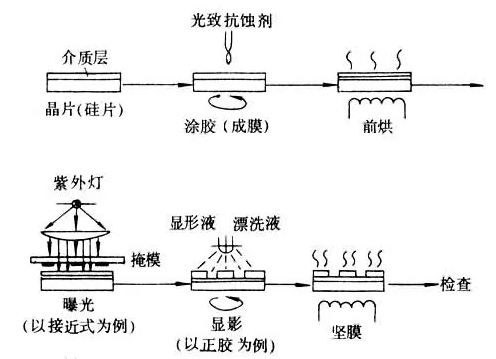

接下来就轮到光刻技术登场了。光刻过程是半导体制造中的关键步骤之一,它用于在硅片上创建集成电路图案的微小结构。这个过程涉及到将一种被称为光刻胶的光敏材料涂覆到硅片上,然后使用掩模(或称为光罩)上的特定图案暴露于光源之下。在光照的区域,光刻胶的化学结构会发生改变,使得在后续步骤中,这些区域能够被选择性地去除(正胶工艺)或保留(负胶工艺)。之后,经过一系列的化学和物理处理过程,最终形成所需的电路图案。

传统的光刻技术通常使用深紫外光(DUV)作为光源,波长大约在193纳米。由于光波的波长限制了光刻工艺中最小可制造的特征尺寸(即分辨率极限),因此随着电子设备对更高性能和更小尺寸的需求增加,传统的DUV光刻技术已经接近其物理极限。

EUV光刻使用波长仅为13.5纳米的光源,远远小于DUV光源的波长。这使得EUV光刻能够创建更小的特征尺寸,并因此实现更高密度的集成电路设计。EUV光刻技术的引入是为了满足先进节点,如7纳米、5纳米以及更小技术节点的制造需求。

EUV光刻的引入不仅提高了芯片的性能,还减少了制造过程中需要的掩模数量,因为更少的掩模暴露步骤就可以达到同样的特征细节。

03

但是光刻之前,我们得有硅片,对吧?制作硅片的过程也是讲究满满。从单晶硅的生长开始,单晶硅是大多数集成电路生产中使用的基本材料,单晶硅的质量直接影响到集成电路的性能和可靠性。为了生产单晶硅,Czochralski(CZ)提拉法是其中最重要的技术之一。关于提拉法技术大家可以去查询资料了解,这里不做过多讲述。

生长好的单晶硅锭需要经过切割、抛光和清洗等后续加工步骤才能最终转化为可用于集成电路制造的硅片。硅锭首先会在切割机中被切割成薄片,这个过程通常使用金刚石线锯或内部应力控制的刀具来进行,以减少材料的损耗并提高切割的精度。切割后的硅片厚度通常只有几百微米。

切割完成后,硅片表面会非常粗糙,因此需要经过抛光的工艺以获得平滑的表面。抛光过程包括机械和化学两个阶段,通常被称为CMP(化学机械平坦化)。这个过程可以移除表面的微裂痕和杂质,减少缺陷,从而保证硅片的质量符合集成电路制造的严格标准。

最后,硅片还需要进行严格的清洗过程,以去除在切割和抛光过程中产生的所有污染物。清洗通常包括酸、碱、超纯水冲洗等多个步骤,每一步都要在洁净室环境下进行,以避免任何新的杂质附着在硅片表面上。

通过这些精密的工艺流程,高品质的单晶硅片最终将为下一步的集成电路制造做好准备。

04

硅片做好了,还得经过离子注入和掺杂,这可是调整硅片电导率的关键所在。用一些高科技装备,把必要的杂质原子射入硅片,从而赋予硅片特定的电性,听起来是不是有点像科幻电影里的情节?

我们的电路图绘制好了,电导性也调整好了,下一步就是要在硅片上沉积各种薄膜,这就需要用到化学气相沉积(CVD)技术了。这个过程中,我们会用到等离子体增强CVD和低压CVD等手段,确保薄膜均匀、牢固地附着在硅片上。

05

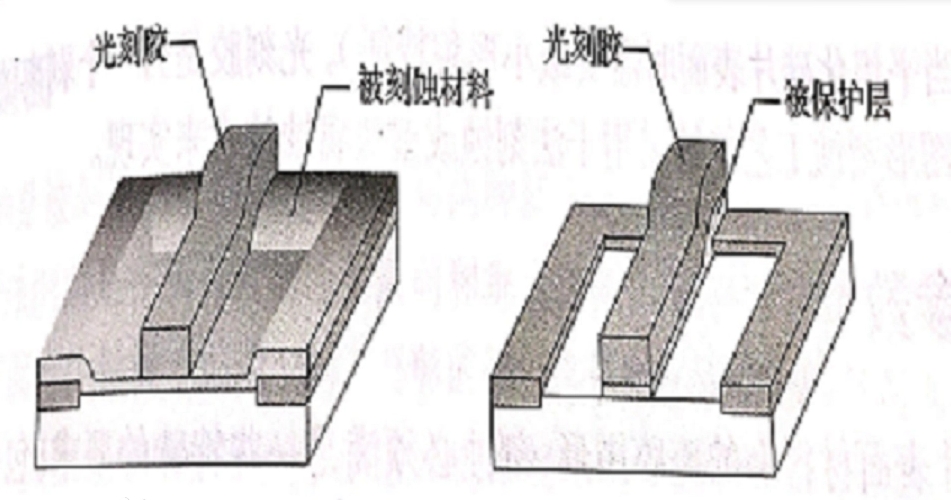

沉积薄膜之后,就得通过刻蚀技术来去除多余的部分,形成精确的电路图案。在半导体制造过程中,刻蚀技术是用来去除硅片上特定区域的材料,以形成电路图案的方法。刻蚀工艺主要分为干法刻蚀和湿法刻蚀两大类。

干法刻蚀(Dry Etching)是利用气体等离子体产生的化学活性粒子来移除硅片表面的材料。这种方法的特点是刻蚀过程可以非常精确地控制,因此广泛应用于微细加工领域。干法刻蚀能够实现高度各向异性的刻蚀,意味着它能垂直于硅片表面精确地移除材料,适合用于制造具有陡峭边壁的复杂结构。此外,干法刻蚀过程是在封闭的真空系统中进行,可以减少污染,提高制造环境的清洁度。

湿法刻蚀(Wet Etching)则是使用液体化学溶剂来溶解和移除硅片上的材料。这种方法操作简单,成本较低,但是其刻蚀过程通常是各向同性的,这意味着刻蚀会沿着水平和垂直方向同时进行,导致边缘不够锐利,不适合高精度的图案制造。然而,在某些应用中,比如大面积的材料去除和初步的图案制造,湿法刻蚀仍然是非常有效和经济的选择。

总结来说,干法刻蚀和湿法刻蚀各有特点和适用范围,随着集成电路设计的不断进步,这些刻蚀技术也在不断地发展,以满足更严格的制造要求。

06

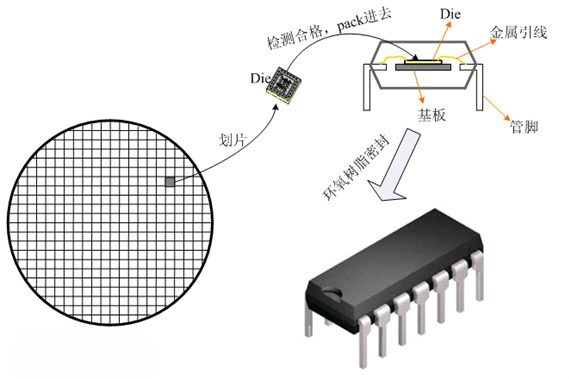

电路造好了,但还不能直接使用,还需要封装保护。芯片封装是半导体制造过程中至关重要的一步。其主要目的在于保护微观尺度的集成电路免受物理损伤、化学腐蚀、湿气侵蚀以及电磁干扰等外界因素的影响。封装过程还能提供电气连接,将微小的芯片引脚扩展至足够大的引线或焊球,以便于在电路板上进行安装。此外,封装还有助于散热,防止集成电路在工作过程中因温度过高而损坏。

芯片封装过程一般包括以下几个步骤:

准备裸片:通过切割硅晶圆,将其分割成单独的芯片。

安装芯片:将裸片安装到一个支持结构(通常是一个铅框或塑料基板)上。

引线键合:通过金线键合、银胶键合或者焊球贴附等方式,将芯片上的电极连接到封装引脚上。

封装:使用塑料、陶瓷或金属材料将芯片和引线键合部分封装起来,常见的封装方式有SOIC、QFP、BGA等。

切割和成型:将封装后的产品切割成单个封装单元,并对引脚进行成型处理。

最终检验:对封装好的芯片进行视觉和电气性能检验,确保其符合要求。

07

芯片封装完成之后,我们还得测试一下。芯片的功能、性能,乃至可靠性,都得通过严格的测试来验证。

功能测试是验证芯片是否按照其设计规格正常工作的过程。通过模拟芯片在实际应用中的条件,检查所有的逻辑功能是否正确执行。

性能测试则是对芯片的速度和其他性能参数进行评估。这包括但不限于频率、功耗、时序特性等。性能测试确保了芯片在规定的性能范围内稳定工作。

可靠性测试是为了评估和保证产品的长期稳定性和耐用性。可靠性测试可能包括高温操作寿命(HTOL)、温度循环、湿度测试、机械冲击和振动测试等。这些测试通常在极端条件下进行,旨在模拟芯片在整个预期使用寿命内的环境变化。

通过这些测试,制造商能够确保每一颗芯片都能在其应用环境中提供稳定、可靠的性能。如果测试发现有任何问题,相关的芯片可以在批量生产并投入市场之前及时被筛选出来。这些严格的测试流程是确保电子产品质量和可靠性的关键步骤。

08

未来的路还很长,新材料、量子计算、纳米技术,每一项都可能是革命性的发展。芯片制造技术就像是一场永无止境的马拉松,每一步的创新都可能改变整个行业的走向。

看到这里,我想你应该对对芯片生产有了更深的理解,虽然它是个技术密集型的过程,但正是这些复杂又精妙的技术,让我们的芯片越来越强大,同时也越来越实惠。技术的创新从未停歇,我们也将一直期待着它带来的新奇和进步。

-

传感器

+关注

关注

2548文章

50644浏览量

751756 -

芯片

+关注

关注

453文章

50362浏览量

421649 -

半导体

+关注

关注

334文章

26989浏览量

216032

发布评论请先 登录

相关推荐

你的方案需要用到加密芯片吗?

线缆生产是否需要用到单向测径仪?

连接网络需要用到的设备猫和路由器,它们有什么区别

在冶金生产过程中需要用到的传感器

智能配电房一般都需要用到哪些相关设备

汽车芯片的分类 一辆汽车需要用到多少芯片

SMT贴片加工所需要用的主要生产设备是哪些?

食品检测项目需要用到哪些仪器设备

物联网开发中需要用到哪些编程语言?

一文看懂芯片生产整个过程以及需要用到哪些技术

一文看懂芯片生产整个过程以及需要用到哪些技术

评论