高速先生成员--黄刚

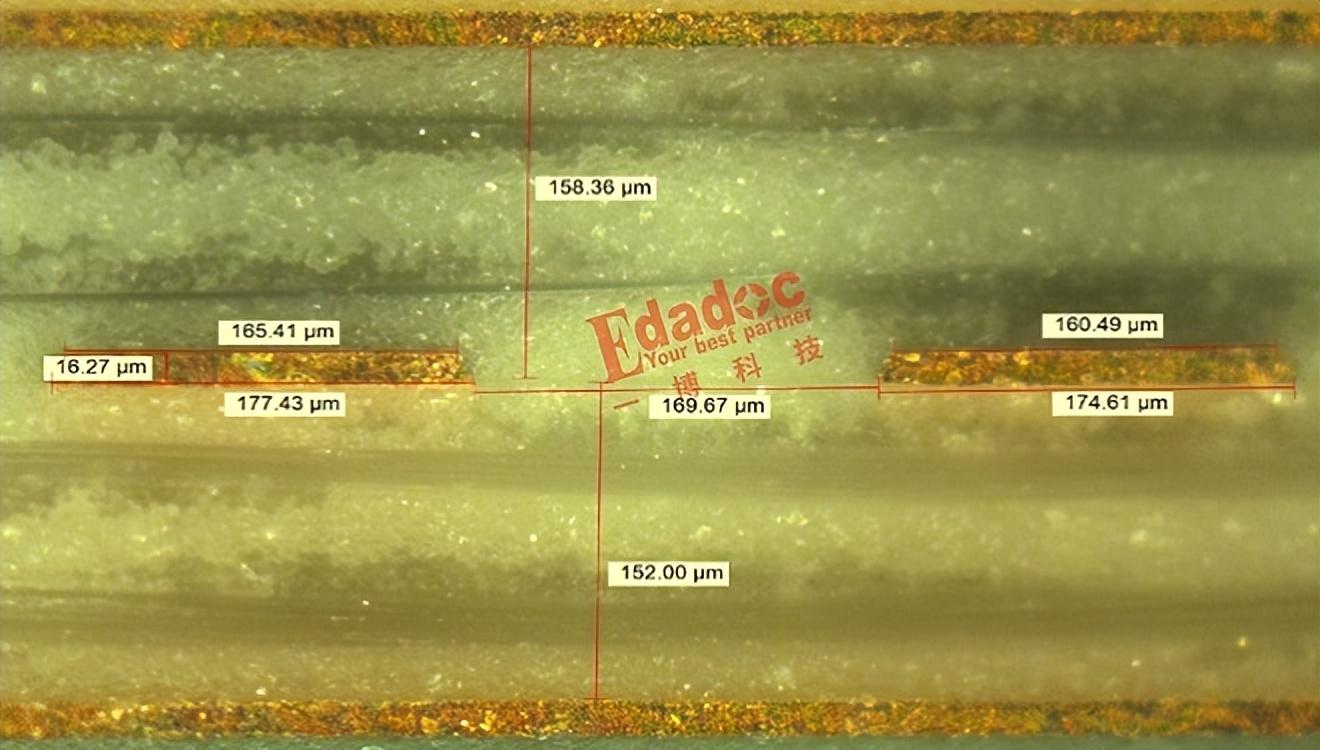

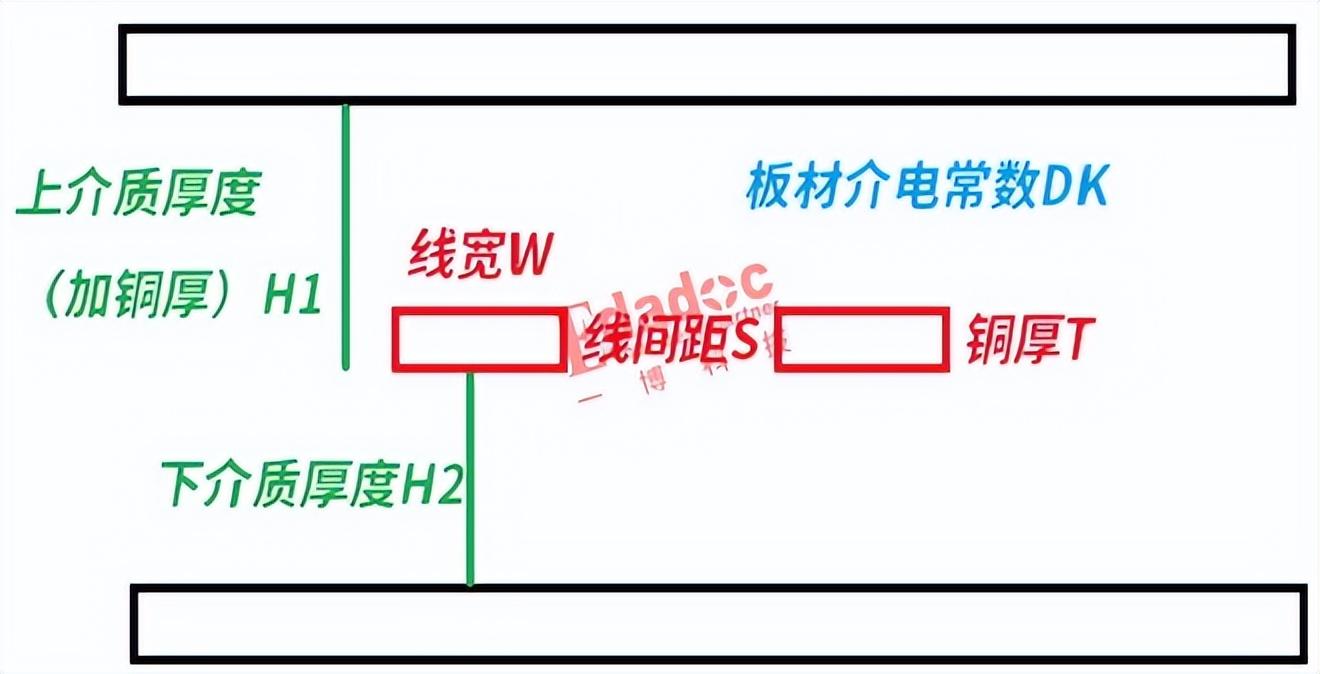

传输线阻抗控制对系统性能的重要性不言而喻,每一家的PCB加工板厂都在往能控制更严格的阻抗公差这个目标而不断努力。但是我们也知道,传输线阻抗的控制公差其实会受到PCB结构本身的因素影响,就好像下面这张PCB差分线的切片图一样,至少有6、7个参数影响传输线的阻抗,例如线宽、线间距、上介质厚度、下介质厚度、铜厚、板材的介电常数等。它们共同决定了这对差分线的阻抗,他们的控制公差决定了差分线阻抗的公差!

今天,高速先生这篇文章想走个高端路线,我们来研究下上面提到的所有影响传输线阻抗的参数里,到底能不能比较定量的给他们排个序,看看到底哪个因素的控制公差对加工出来的传输线阻抗的公差影响最大呢。这算不算是一个比较有意思的研究方向?

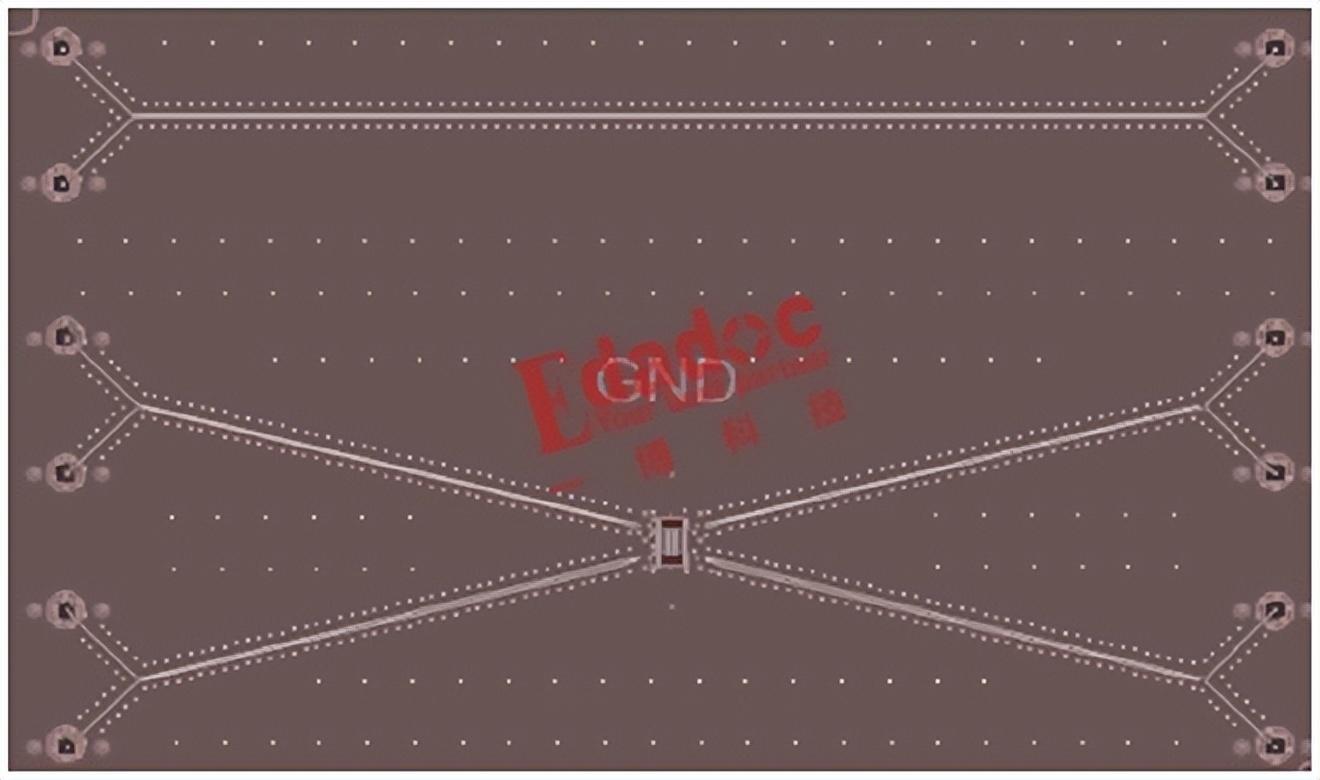

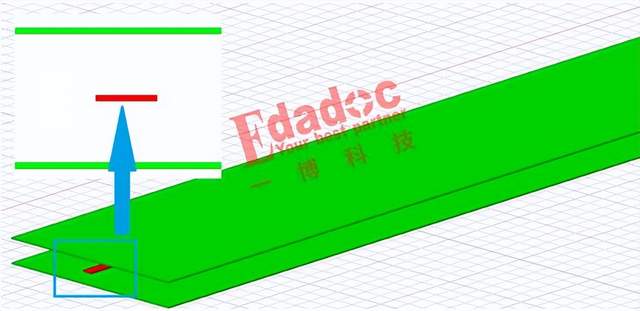

我们一起来看看高速先生最近做的测试板的案例,我们做的是一个USB的测试夹具,PCB设计如下所示:

为了保证高频的性能,我们使用1到2的激光孔工艺,然后走线就在L2层了。由于板厚比较薄,也就是L2层的上下层介质厚度也很薄,因此我们L2层的线宽自然就设计得很细了。

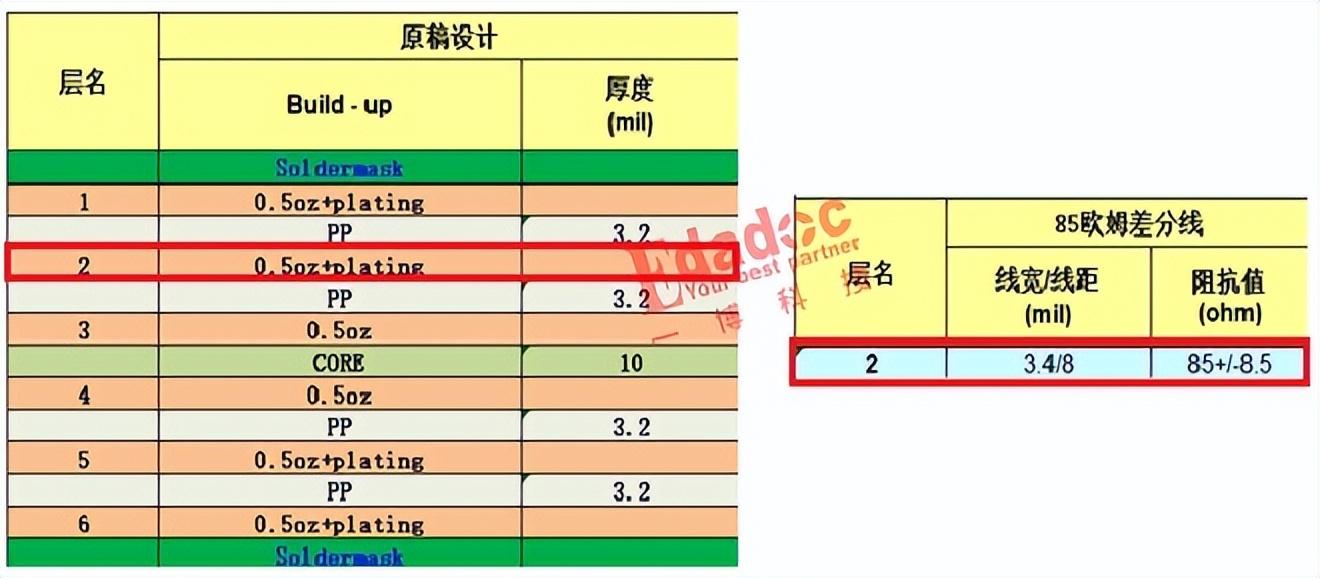

叠层和L2层的线宽线距就是下面这个样子了。上下层厚度也就3mil多的样子,差分阻抗控制85欧姆情况下,线宽也是3mil多点。顺便提一下,板材是中等损耗板材,介电常数DK在3.8左右。

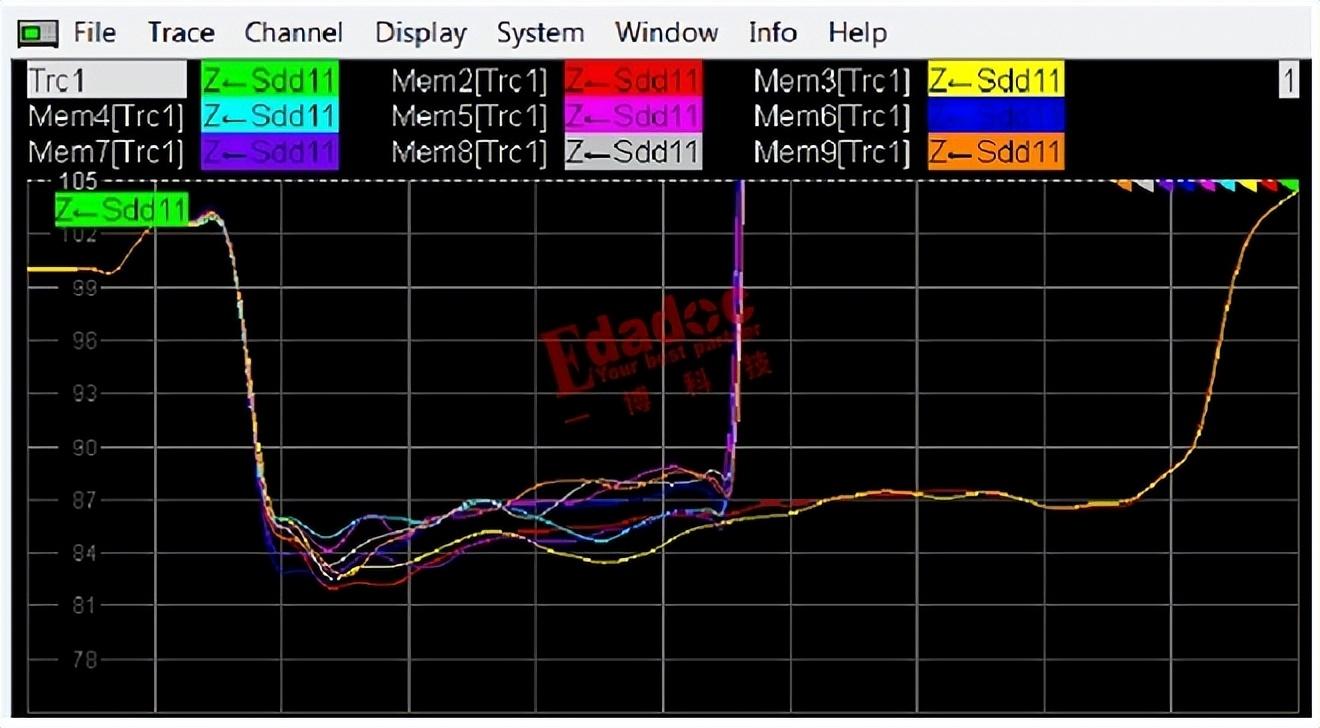

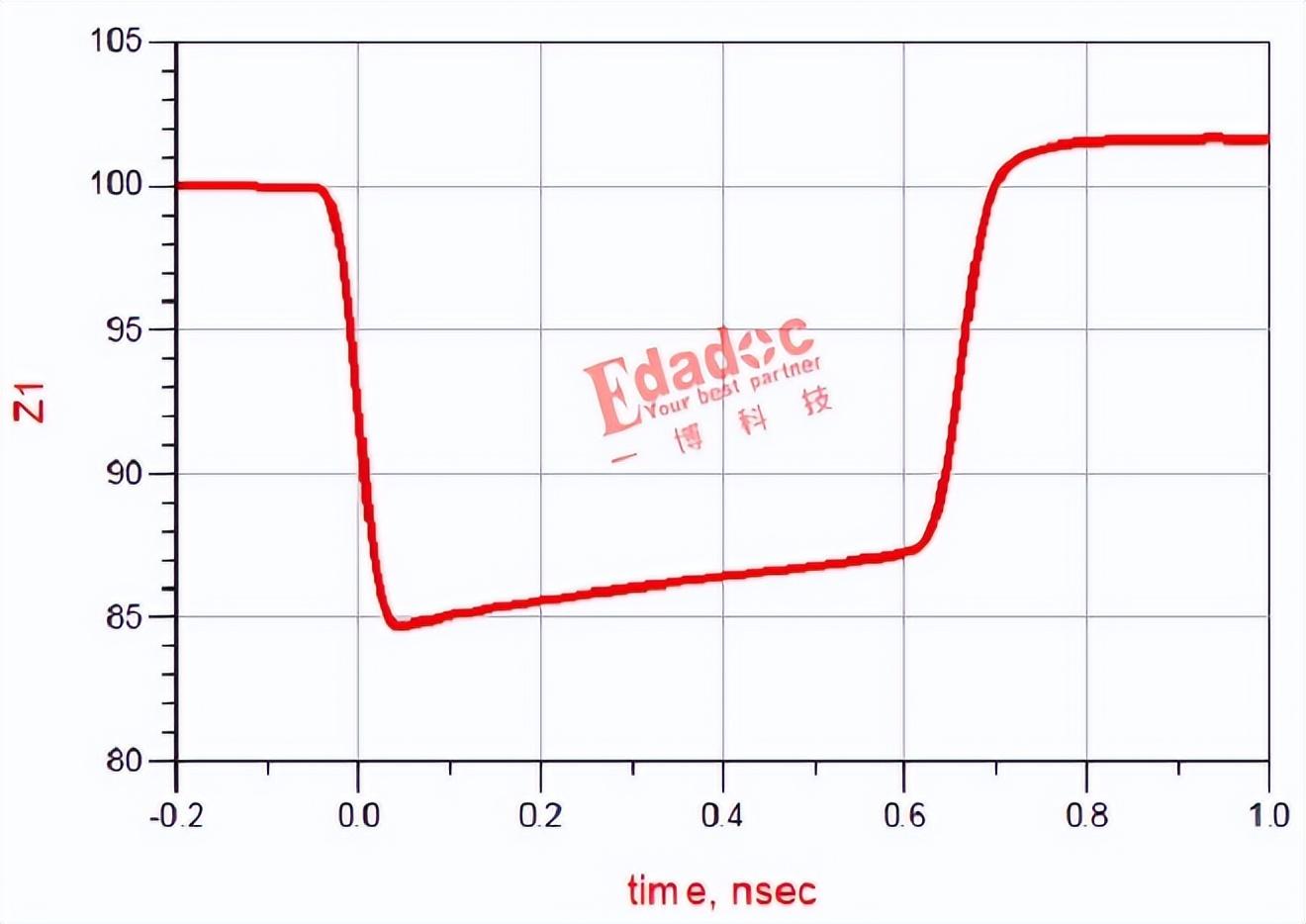

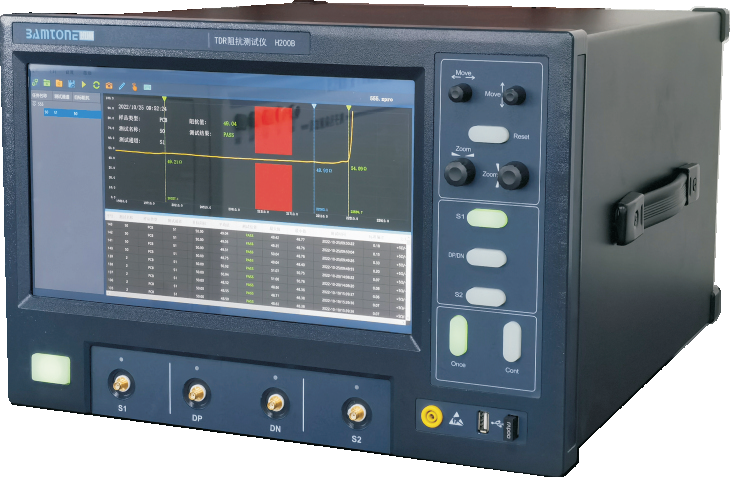

然而我们也知道,阻抗加工肯定是有偏差哈,板厂一般是保证10%的阻抗偏差,严格的话可能就是8%的阻抗偏差。下图是该项目最终加工完成进行阻抗测试的传输线结果。

其实能看到,同一块板上的长线和短线的阻抗都很好的满足8%的阻抗偏差(其实已经接近5%了),这一组差分线的阻抗其实已经加工得非常的好了!

那回过头我们再进行下理论的分析。根据板厂给出的叠层,我们通过仿真软件进行阻抗的仿真,的确能看到阻抗的中值就在85欧姆,以下是线长2inch情况下的传输线阻抗仿真结果。

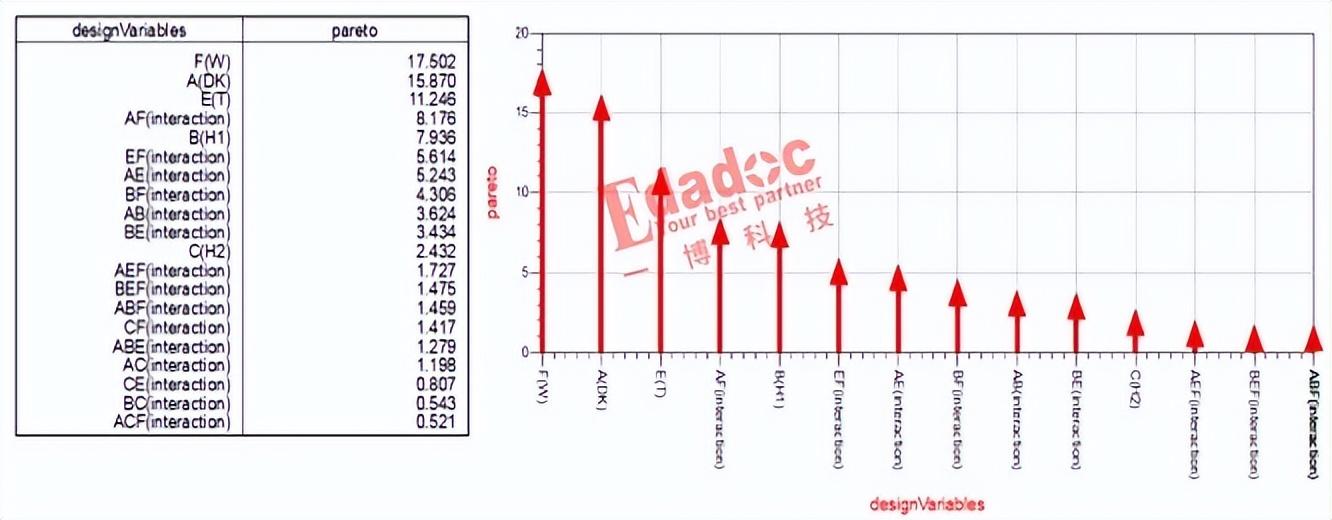

那么要怎么来研究上述的参数对阻抗的影响度呢?我们可以用相关仿真软件的容差分析控件,俗称DOE分析来进行研究。这个控件主要就是分析如果每个参数都有一定的偏差时,对整体阻抗结果的偏差度影响是怎么样的,同时也能得到每个参数对后面结果的影响比例!是不是听起来就有点意思呢?

我们先用一张传输线的结构图来说明这个案例中的参数情况,如下:

其中根据板厂给出的叠层,每个参数的中值分别为:线宽W=3.4mil,线间距S=8mil,上介质厚度(加铜厚)H1=4.4mil,下介质厚度H2=3.2mil,铜厚T=1.2mil,板材的介电常数DK=3.8,那我们就开始进行DOE的仿真。原理也很简单,我们分别把上面的6个变量参数都设置允许10%左右的误差,我们来看看进行DOE仿真后,每个参数对最后阻抗结果的贡献比例是多少!

好!我们来看看在这个case下的DOE仿真结果,就是下面的这张图:

高速先生来解释一下这张图来表达的意思哈!首先左边表格给出的是不同变量的同样误差改变下对后面传输线阻抗的影响比例。例如线宽W的误差改变,会占到17.5%左右的比重;介电常数DK也会有15.8%的影响;铜厚T也占到了11.3%左右。另外还有一些参数可能是互相有影响的,因此结果也一并来考虑。例如线宽W和上介质厚度H1加起来的影响为4.3%。

很多朋友之前是不是没想过从这个角度出发来分析呢?这个分析其实意义还是很重大的,它可以很清晰的给出哪个参数的影响是最大,在加工过程中可能就需要重点去管控这个因素,这样的话其实就对最终的阻抗公差有更好的把握。另外也需要知道的是,不同的叠层,不同的线宽线距时,每个参数的影响度的DOE分析结果肯定是不一样的,可能在A项目中线宽的影响最大,但是在B项目中可能就变成了介质厚度的影响最大了。因此需要针对你们实际产品的情况去做具体分析了哈。

最后问一句,这个方法大家get到了吗?

本期提问

如果用文章中的例子让你分析下损耗情况,你觉得损耗和哪些参数有关,哪些参数的影响度最大呢?

审核编辑 黄宇

-

pcb

+关注

关注

4418文章

23979浏览量

426422 -

阻抗

+关注

关注

17文章

994浏览量

49527 -

传输线

+关注

关注

0文章

384浏览量

25577

发布评论请先 登录

深入解析 PI7AT04:低电压、零延迟有源传输线钳位器

PCB加工中的“流胶”到底是怎么影响阻抗的?

锂电池嵌入电极颗粒的传输线法TLM 模拟研究

基于改进传输线法(TLM)的金属 - 氧化锌半导体界面电阻分析

传输线法(TLM)优化接触电阻:实现薄膜晶体管电气性能优化

Bourns 推出全新共模电感系列 专为信号传输线应用提供理想的噪声抑制解决方案

PanDao应用:确定和转换透镜公差

知识分享-传输线的返回电流(信号完整性揭秘)

传输线高频参数之Crosstalk

掌握了这个分析方法,实现传输线阻抗5%的加工公差不是梦!

掌握了这个分析方法,实现传输线阻抗5%的加工公差不是梦!

评论