做为FPGA的集成开发环境,不同的厂家其实大同小异。很多国产厂家,如安路,高云,会在软件上贴近Xilinx和Intel,以节省客户的软件使用成本。而国产厂商的易灵思的集成开发环境Efinity似乎并不像大厂,显得差异更大一些。但经过一段时间的使用,我个人认为并不需要因为差异大些就过于排斥,Efinity在使用上并不会麻烦。 接下来我们来聊一下Efinity的一些功能及个人使用感受。主要包括以下几个方面:

(1)软件安装;

(2)软件界面;

(3)控制面板;

(4)预设置;

(5)工程编译器;

(6)interface 与Core架构;

(7)在线调试;

(8)配置方式;

1、软件安装

这里以windows系统为例。Efinity的软件安装过程相对操作步骤多些,但是过程也很清晰。包括python的安装、Efinity的安装、驱动的安装和在线调试工具的安装。而且Efinity软件比较小,只有1G左右,另外Efinity也没有把器件库单独分离,整个安装时间相对短很多。再者Efinity也没有license的限制,也就没有因为license过期而需要等待重新申请的过程,这对于很多FPGA开发应该说轻松不少。

2、软件界面

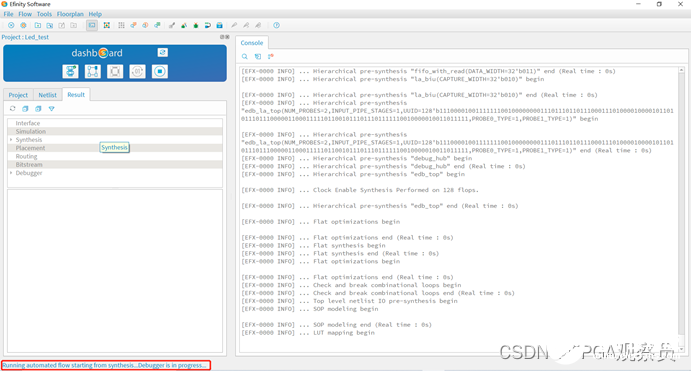

打开Efinity界面如图1,大致的框架与其它厂商也没有多大差别,有控制面板,代码编辑器,控制台,信息栏等,毕竟都是FPGA集成开发环境,也不能差异大到哪儿去。 有些地方个人认为需要调整,比如编译时没有进度条,也没有时间指示,不过左下方也有信息提示;另外项目路径放在软件最上方,各个窗口之间灰度空白缩小一点等小细节也可以稍做调整。但对于一个只开发了三年左右的FPGA集成环境,已经非常不错了。

图1

3、控制面板

下面主要来聊下控制面板。控制面板分成四部分:流程控制台、工程面板、网表面板,输出面板。

流程控制台:深蓝色的dashboard部分就是流程控制台, 如图2。主要控制程序的编译流程,包括综合、布局、布线和生成烧写文件。另外两个是停止和单步流程运行。这与所有厂家都大同小异。

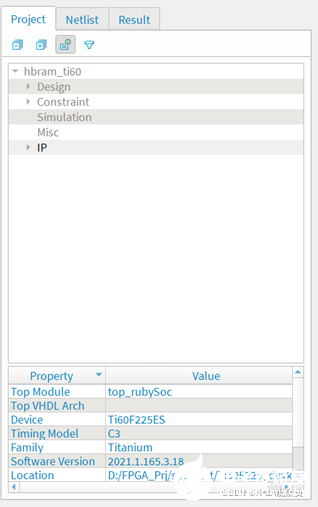

图2 工程面板(Project):客户可以在工程向导中添加源文件,IP和仿真文件等。另外也可以查看选择的器件、工程路径及顶层文件等信息,如图3所示。

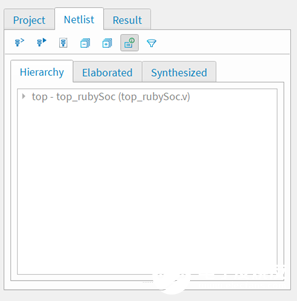

图3 网表面板(netlist):客户可以在这里查看工程中生成的网表,包括hierarchy、Elaborated和Synthesized三种,如图4所示。

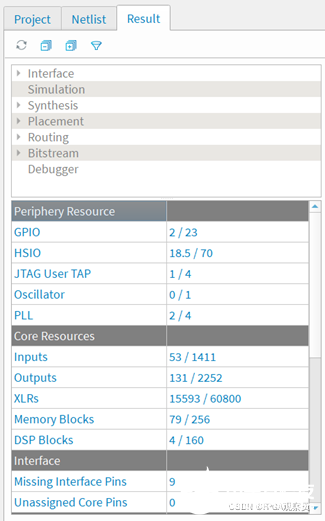

图4 输出面板(Result):这里主要是工程编译生成的各种报告及资源使用详情,时序裕量、时钟MAX值等,如图5所示。 输出面板(Result):这里主要是工程编译生成的各种报告及资源使用详情,时序裕量、时钟MAX值等,如图5所示。

图5 总的来说,控制面板中工程编译信息都是很详细的,而且输出信息以文件的形式给出在保存和发送上也是很方便的。

4、预设置(preferences)

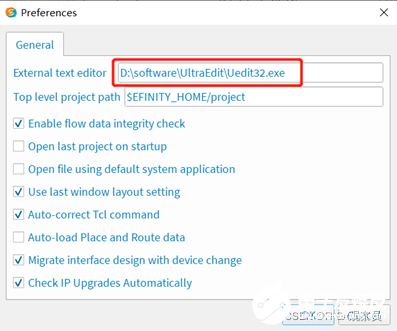

在预设功能中这里主要提两个功能,其余大家可以在使用中体会。如图6所示,一个是外部编译器,另一个是Auto-load Place and Route Data。当然其余功能也很重要。 一般来说软件自带编辑器功能有限,所以集成环境一般都支持指定外部编译器。Efinity同样也支持外部编译器件,并且操作上相对某些集成环境也更简单,只需要在Preferences下面指定外部编译器件的执行文件路径即可 如果双击Project下的Design或者在Hierarchy下面的文件,文件会以自带的编辑器件打开。只有选择文件右击,并行选择Open with user Editor时才会通过用户设置的编译器打开,看似麻烦一些,却可以同时使用两种编译器件。这一点在使用Quartusprame的自带编辑器件insert功能时会有深刻体会到在某个时刻它的优势。 另外还有一个Auto-load Place and Route Data功能值的一提,该功能可能根据需要来选择加载时是否可以加载布局布线的数据。如果不加载布局布线的数据可以节省打开软件的时间以及节省编译时间,还可以手动加载,也算比较灵活的一个功能。

图6

5、工程编辑器(Project Editor)

软件使用中的大部分功能都在Project Editor中,包括工作设置,工程文件的添加,器件的指定、综合和布具布线的设置及优化选项、位流文件的生成方式及在线调试文件的指定。相对来说没有大厂的功能丰富,但功能划分比较清晰而都是在设计中用得到的。 下面来简单聊下部分功能。 工程设置(Project):工程设置包括工程名、工程位置、器件家族及器件的型号和速度等级这些常用项。一目了然,毋需多言,如图7所示。

图7 设计文件添加:这里用于指定顶层文件,添加源文件及约束文件,如图8所示。

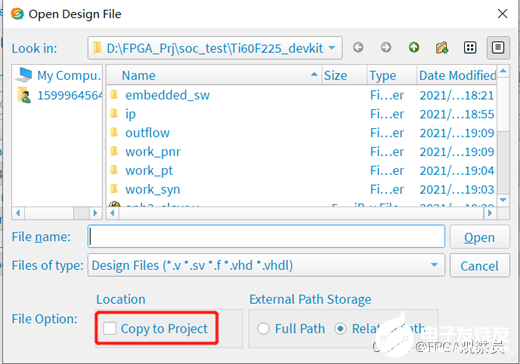

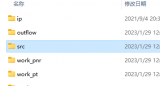

图8 除了可以单独添加文件外,Efinity还可以添加整个文件夹的文件,如图9所示。另外还支持把外部文件导入到工程目录下,如果不导入工程,也可以指定相对路径或者全路径。这个功能比较灵活支持各种方式的文件添加,是比较方便的。

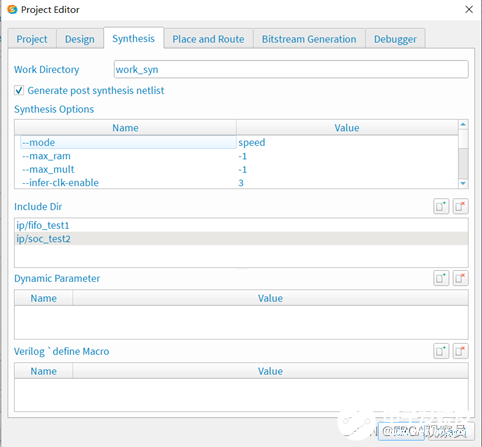

图9 综合(Synthesis):综合页面有关于综合的优化选项,添加参数和宏定义等,常用的功能都是存在的,如图10所示。

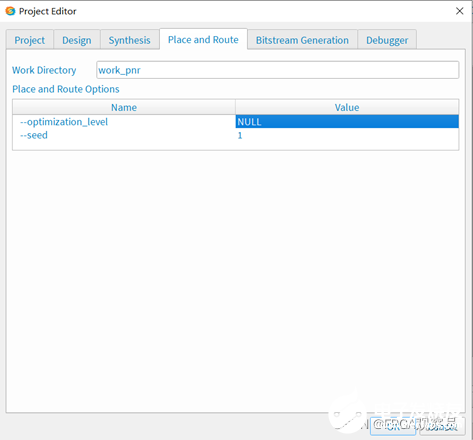

图10 布局布线(Place and Route):如图11所示,布局布线功能相对简单,有6个优化策略和种子选择。另外也可以通过命令来扫描策略和控制种子运行数量,操作也非常简单,另外结论会以文件的形式输出,一目了然。

图11 有关于位数据流和调试就不再展开,留给大家自己去亲自体验下。 我们可以来对比一个点,而别的厂家,比如xilinx和intel,顶层文件是在在Hierachy中指定,并把Hierachy摆放在一个主要的位置,显得更一目了然。而Efinity的工程的顶层文件需要手动输入,如果没有输入会自动检测,但是并不一定准确。上面的网表中也讲到Efinity也有Hierachy的功能,但感觉已经弱化了它的重要性。在应用中只要稍加注意或者使用习惯之后,是不会存在任何问题的。

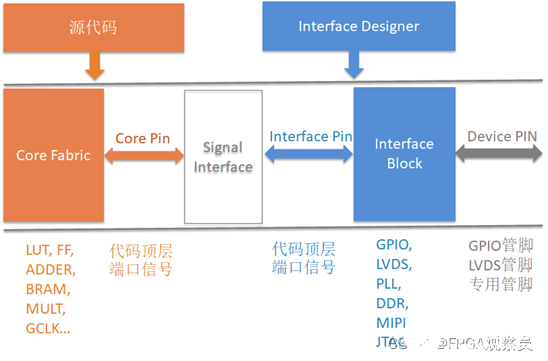

6、Inteface 与Core分析的架构

Eifinty与别的器件厂商集成环境的一个很大不同之处在于,Eifinty采用的把逻辑资源和硬核资源分开的架构,如图12所示。代码部分只针对逻辑资源,也就是我们这里提到的Core,而IO及其他硬核部分的配置在interface Designer工具中。下图是interface与Core的关系,它们之间通过被称作Siganl Interface的连线资源实现互联。 这里要提到的是因为习惯问题,使用者在最初一定会存在一些问题,但是习惯之后它也是有不少优势存在的。比如说,在前期的硬件设计中,只需要在Interface Designer中添加已添加的IO及其他需要的硬件接口,并通过一键检测就可以很清楚的知道与外设的连接是否合理,不需要考虑内部因为没有完整的程序而可能被优化的风险。 当然,它也有不灵活之处。不如通过代码复制来的简单快捷,虽然也可以通过文件设置再导入,但是文件的编辑上也会相对麻烦一些。

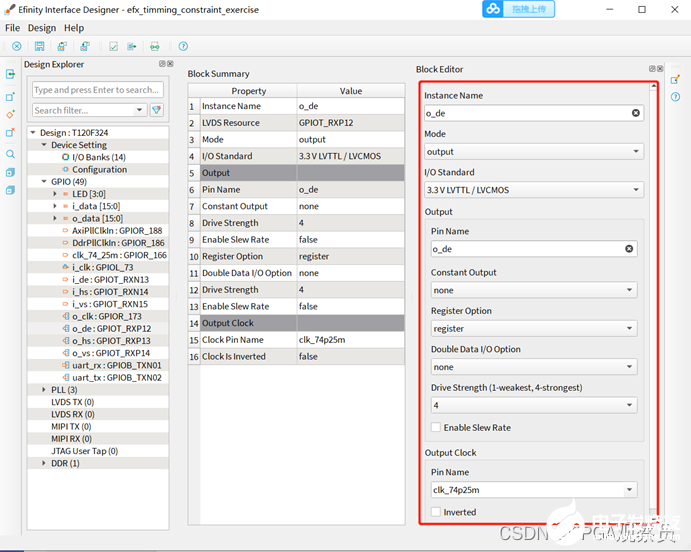

图12 这里以GPIO为例,如图13所示,可以设置例化名,指定IO类型,设置电平标准,选择是否支持寄存器,选择是否支持DDR数据及信号驱动强度等。这相对于在RTL文件直接用input或者output来定义信号来说,更有利于理解GPIO的内部结构及其使用规则。整体来说这种interface和core分析的架构优势很明显。

图13

7、在线调试

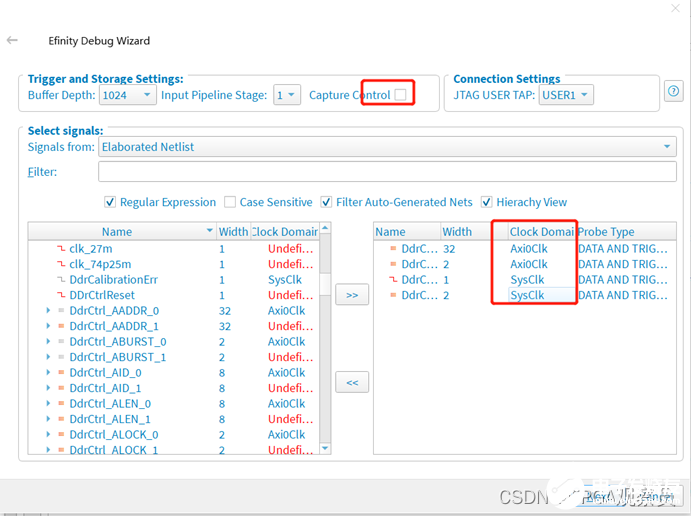

Efinity的在线调试工具名为Debbuger,如图14所示,目前只支持post-map网表 elaborated(综合前)网表,如图3所示,如intel的signalTap一样,用户可以通过简单的点击信号来选择,用户可以通过选择不同的时钟域,把信号自动分到不同的界面,操作相对简单。另外在勾选了Capture Control选项之后,也可以支持任意触发位置和分段触发。这都是Efinity相对具有的优点。 但由于软件开发时间比较短,不足之处也是有的,Efinity的Debbuger工具占用资源相对多些,对时序也会有些影响。并且目前也不支持上电触发和多级触发等功能。但是相应的功能和优化也已经在迭代开发中,每个一新发布的版本都值得期待。

图14

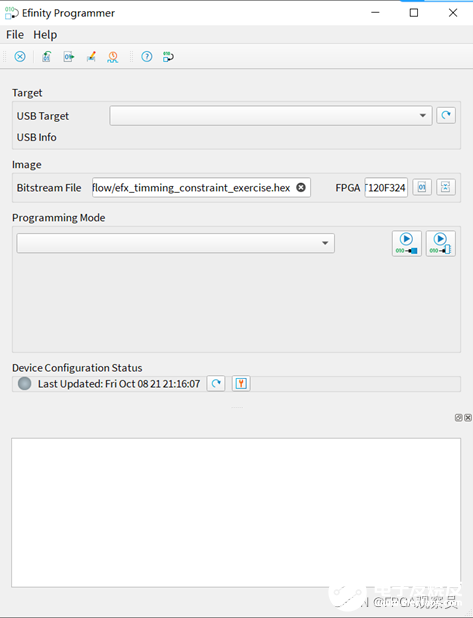

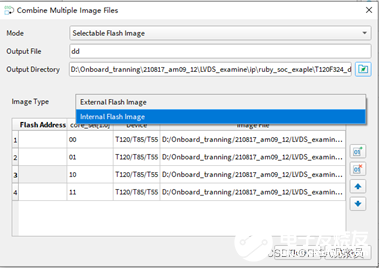

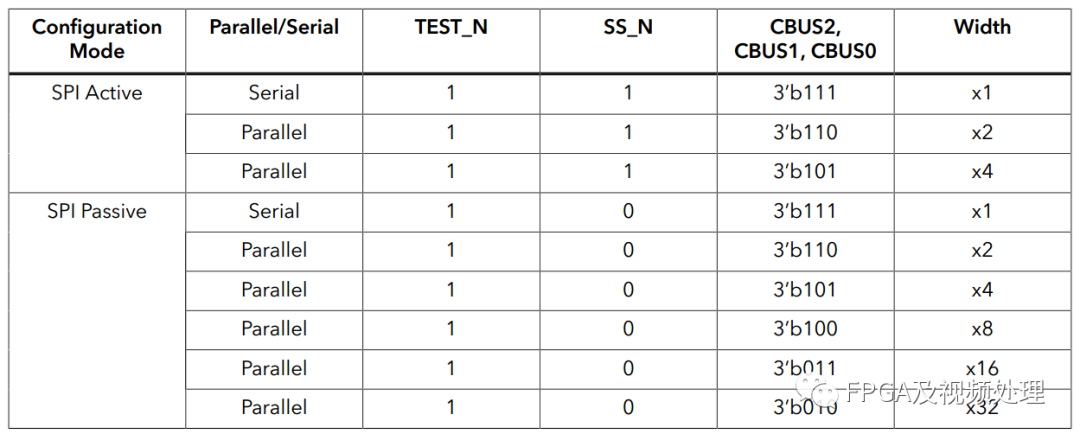

8、配置方式

目前Efinity支持的配置有AS模式,PS模式、jTAG模式和Jtag Bradge四种模式。这几种模式也是最常用的,各个厂家差异几近相似。大厂模式更多些,但这些模式在实际使用中——由其在中低端器件上——使用者寥寥无几。 图15是一个Programmer界面。Efinity的Programmer界面比较朴素,连进度条也没有,不过通过打印信息可以看到配置进程。

另外Efinity仿真模型也都是能RTL代码的形式存在,在通过第三方仿真时也不需要编译库等等。Efinity也有通过指令控制之类一些软件使用功能,这里不再一一列举。总结来说,Efinity是一个具备FPGA开发完整功能的集成开发环境,虽然相对大的厂商Xilinx和Intel的集成开发环境功能还有一段距离,但是只要存在的功能都显示出了清晰明了的特征,相对都操作更简单直接。并且在每一个版本的迭代上功能都越来越丰富。我们也由衷期待易灵思在FPGA这个行业越做越好,为国产FPGA行业带来更多创新和更长足的发展。

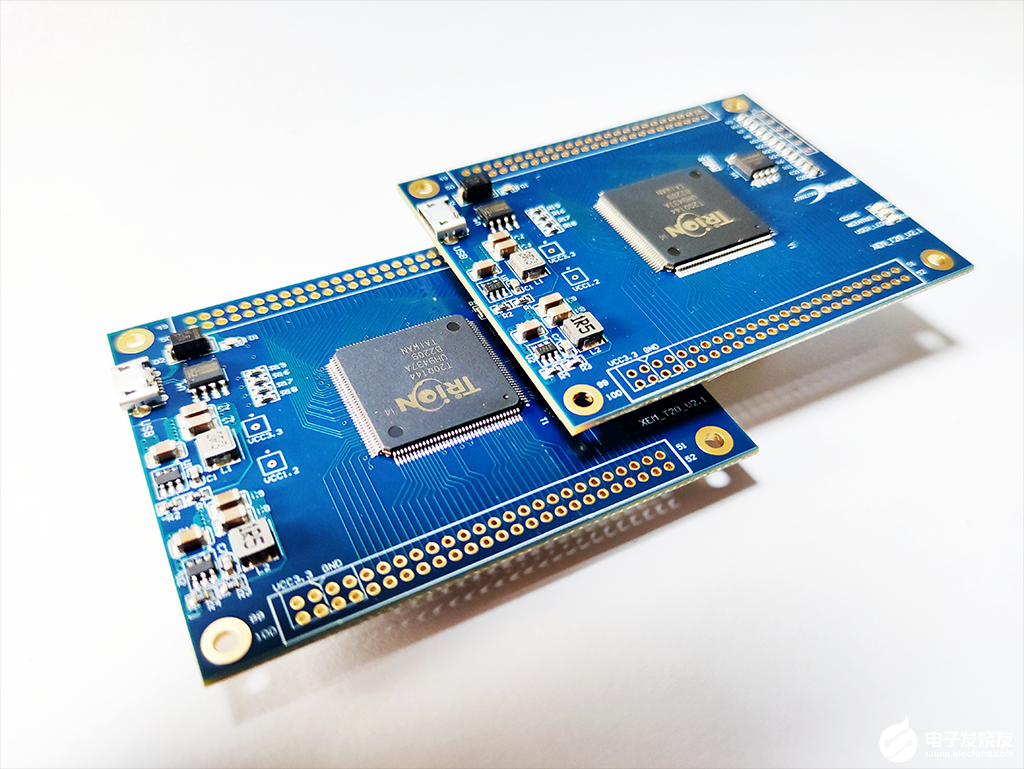

如果想快速上手易灵思的FPGA,可以选择“XEM_T20”FPGA模块快速上手,直接上手编程,实现您的idea在FPGA上。

-

FPGA

+关注

关注

1664文章

22508浏览量

639458 -

国产FPGA

+关注

关注

0文章

9浏览量

15939 -

易灵思

+关注

关注

6文章

66浏览量

5601

发布评论请先 登录

易灵思(Elitestek)FPGA编程器功能特点及驱动安装方法

从赛灵思FPGA设计流程看懂FPGA设计

易灵思推Trion Titanium FPGA,采用 “Quantum™ 计算架构”

易灵思FPGA产品帮助安防领域创新和突破

亿灵思®国产可编程逻辑芯片EDA软件系列一:亿灵思设计软件介绍

易灵思FPGA产品的主要特点

国产FPGA应用专题--易灵思Efinity软件使用心得

国产FPGA应用专题--易灵思Efinity软件使用心得

评论