1. 概述

在摩尔定律的推动下,集成电路工艺取得了高速发展,单位面积上的晶体管数量不断增加。

片上系统(System-on-Chip,SoC)具有集成度高、功耗低、成本低等优势,已经成为大规模集成电路系统设计的主流方向,解决了通信、图像、计算、消费电子等领域的众多挑战性的难题。

随着片上系统SoC的应用需求越来越丰富,SoC需要集成越来越多的不同应用的IP(Intellectual Property)。另外,片上多核系统MPSoC(MultiProcessor-System-on-Chip)也已经成为必然的发展趋势。

随着SoC的高度集成以及MPSoC的高速发展,对片上通信提出了更高的要求。片上网络技术(Network-on-Chip,NoC)在这个时候也得到了极大的应用,它本质上就是提供一种解决芯片内不同IP或者不同核心之间数据传输的片上通信方案。

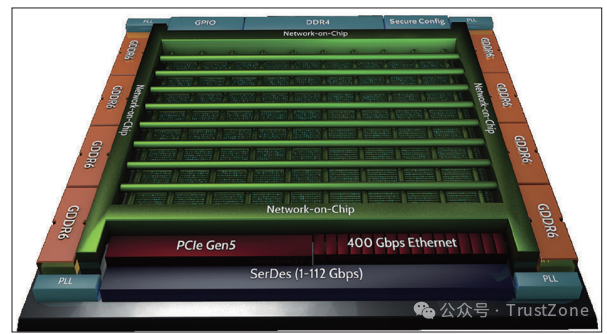

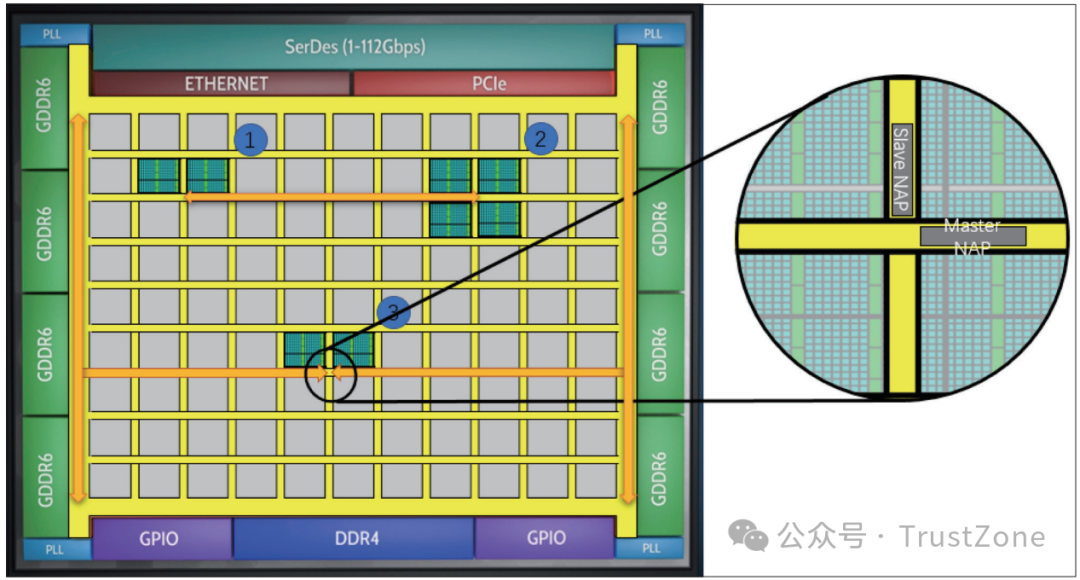

片上网络技术从发明至今已有20多年的历史,在SoC中已经有了广泛的应用。针对片上网络高带宽、低延迟的特性,主流FPGA公司也开始考虑将NoC用于高端FPGA中来解决数据传输的高带宽需求。Achronix的新一代7nm工艺的Speedster 7t便是最早集成了NoC的高端FPGA之一。如图1所示。

图1 Speedster 7t FPGA结构图

2. 片上互连架构的发展

片上互联架构的发展主要经历了三个阶段:

共享总线(Bus)

Crossbar

片上网络(NoC)

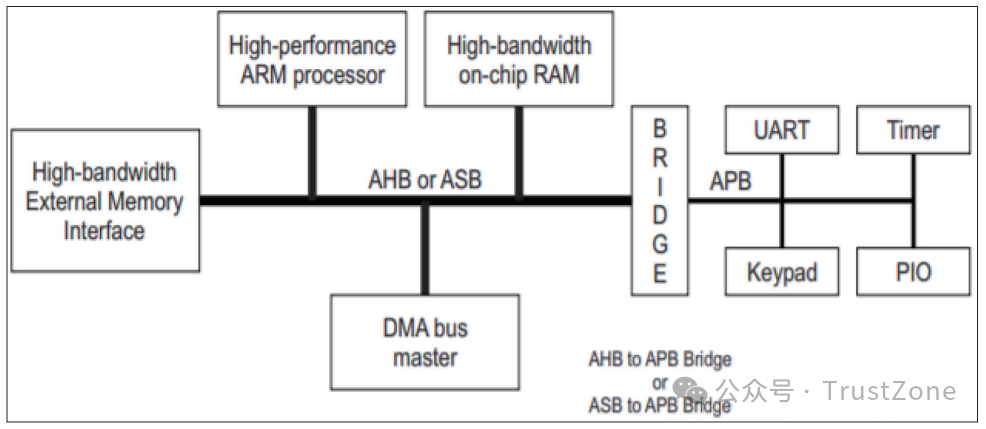

(1) 传统的SoC片上通信结构一般采用共享总线的方式。在共享总线结构中,所有的处理器和IP模块共享一条或多条总线。当有多个处理器同时访问一条总线时候需要有仲裁机制来决定总线的所有权。共享总线片上通信系统结构一般比较简单,且硬件代价也小。但是带宽有限,而且带宽也没法随着IP的增多而进行扩展。1996年,ARM公司提出的AMBA总线广泛应用于嵌入式微处理器的片上总线,现在已经成为事实上的工业标准。

图2 典型的AMBA总线系统

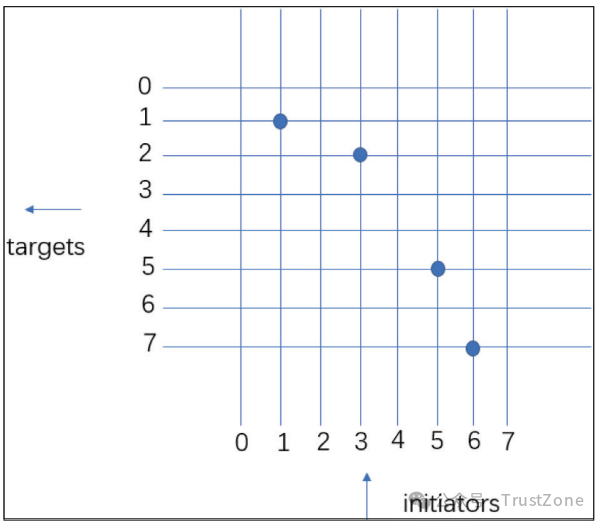

(2) 对于传统的共享总线,当多个处理器同时去访问不同的IP的时候,因为需要仲裁机制去决定总线的所有权,所以传统的总线方式在这种情况下就会造成一定的瓶颈,最大的问题就是访问的延时。在这种情况下,为了满足多处理同时访问的需求同时提高整个系统的带宽,一种新的解决方案Crossbar孕育而生,如图3所示一个典型的Crossbar结构。

Crossbar保证了多路通信同时进行的实时性,只要不是访问同一个目标设备,就不需要用到仲裁,大大减少了因为仲裁带来的瓶颈问题。但是随着设备数的增加,Crossbar的规模会以几何级数增长。所以通常我们通过桥接设备去级联多个Crossbar来支持设备的扩展。但是桥接设备可能会成为系统的瓶颈,增加传输的延迟。

图3 典型的单向8x8 Crossbar

实际应用中,我们通常也会采用Crossbar和共享总线相结合的方式,用桥接器将Crossbar网络和共享总线网络连接起来。

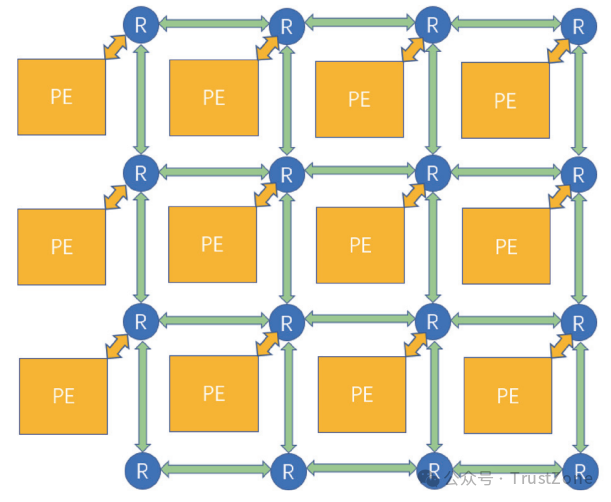

(3) 片上网络NoC带来了一种全新的片上通信方法,显著优于传统的总线式和Crossbar的性能。NoC是一种可扩展性更好的设计。在NoC架构中,每一个模块都连接到片上路由器,模块传输的数据则是形成了一个个数据包,通过路由器去送达数据包的目标模块。如图5所示是一个典型的NoC结构,图中的R表示Router,所有的Router可以是同步,但每个Router所连接的PE(Processing Element)与Router异步,自成一个时钟域(Clock Domain)。所以基于NoC的系统能更好地适应在复杂多核SoC设计中使用的全局异步局部同步时钟机制。另外,NoC可以支持各种扩展功能,比如流量控制(flow control)、服务质量(QoS)等等。因此,NoC是多核系统的最佳互联机制。

图5 典型的片上网络NoC结构

3. NoC在高端FPGA的应用

FPGA在日益增长的数据加速需求上正在发挥越来越重要的作用。

为了满足云计算和边缘计算中各种高性能应用的需求,FPGA作为一种可编程可定制化的高性能的器件逐步成为一条部署高吞吐量数据加速的快捷途径。

但同时这些高性能的加速应用也对高端FPGA提出了更高的要求,高算力、高带宽的数据传输以及高带宽的存储器。

片上网络技术已经比较广泛的用于SoC中,并取得了比较好的效果。近年来才慢慢用于FPGA中,Achronix创建了一种可最大限度地提高系统吞吐量的Speedster 7t FPGA芯片,创新地将二维片上网络(2D NoC)运用到了FPGA中,可以在逻辑阵列内的处理单元与各种片上高速接口和存储器接口之间高速地传输数据,真正实现了数据密集型应用吞吐量的最大化。

有了片上网络的FPGA如虎添翼,带来了传统FPGA所不及的很多优势,势必在各种数据加速应用中发挥巨大的作用。

4. NoC给Speedster 7t FPGA带来的优势

Achronix Speedster 7t FPGA拥有支持单通道速率112Gbps的SerDes、400G以太网MAC、PCIe GEN5控制器以及带宽高达4Tbps带宽的GDDR6控制器,为各种数据加速应用提供了高带宽的I/O接口和高带宽的存储器。在这类应用中,会有大量的数据进入FPGA进行处理,处理后的数据会通过FPGA输出,所以除了FPGA算力以外,数据移动速度直接决定了器件的性能以及用户的体验。

为了提高数据传输速率,Achronix在Speedster 7t FPGA中专门设计了不同于传统FPGA数据移动通道的片上网络。如图6所示。这是一个可横跨和垂直跨越FPGA逻辑阵列的创新性的、高带宽的二维片上网络(2D NoC),它不仅可以连接到所有FPGA高速接口、高带宽存储器接口,还可以作为内部逻辑之间的互连。

图6 Speedster 7t片上网络(NoC)结构

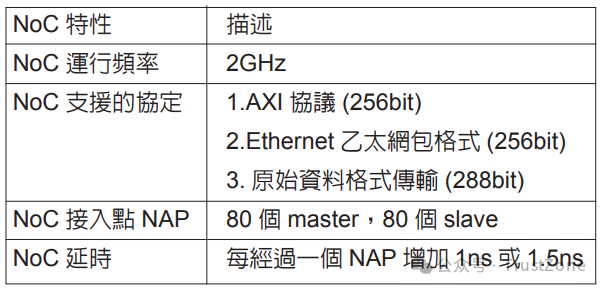

Speedster 7t FPGA上的二维片上网络(2D NoC)不是由可编程逻辑搭建,而是固化的ASIC逻辑实现,固定运行频率为2GHz,每一行或者每一列的NoC都可以作为两个单向256位实现双向的通路,所以每个方向可提供512Gbps的带宽,整个网络总带宽则能达到27Tbps。

下面的表格列出了Speedster 7t FPGA中NoC的特性。

表1 Speedster 7t FPGA中NoC特性

NoC为FPGA提供了以下几项重要优势:

(1) 大幅提高设计性能,解决一些高性能应用如400G以太网的性能瓶颈:通常在数据流经过400G以太网MAC解包以后会是一个超高位宽且需要运行在很高频率的处理,这在传统FPGA逻辑单元里面是无法实现的,而NoC就能解决性能瓶颈。

(2) NoC是在传统可编程逻辑之外额外增加的走线资源,所以在高资源占用设计中可以降低布局布线拥塞的风险。

(3)NoC包含了异步时钟转换,仲裁控制等逻辑,可以去替代传统的逻辑去做高速接口和总线管理等,所以利用NoC可以简化用户设计节省一部分传统资源(LE、FIFO和布线等)的使用。

(4)NoC部分是ASIC固化逻辑,功耗比传统的FPGA可编程逻辑实现要低很多。

(5) 利用NoC可以实现真正的模块化设计。传统高端FPGA设计通常是需要一个FPGA工程师团队来完成,每个工程师设计自己模块,在FPGA整个芯片里调试验证自己模块,然后再把各个模块连接成更大的完整设计,这时候会由于资源占用上升,通常需要花很多时间去优化布局甚至去修改设计以达到目标性能。而在Achronix Speedster7t 中可以让模块之间通过NOC互联,再借助对于单个模块功能性能调试完成后固定布局技术,甚至可以达到NoC互联后整体设计不需要额外联调的可能。这样可以大幅减少研发工作量和时间。

审核编辑:刘清

-

FPGA

+关注

关注

1634文章

21830浏览量

608037 -

摩尔定律

+关注

关注

4文章

637浏览量

79348 -

数据传输

+关注

关注

9文章

1972浏览量

65011 -

AMBA总线

+关注

关注

0文章

35浏览量

9646 -

晶体管

+关注

关注

77文章

9829浏览量

139396

原文标题:片上网络(NoC)技术的发展及其给高端FPGA带来的优势

文章出处:【微信号:Rocker-IC,微信公众号:路科验证】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

片上网络(NoC)技术的发展及其给高端FPGA带来的优势

基于FPGA的多时钟片上网络设计

利用片上高速网络(2D NoC)创新地实现FPGA内部超高带宽逻辑互连

中高端FPGA如何选择

基于遗传算法的片上网络虚通道分配算法

基于FPGA的多时钟片上网络该怎么设计?

技术文章:如何利用NoC来进行FPGA内部逻辑的互连

基于FPGA的NoC验证平台的构建

片上网络概述与FPGA研究(连载1)

浅析片上网络(NoC)技术的发展及其给高端FPGA带来的优势

浅析片上网络(NoC)技术的发展及其给高端FPGA带来的优势

评论