《半导体芯科技》杂志文章

作者:华斌,张世宇,刘瑞,周训丙,孙先淼,杨仕品;苏州智程半导体科技股份有限公司

引言

伴随着摩尔定律逼近其物理极限,芯片性能的进一步提升面临诸多障碍,因此,先进封装在半导体制造中扮演了越来越重要的角色。而在先进封装中,电镀是必不可少的关键环节。电镀主要用于形成铜、镍等金属镀层,构建RDL、UBM、Bump等关键结构,以及填充TSV结构,从而将芯片的引脚引出并在水平与垂直方向上重新排布,实现芯片与外部的I/O连接。随着各类电子产品的快速更新迭代,功能芯片不断向着微型化、复杂化的趋势发展,对RDL等结构的质量以及图形密度都提出了越来越高的要求,这对电镀的均匀性、成膜质量等性能都带来极大的挑战。

针对先进封装中电镀所面临的挑战,苏州智程半导体科技股份有限公司自主开发了包含多种改进技术的全自动电镀设备,在预防气泡生成、改善全局与局部的成膜均匀性、保障成膜致密性等方面,有着优良的表现。

预防气泡生成技术

随着封装的日益微型化、复杂化,RDL等结构的尺寸越来越小、排布密度越来越大,而TSV等结构也越来越多地被应用,这就需要在大量的极其微小且高深宽比的结构中电镀成膜。而在此类结构中,电镀液对晶圆表面的浸润变得十分困难,极易形成气泡且难以去除,导致电镀形成的结构存在孔洞等缺陷,进而导致电阻率过大,无法提供高性能的电气连接,恶化芯片的性能。

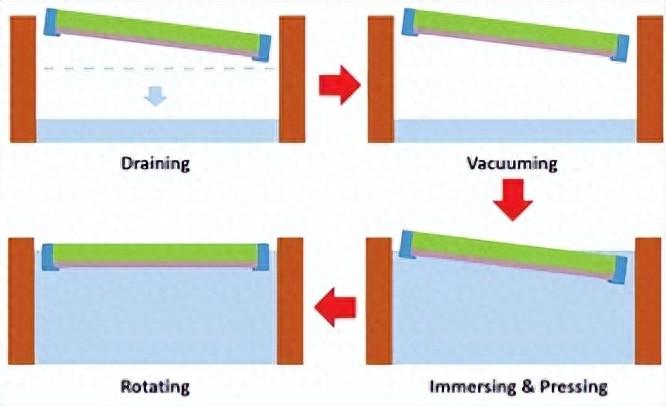

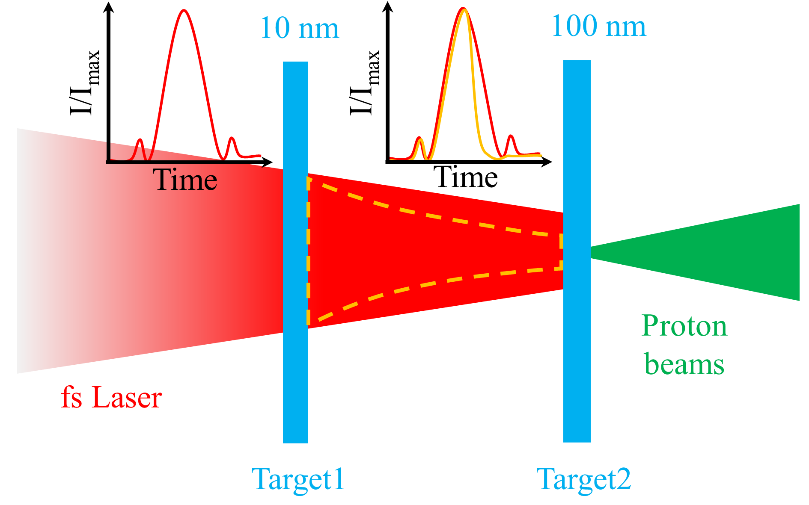

△图1:晶圆浸没过程示意图

针对气泡造成的危害,保证镀膜结构的高致密性与低电阻率,我们改进电镀槽的设计:

(1)在电镀槽中增加真空系统,令晶圆从真空环境中浸入电镀液,减少残余的空气滞留在微孔等结构中从而形成的气泡;

(2)采用电镀液增压技术,在晶圆浸没入电镀液后,增大电镀液的压力,一方面,减小表面张力从而令浸润更充分,另一方面,通过挤压气泡,令电镀液侵入气泡与晶圆的接触面,从而更容易地将已形成的气泡从晶圆表面剥离,减少对电镀的影响;

(3)设计可旋转式的晶圆夹具,令晶圆倾斜浸入电镀液中,以使表面残余空气可以顺利排出,完全浸入后再将晶圆旋至水平以进行正常的电镀。改进的晶圆浸没过程如图1所示。

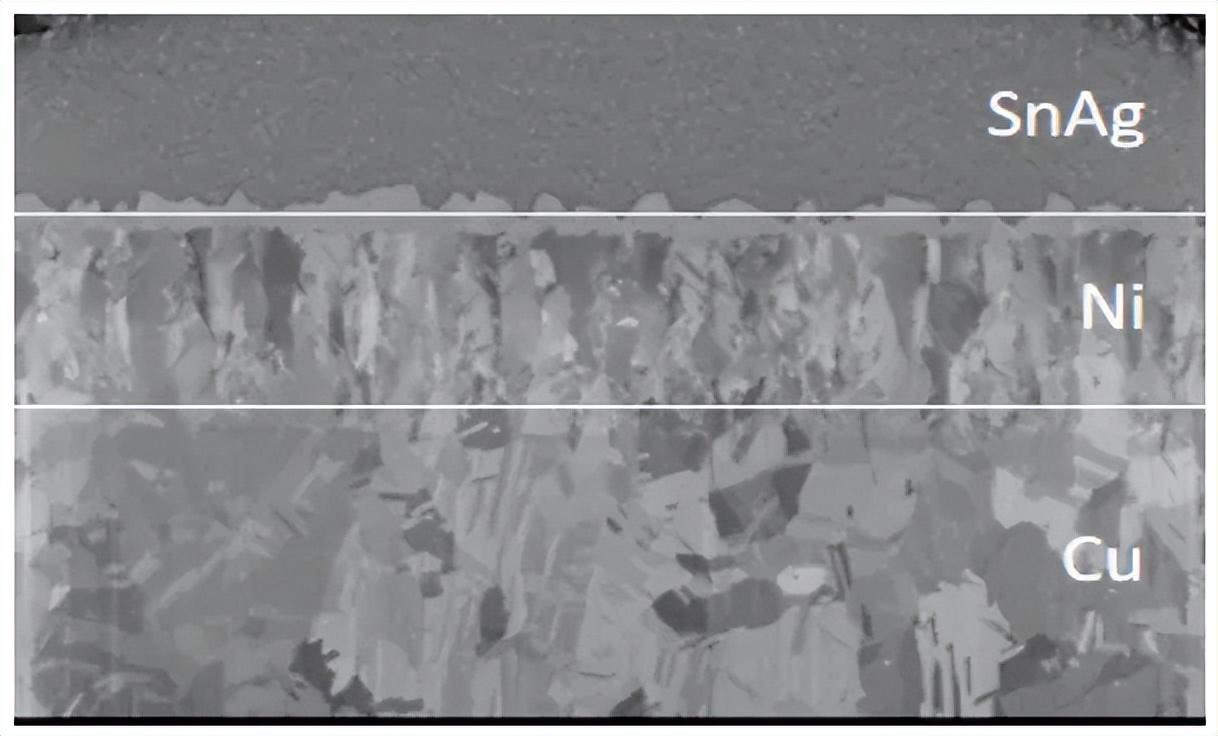

利用上述的改进结构与相应的晶圆浸没流程,在电镀进行前,避免了槽内气体残留在晶圆表面进而产生的气泡,保证了镀膜结构的致密性。如图2所示,所镀的Bump内部结构致密,没有微孔洞等缺陷。

图2:应用改良技术所镀的Bump结构的截面SEM图

全局电流密度调控技术

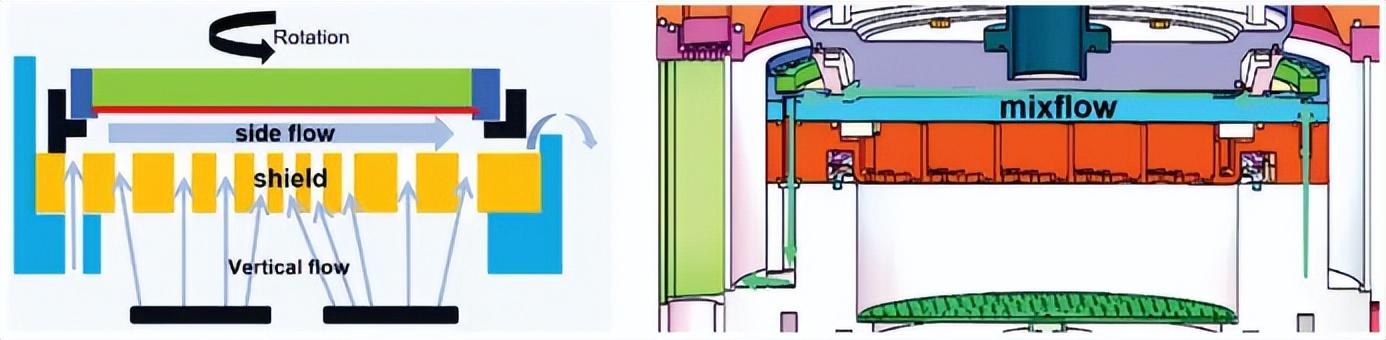

在电镀过程中,电镀液的流场分布影响着电流密度分布,进而对镀层厚度分布与成膜质量均有着重要影响。更大的电镀液流量会运输更多的金属离子,导致更大电流密度的同时,使镀层成膜速率更快,但过大的成膜速率也会导致成膜质量的下降,反之亦然。然而在常规的电镀过程中,流场分布往往难以调节。通常在整片晶圆中,膜厚从晶圆中心到边缘逐渐增大。除了流场的影响外,晶圆自身结构对电镀效果也会产生重要影响。晶圆表面有无芯片、受镀面积大小等情况,也影响着电流密度,进而影响镀膜的厚度与质量。其中,晶圆边缘不可避免地会出现无芯片区域,有相对较大面积的种子层金属裸露在外,导致边缘电流密度更大,进一步加剧了中心与边缘成膜速率的差异。

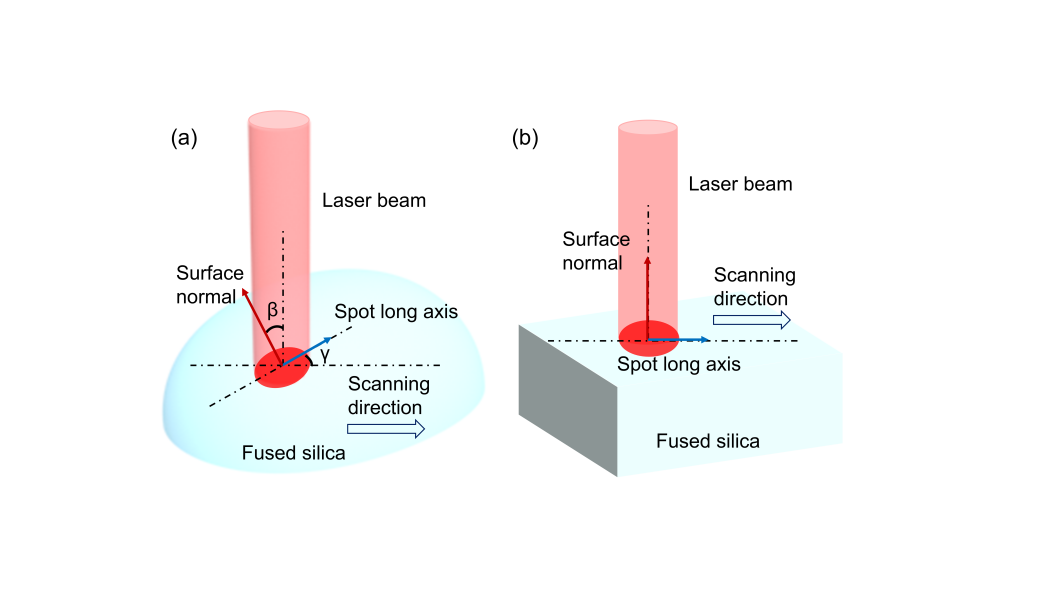

图3:挡板结构示意图

为了调控全局的电流密度分布,我们设计非均匀多孔遮挡板。如图3所示,遮挡板位于阳极与待镀晶圆之间,其中含有诸多通孔。通过调整通孔的尺寸、数量以及疏密排布,可灵活地调控各处电镀液的流量。这样,一方面可以调整晶圆表面总的电流密度,防止过快的成膜速率,从而提升整体的镀膜质量;另一方面,可令通孔密度从中心到边缘呈现从密到疏的变化,从而调节晶圆表面中心到边缘区域的电流密度,使各处成膜速率趋同,改善整体的膜厚均匀性。

此外,针对边缘区域过快的成膜速率,还可以增加O型遮挡环,如图4所示,对晶圆边缘区域进行遮挡,进一步抑制边缘区域过快的成膜速率。由于所制芯片尺寸的不同,晶圆边缘无芯片区域的尺寸也会有所不同,对此可针对性地使用不同宽度的O型环,以灵活性地应对不同的生产需求。

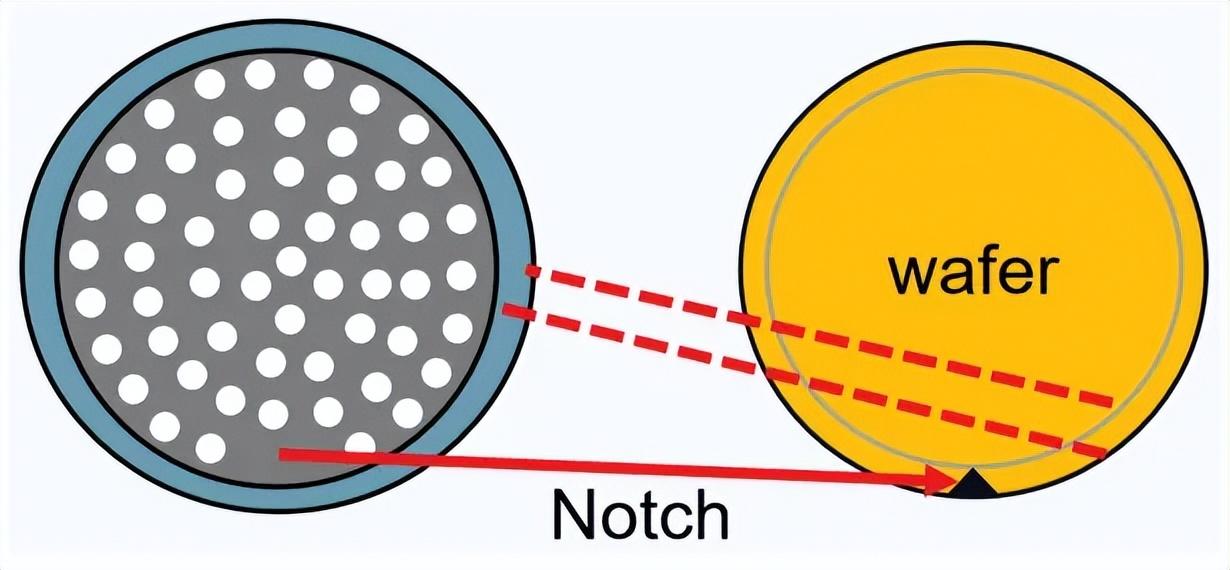

图4:O型遮挡环以及Notch局部遮挡示意图

局部电流密度调控技术

在电镀过程中,与边缘区域的情况类似,晶圆上Notch附近区域通常没有芯片,从而有更多裸露的金属表面。因此,Notch附近区域的电流密度显著高于其它区域,导致该区域成膜速率过快。

针对Notch处的局部不均匀问题,我们采取一种局部电流密度调控技术。首先,如图4所示,在多孔遮挡板中,在与Notch对应的部位设置无孔区域,以起到局部遮挡的作用。其次,我们开发晶圆转速可灵活调控的控制系统。在电镀过程中,通过适当的参数设置,令晶圆变速旋转,当Notch随晶圆旋转至与遮挡板上无孔区域重合时,显著降低晶圆转速或令晶圆短暂停止旋转,当Notch转离无孔区域时,再恢复转速。这样,使得在整个电镀过程中,Notch在较多的时间内处于被遮挡状态,降低了Notch周边区域在全过程中的平均电流密度,从而抵消该处成膜过快等一系列问题。以同样的方式,晶圆表面任意区域因特殊的结构而产生的局部成膜速率过快问题,均可以进行针对性的调控。

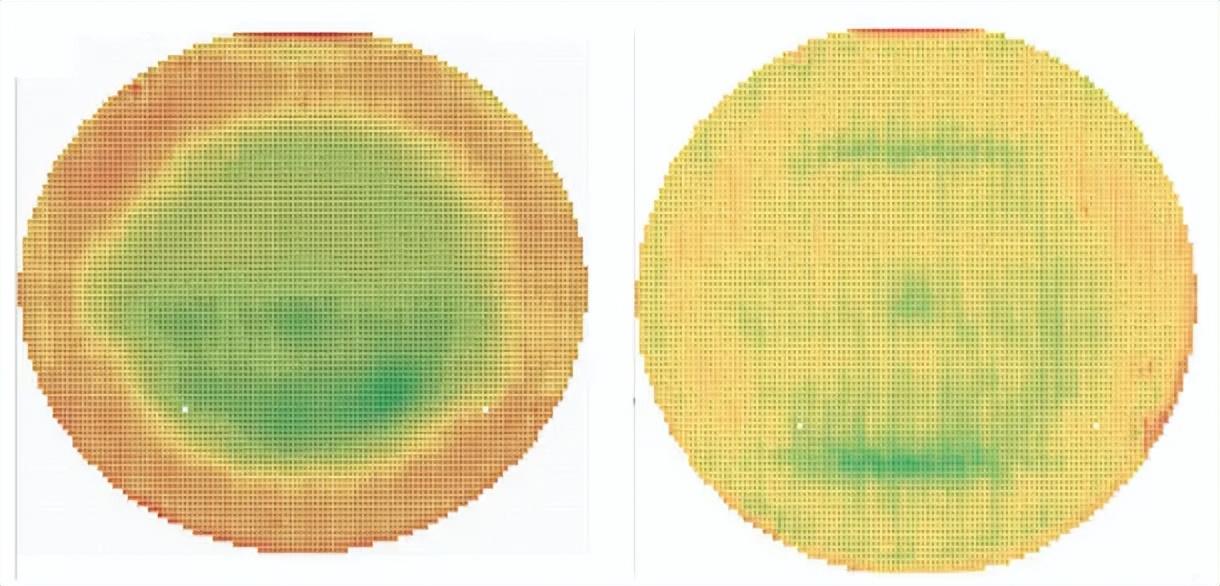

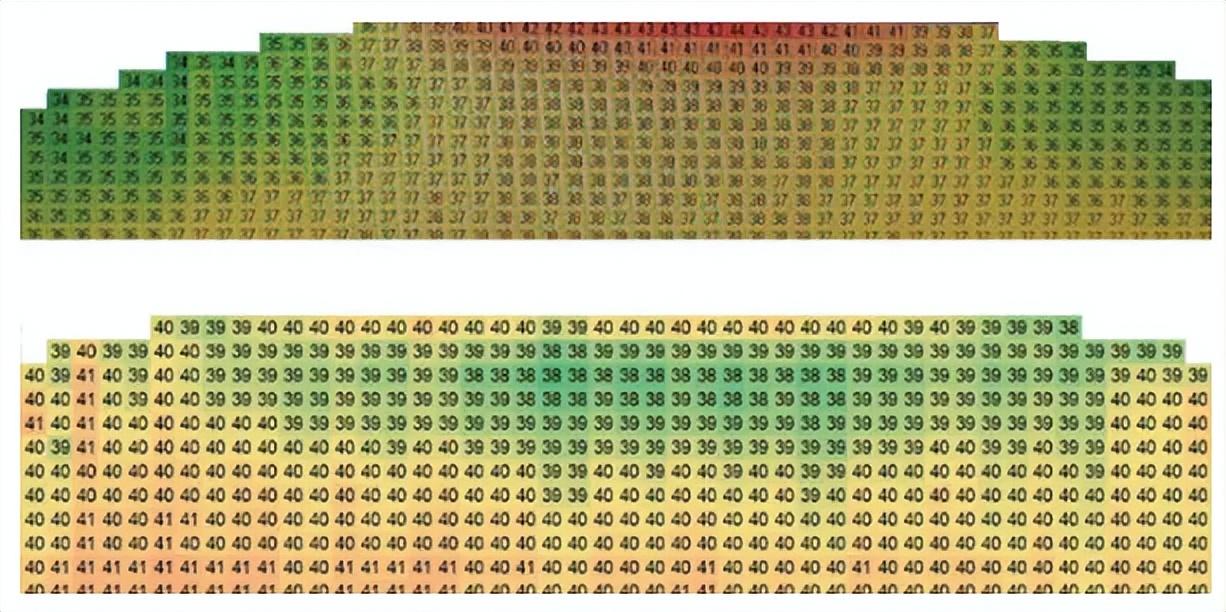

通过上述全局与局部电流密度的调控,我们实现成膜均匀性的大幅改良,分别如图5与图6所示。图中,颜色越偏向红色代表膜厚越大,越偏向绿色代表膜厚越小,颜色差异越小代表膜厚越均匀。

图5:晶圆表面全局膜厚均匀性的改善效果(左图为改善前,右图为改善后)

图6:晶圆表面Notch处的局部膜厚均匀性的改善效果(上图为改善前,下图为改善后)

结束语

以上是针对先进封装中电镀所面临的挑战,我们自主开发的一些改进技术。苏州智程半导体科技股份有限公司成立于2009年,主要从事半导体领域湿制程设备的研发、生产与销售。产品广泛应用于集成电路制造、先进封装、化合物半导体、MEMS等领域。公司研发场地包含百级、千级无尘室等,具备半导体设备整机开发及相关机械结构、电气控制测试开发能力。通过多年的技术积累,已经成功掌握包括薄片晶圆背面清洗刻蚀技术、防静电晶圆清洗技术、Mini/Micro LED超声波去胶技术、电镀均匀性增强技术、晶圆干燥技术、高精度控温技术、缓冲脉冲的液体阻尼器技术等在内的多种半导体设备产品核心技术,并拥有多项自主知识产权。此外,公司开发了模块化生产模式,可以根据客户需求灵活配置不同的湿法工艺。

审核编辑 黄宇

-

封装

+关注

关注

128文章

9339浏览量

149065 -

电镀

+关注

关注

16文章

478浏览量

25898

发布评论请先 登录

2025年联接领域十大创新进展回顾

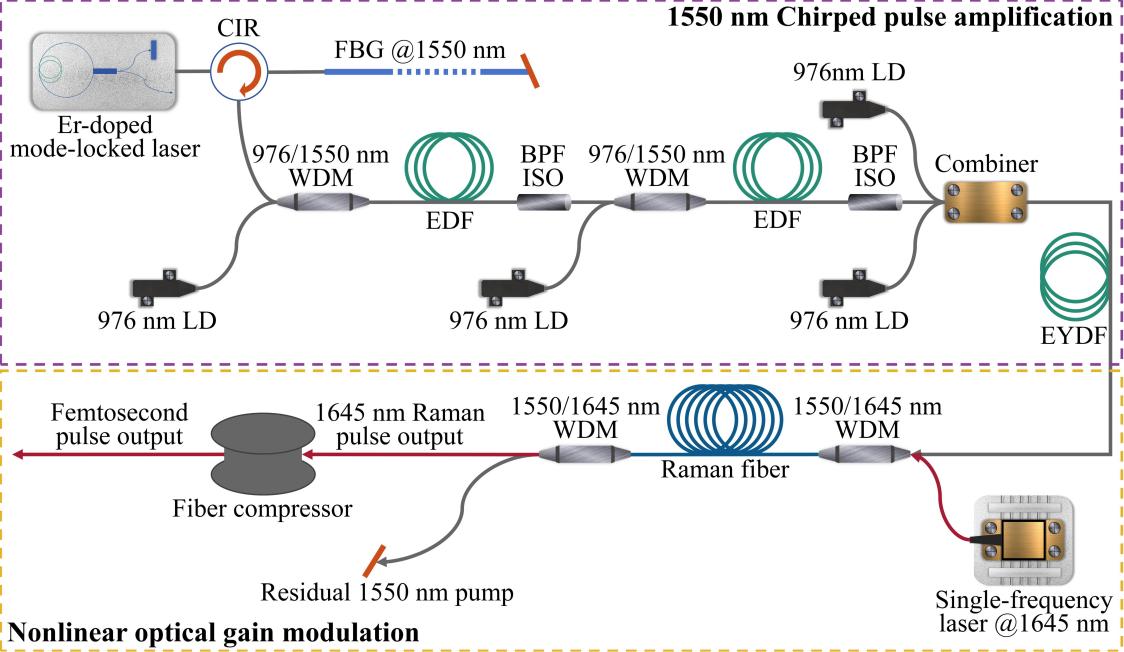

上海光机所在高功率U波段飞秒激光方面取得新进展

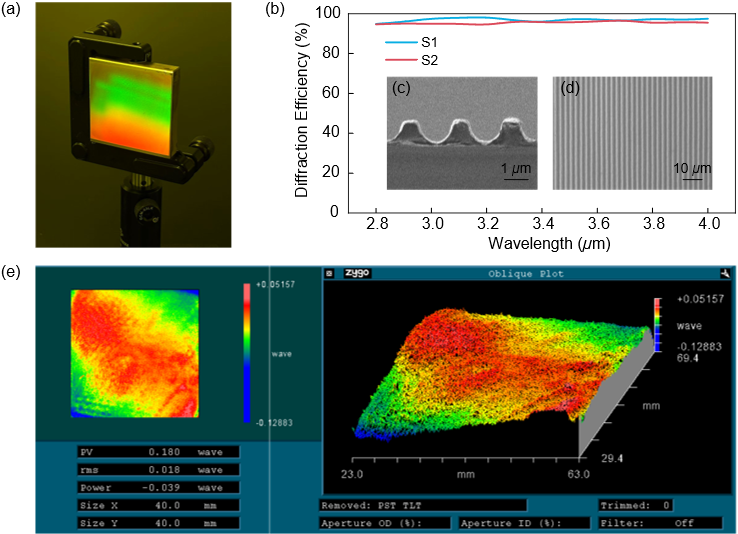

上海光机所在中红外光谱合束光栅研究方面取得新进展

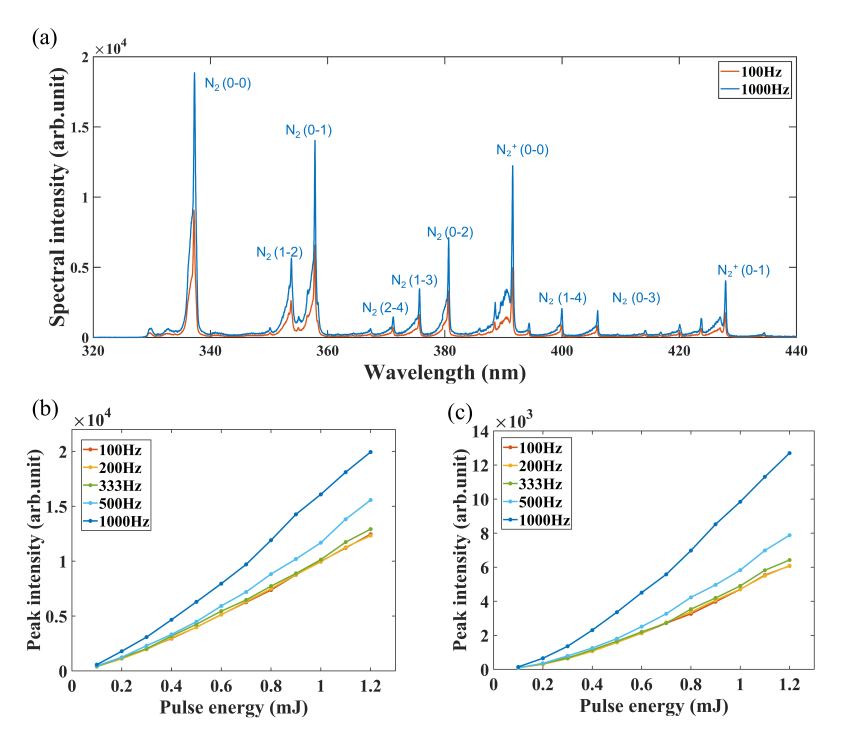

上海光机所在脉冲累计效应影响光丝荧光研究中取得新进展

芯科科技分享在物联网领域的最新进展

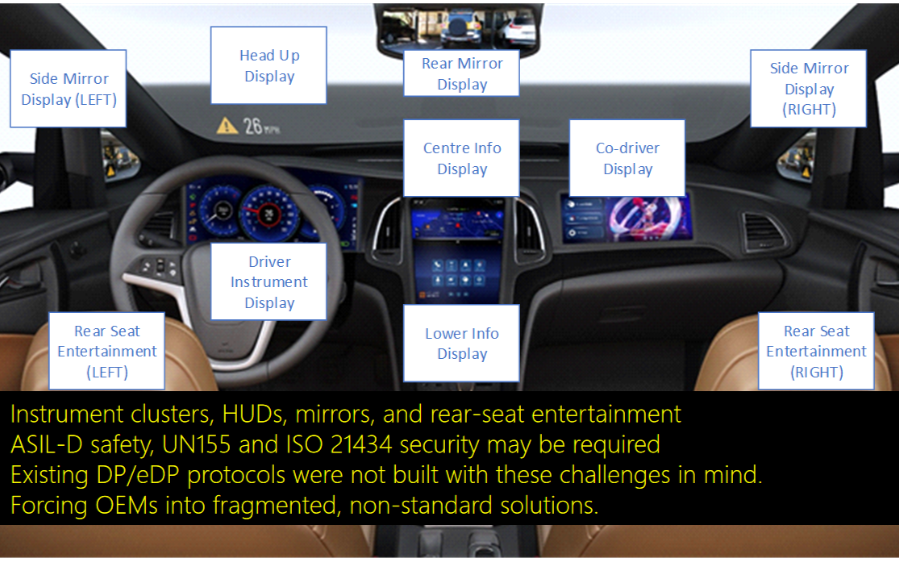

DisplayPort汽车扩展标准新进展,显示系统灵活性和效率大幅提升

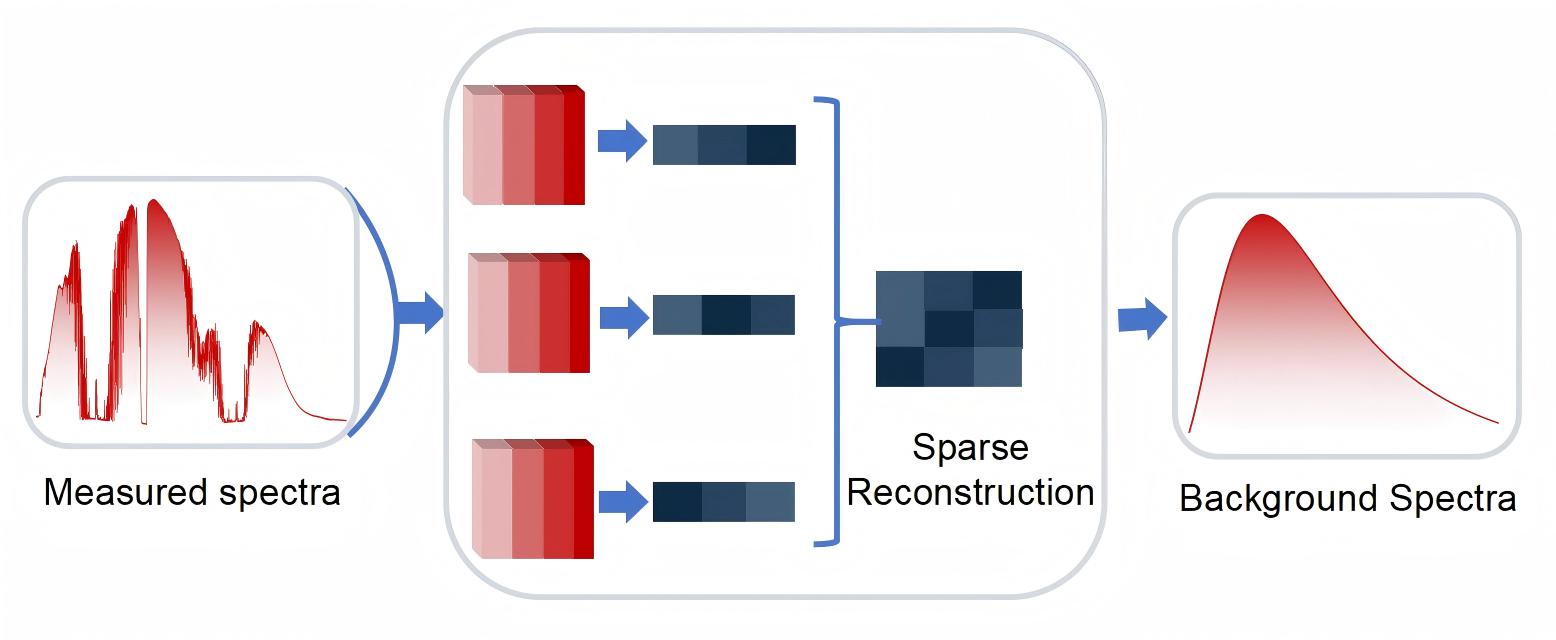

科学岛团队在红外光谱遥感分析方法领域取得新进展

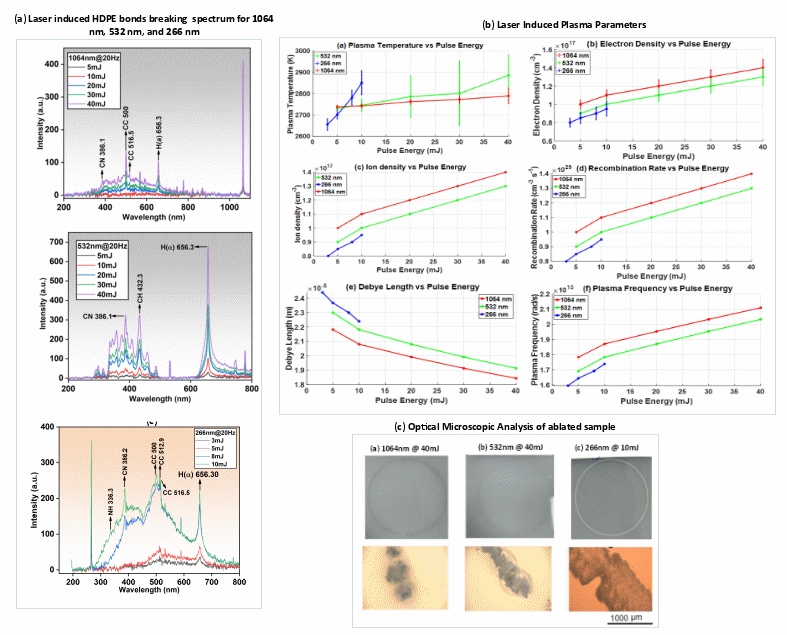

上海光机所在不同激光谐波裂解HDPE方面取得新进展

上海光机所在激光驱动离子加速方面取得新进展

上海光机所在激光烧蚀曲面元件理论研究中取得新进展

东风汽车转型突破取得新进展

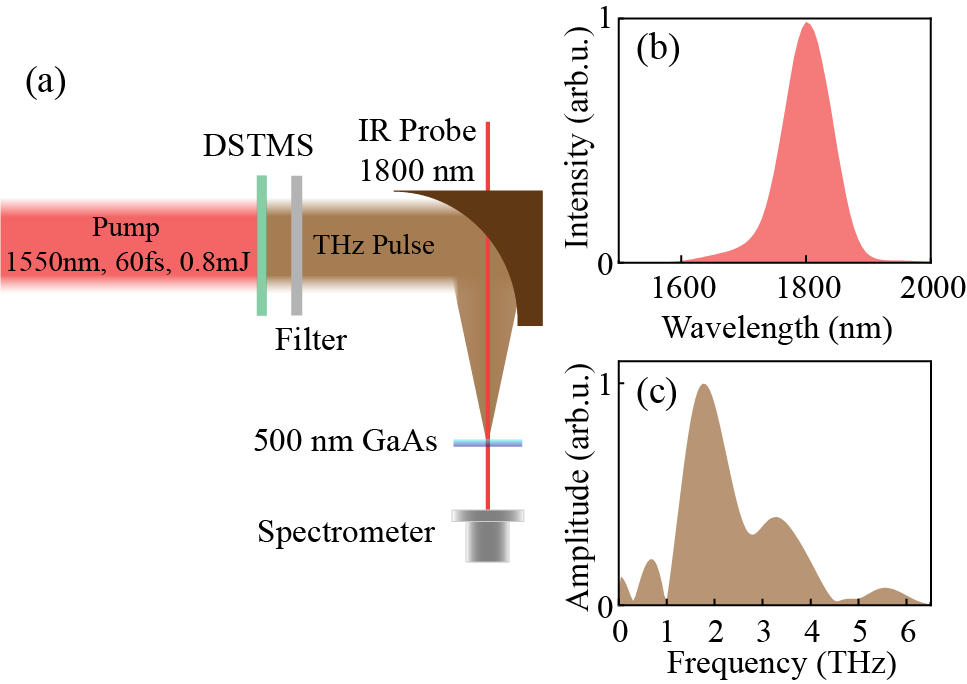

上海光机所在强场太赫兹对砷化镓偶次谐波调控研究方面取得新进展

面向先进封装的电镀技术新进展

面向先进封装的电镀技术新进展

评论