这是一种驱使人们自愿构建自己的CPU的痒。我们开始思考我们理解中的空白,这个空白潜伏在逻辑门和触发器如何单独工作以及机器代码如何控制完全组装的处理器之间。在硬连线电路开始随着软件不断变化的曲调跳舞的神奇区域中究竟发生了什么?

事实证明,这种痒折磨着足够多的人,以至于有商业套件供想要将 CPU 组装在一起以看到(或听到)它的制造商使用,并且网络上充斥着自制的 4 位和 8 位 CPU,其架构是 1970 年代工程师所熟悉的。我应该知道——我自己做了一个。但后来我开始怀疑:我能不能用一些最新技术来构建自己的CPU?我可以设计自己的完全兼容的 32 位 RISC-V 中央处理器吗?

RISC-V 是一个开源架构,大约有 11 年的历史,现在开始在由 x86 和 ARM CPU 架构主导的世界中取得进展。罗伯特·巴鲁克(Robert Baruch)的工作提醒了我RISC-V的可能性,他大约两年前开始了一个类似的项目,但尚未完成他的处理器,部分原因是他必须不断重新设计他早期构建的组件,以满足不断发展的设计需求。

RISC-V 设计的模块化特性使我能够将 Pineapple One 构建为一堆可单独测试的 10 x 10 厘米 PCB,这些 PCB 具有不同的功能(顺时针方向,从左上角开始):VGA 驱动器;公羊;传输层;移;阿鲁;寄存器文件;控制单元;程序计数器;只读存储器。詹姆斯·普罗沃斯特

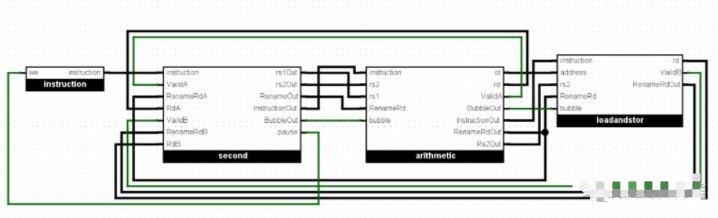

取而代之的是,我首先在逻辑电路仿真器Logisim Evolution中构建了我的完整设计,我将其命名为Pineapple One。在查阅了官方 RISC-V 手册以及 David Patterson 和 John Hennessy 的著作《计算机组织与设计,RISC-V 版》(Elsevier,2017 年)的第一版,并将 Logisim 推向了极限,我在六个月内对 Pineapple One 进行了工作模拟,满足了基本 RISC-V CPU 的要求。

在实现 RISC-V 架构时,我惊讶地发现,与我早期自制 CPU 中使用的传统复杂指令集相比,该架构的意义要大得多。冗余被消除,处理器的寄存器(存储 CPU 工作内存的暂存器)更加灵活。另一大优势是RISC-V是一个有据可查的模块化设计,所以我知道每个模块必须做什么。我的目标是以我自己的方式设计每个模块,但要确保它的性能符合 RISC-V 标准。(这决定了我的 CPU 是 32 位的,因为根据定义,RISC-V 指令至少那么长。

从物理上讲,菠萝一号分布在垂直堆叠的八个方形印刷电路板上,这些电路板的边长约为10厘米,外加一个处理VGA显示接口的卡。它使用了 230 多个集成电路,主要来自 74HCT 系列逻辑芯片。我最大的挑战是实现桶形移位器,这种电路可以围绕寄存器中的位以可控的量进行移位。我首先尝试了一种需要 80 多个组件的快速实现,但尽我所能,我无法让它适合我的 PCB。因此,我采用了一种低组件方法,基本上暂停了 CPU 其余部分的运行,直到我的变速杆完成启动。由于菠萝一号的走线很长,与单芯片CPU相比,我还很难管理寄生电容和阻抗,这意味着要调试一些非常奇怪的行为。

忠诚shopping_cart删除

詹姆斯·普罗沃斯特(James Provost):虽然有规定指令的长度范围在16位和理论上无限的数量之间,但这里是RISC-V指令的四种核心类型的固定32位格式。一些指令将操作码与其他功能字段相结合来定义行为,而另一些指令则允许将多个源寄存器与所谓的即时数据相结合,并将结果放置在目标寄存器中。

我使用Arduino微控制器测试了每块板,以模拟计算机其余部分的输入,并监控输出的正确性。我用3D打印了一个漂亮的外壳来容纳整堆PCB和输入/输出连接器,这样就可以将键盘和VGA显示器直接连接到Pineapple One上。有 4 个通用 I/O 端口 — 2 个 8 位输入和 2 个输出。

我的朋友 Jan Vykydal 帮助我设置了一个符合 RISC-V 的编译器才能正常工作,所以我用 C 语言编写了一些系统软件和演示程序。编译器生成机器代码,我使用一个 Python 脚本来获取代码并将其闪存到 CPU 的内存中。尽管 Pineapple One 的运行频率仅为 500 千赫兹,但这仍然足够快,可以实时玩像 Snake 这样的简单电脑游戏,而且 512 KB 的程序内存和 512 kB 的 RAM 已经足够了。

最终,我想稍微升级一下处理器,以便它可以运行更复杂的程序。我还想添加更多扩展板,例如声卡。您可以在 Hackaday 上找到原理图和物料清单,但最终将其作为套件提供给其他有兴趣了解当代 CPU 设计的人会很棒。

审核编辑 黄宇

-

芯片

+关注

关注

457文章

51345浏览量

428268 -

cpu

+关注

关注

68文章

10922浏览量

213284 -

RISC-V

+关注

关注

45文章

2334浏览量

46743

发布评论请先 登录

相关推荐

64位RISC-V CPU发展现状和未来前景

基于risc-v架构的芯片与linux系统兼容性讨论

RISC-V 生态架构浅析

科普RISC-V生态架构(认识RISC-V)

瑞萨基于RISC-V核心架构的预编程ASSP器件

ARM与RISC-V架构的区别是什么?

两大架构RISC-V 和 ARM 的各种关系

聚焦RISC-V架构,避免主流CPU架构制约

为什么我们提升了RISC-V的会员等级

芯来科技CEO彭剑英:RISC-V构建自主可控CPU繁荣生态

TenstorrentInc首席CPU构架师 练维汉:助力数字化升级的RISC-V AI 高性能CPU

从头开始构建 RISC-V CPU使用分立逻辑芯片,通过最热门的新架构构建功能惊人的 CPU

从头开始构建 RISC-V CPU使用分立逻辑芯片,通过最热门的新架构构建功能惊人的 CPU

评论