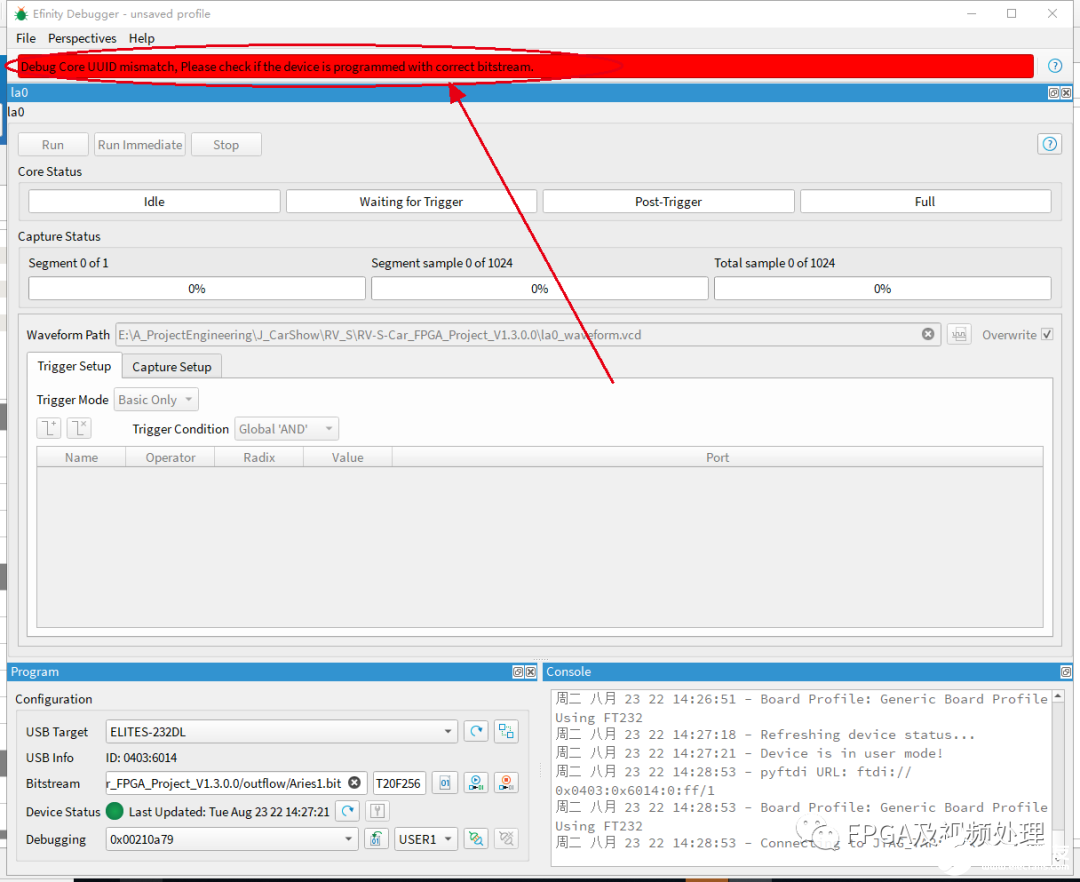

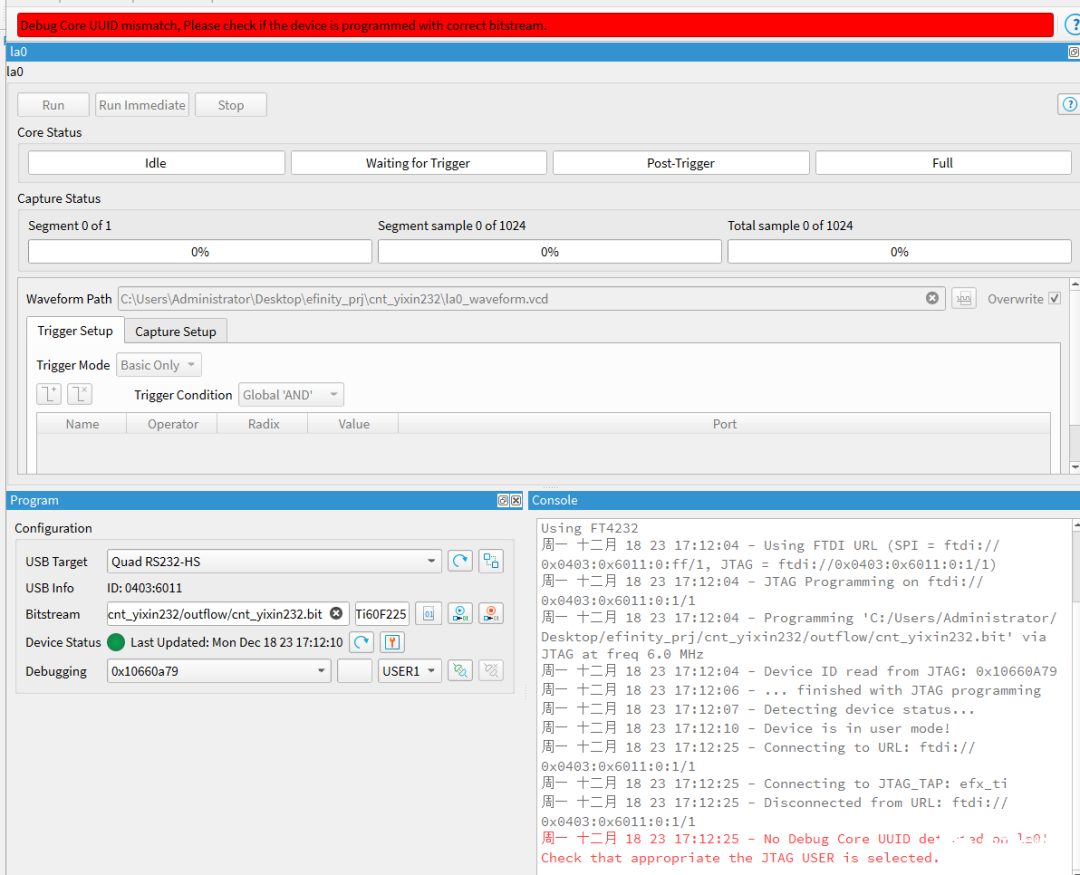

(1)UUID mismatch

Efinity在Debug时会出现UUID mismatch错误。很多刚开始使用的人经常遇到。下面我们做一个总结。欢迎遇到案例时共同分享。

一般有以下几种原因

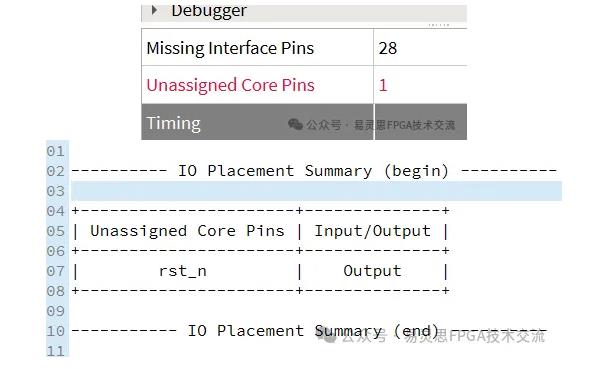

(1)程序没运行起来。这种情况CDONE信号没有拉高,说明程序没有加载到FPGA,也可以说程序没有运行起来。

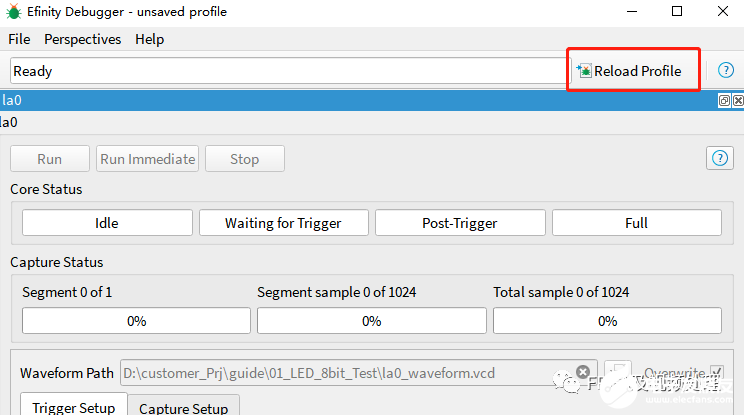

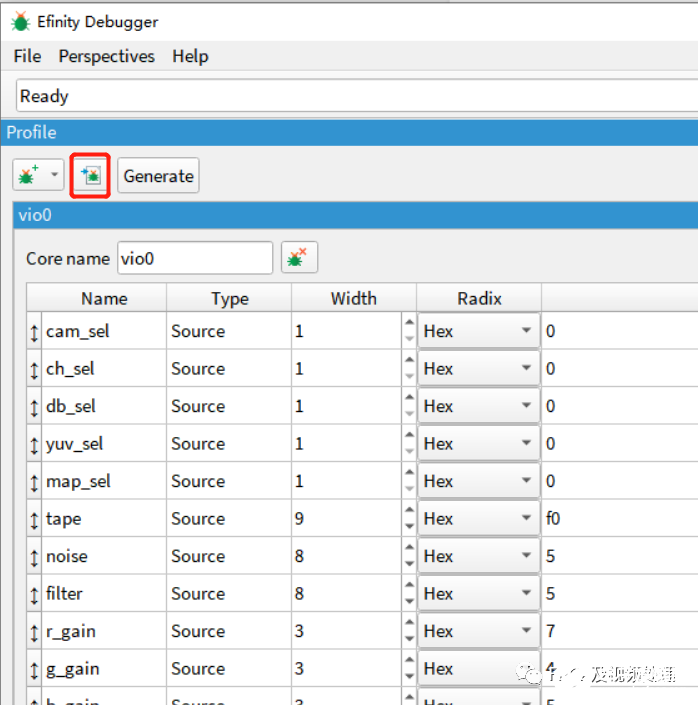

(2)配置文件与debugger文件——即json文件不对应。需要手动从Perspectives -> Profile Editor中重新import Profile,即找到json文件,目前已经添加了upload功能功能解决该问题,在界面的右上角,会提示upload。

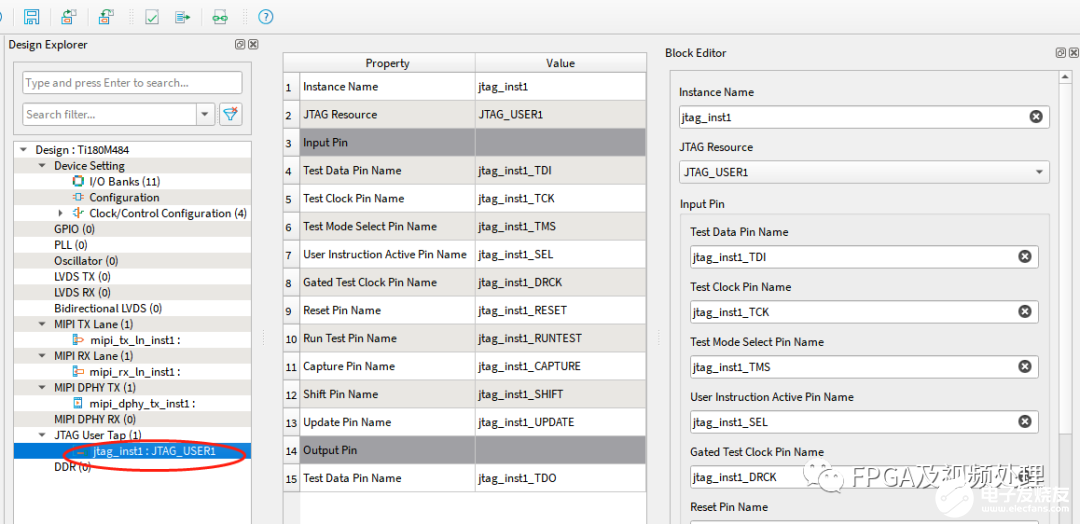

(3)通过Open Debugger添加vio或者la,但是实际上没有在Interface Designer中添加JTAG_USER_TAP。

(4)没有添加Debug;

(5)JTAG_USER_TAP接口与debug_top例化部分连接出错,比如名字不对。

(6)TI60会存在A版本与A1版本有区别不连接不上,2022.8月份之后不存在该问题。

(7)添加了vio和la但是没有添加debug_top.v到工程中,依然编译过去,连接时也会提示UUID mismatch.

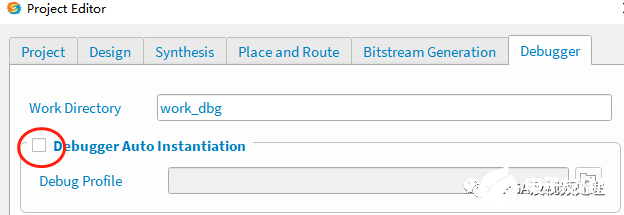

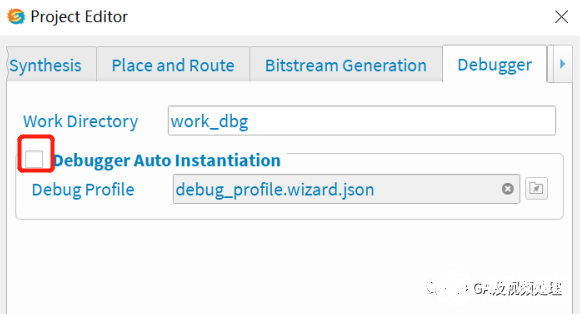

(8)Debugger Auto Instantiation没有打开。

(9)有客户第一次的设计调试信号线 TCK TDO TMS(10K上拉) TDI(10K上拉)是直连的使用正常。第二次在TCK,TDO,TMS和TDI串联了100欧的电阻,并且TCK进行了4.7K下拉,就出现了UUID mismatch。

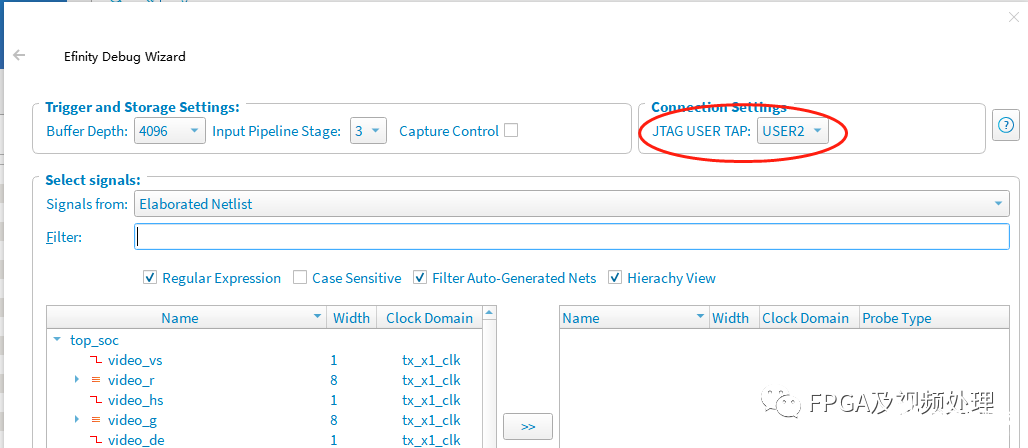

(10)JTAG USER TAP不对应。比如下图选择了USER2,但是连接时选择的是USER1.

(11)T20以下器件在通过JTAG配置时必须要连接CRESET,T8F81还需要连接SSN信号。如果没有连接的话,可能存在看似JTAG配置成功,但是实际上配置的程序并没有运行,依然只运行了上电第一次配置的程序。此时UUID肯定也不匹配,因为新程序没有运行。

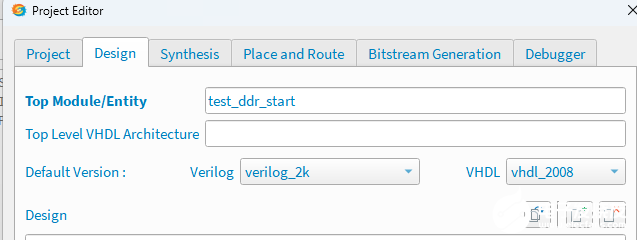

(12)没正确指定top文件。如果没有指定top文件,软件会自动选择top文件,很多时候就是用户自己定义的top文件。

(13) JTAG下载器连接有问题。

说明:upate1 添加了(12)(13)两项。

(14)另外我们也遇到了程序设计并没有问题,也会出现以下情况,这时候可能要重启软件。

(2)Debugger不运行

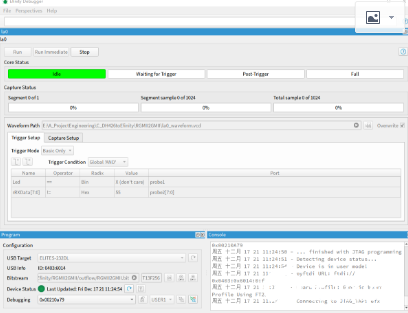

现象:点击run和run immediate都没有运行,Core Status处于Idle状态。

原因:(1)时钟没有运行。

(2)时钟性能不好,或者时序不好。

(3)gitwave打不开

原因:

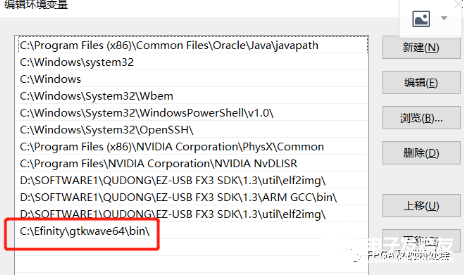

(1)注意环境变量路径为"C:Efinitygtkwave64bin",不能添加"gtkwave.exe"

(2)正确的添加环境变量后,要重启efinity才能打开

(4)debugger关不掉

原因:(1)关闭工程,重新打开。

(5)直接通过josn文件打开Debugger。

打开Perspectives -> Profiles Editor

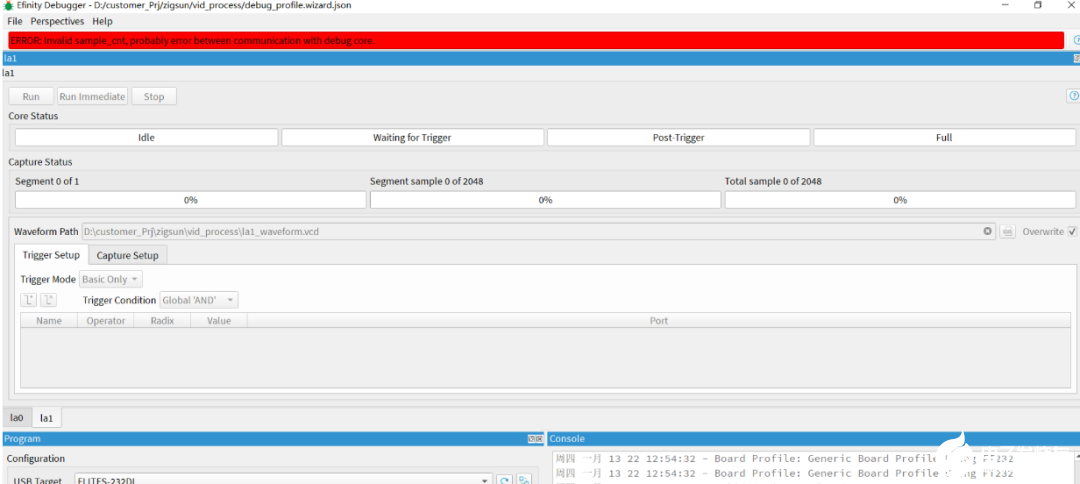

(6)Error:invalid sample_cnt, probably error between communication with debug core.

1)JTAG下载正常,能连接上,但是采集数据不正确

2)过一会儿之后报下面的错误

Error:invalid sample_cnt, probably error between communication with debug core.

3)la0是好的,la1会出上面的错误

原因:(1)时钟没有进行约束。

(2)时钟不稳定,比如pll没有锁定。

(7)Open Debugger打不开

(1)没有安装USB驱动;

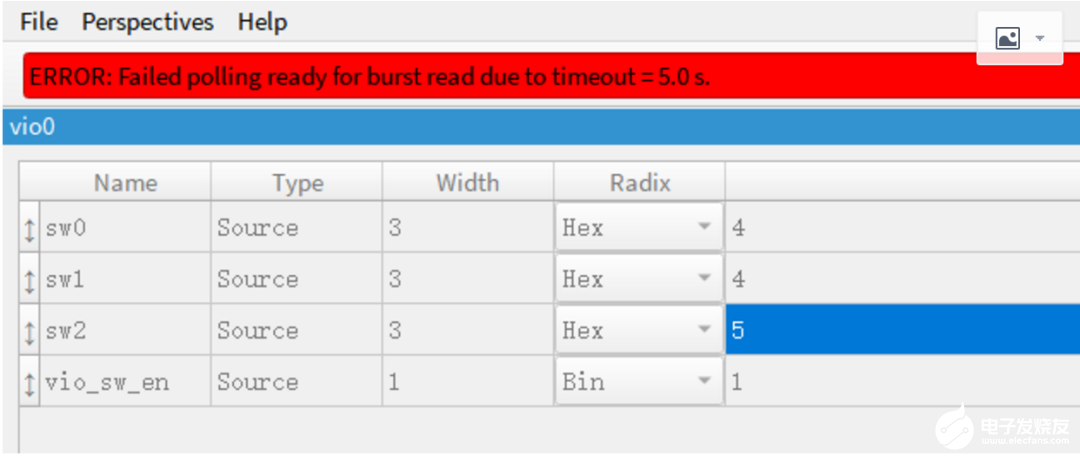

(8)ERROR:Failed polling ready for burst read due to timeout= 5.0 s

结论:可能没有用连续时钟采样 。

-

DEBUG

+关注

关注

3文章

89浏览量

19879

发布评论请先 登录

相关推荐

Efinity软件安装-v5

Efinity FIFO IP仿真问题 -v1

Efinity编译生成文件使用指导-v1

SC171开发套件V1 技术资料

CMSIS-RTOS V1与V2的区别是什么?

LT8228从V1到V2是BUCK模式,从V2到V1是BOOST模式,请问这个模式是固定的吗?

Efinity Interface Designer报错案例-v1

Efinity debugeri常见问题总结-v1

Efinity debugeri常见问题总结-v1

评论