电子发烧友网报道(文/周凯扬)对于任何一个芯片大厂而言,在ISA的选择上都是相当谨慎的。ISA不仅决定了芯片开发的难易程度,也决定了与之绑定的软件和开发生态,甚至可能会影响到市场面临的竞争。然而在这个重要的选择上,我们却发现不少大厂开始发力RISC-V。

瑞萨:授权到自研

瑞萨作为MCU大厂之一,尤其是在汽车领域,经过多年的积累与开发,旗下已经有了多条MCU产品线。在32位MCU上,有基于自研CISC内核的RX系列,也有基于Arm Cortex-M架构的RA系列。即便如此,瑞萨还是决心开拓第三条产品线,而且是基于RISC-V架构。

其实瑞萨很早就开始RISC-V相关的布局了,比如2021年推出的汽车控制域管理MCU RH850/U2B,就集成了来自NSI-TEXE开发的MIMD加速器核心,基于RISCV架构的DR1000C。

DR1000C不仅取得了ISO 26262 ASIL D级别的认证,凭借其并行处理器的特性,可以帮助MCU卸载一些繁重的计算工作,比如模型预测控制、AI推理以及传感器数据处理等等,不仅适合工业自动化设备,也很适合用于汽车MCU中辅助雷达或其他传感器的融合计算。

除此之外,瑞萨也与晶心科技达成合作,继续推出了用于特定市场的RISC-V产品,比如集成了RISC-V核心的ASSP和MPU产品,包括基于RISC-V的电机控制ASSP MCU,以及64位的RZ/Five,前者主要用于工业控制、人机交互等场景,而后者则主要用于网关控制。

在RISC-V上,瑞萨不仅选择了授权第三方内核,也有了自研内核的野心,为其通用MCU再度开辟一条可选产品线。2023年11月30日,瑞萨宣布推出第一代32位RISC-V CPU内核,计划面向物联网、消费电子、医疗保健和工业系统打造一个全新的开放灵活平台,也作为其已有RX系列和RA系列的补充。

瑞萨自研RISC-V内核 / 瑞萨

作为其首个自研RISC-V内核,其CoreMark/MHz达到了3.27,要低于此前用到的晶心科技N22核心,也低于其自研的RXv1核心。由此看来其首个自研RISC-V核心的规模并不高,主要用于超低功耗的MCU设计。

近日,瑞萨也发布了基于该自研内核打造的首个通用32位RISC-V MCU,R9A02G021,正是一款超低功耗的48MHz MCU产品。R9A02G021集成了128KB代码闪存,4KB数据闪存,以及16KB的SRAM和丰富的IO。在开发工具上,瑞萨的e² studio依然为R9A02G021提供了IDE支持,除此之外,IAR和SEGGER也迅速跟进了对这一MCU的开发支持。

即便有了新的RISC-V内核,并不代表瑞萨会放弃其他产品线的后续开发,从其路线图规划上可以看出,无论是RL78、RX、RA系列,瑞萨都有产品扩充和增强的计划,以实现更高的性能和集成度,并加入一定的AI/ML功能。与此同时,瑞萨或许也会在未来开发更高规格的RISC-V内核,用在更高性能的RISC-V MCU设计上。

高通:率先发力可穿戴和汽车

高通作为Arm阵营的坚定拥护者,这些年也在慢慢向RISC-V倾斜一部分开发资源。在2022的RISC-V全球峰会上,高通高管宣布,早在2019发布的骁龙865 SoC中,高通就已经将RISC-V用到了微控制器的设计中,并已经出货了上亿个RISC-V核心,尽管高通并未透露后续的骁龙手机SoC是否继续沿用这一设计,但已经足以说明这家手机芯片大厂对于RISC-V的重视了。

去年一则与RISC-V相关的新闻相信不少人都已经看过了,那就是高通联合博世、英飞凌、恩智浦、Nordic几家大厂,共同成立了一家名为Quintauris的RISC-V初创企业。该公司的目标是通过支持下一代硬件开发来推动RISC-V在全球的普及,也就是加速RISC-V架构产品的商业化,提供参考架构。据其官网描述,这家公司的初期重点放在了汽车应用上,也就是说未来高通很可能会根据这一参考架构,推出对应的RISC-V汽车芯片产品。

在联合成立RISC-V公司的消息发布后不久,高通又联合谷歌共同宣布,双方将加强合作,基于RISC-V架构开发下一代Snapdragon Wear平台,从而为谷歌的下一代Wear OS解决方案提供支持,而且高通明确表示,他们将在全球范围内推行RISC-V的可穿戴解决方案。不过,RISC-V在这一新的Snapdragon Wear可穿戴硬件平台以什么定位出现,我们尚不清楚。

从过去的可穿戴芯片来看,高通主要采用性能中等的Arm内核来打造相关的SoC。比如从Wear1100到Wear 3100,其都是基于Arm Cortex-A7来设计CPU部分的。直到2020年推出的Wear4100+,才开始使用4核A53 CPU加协处理器的设计。

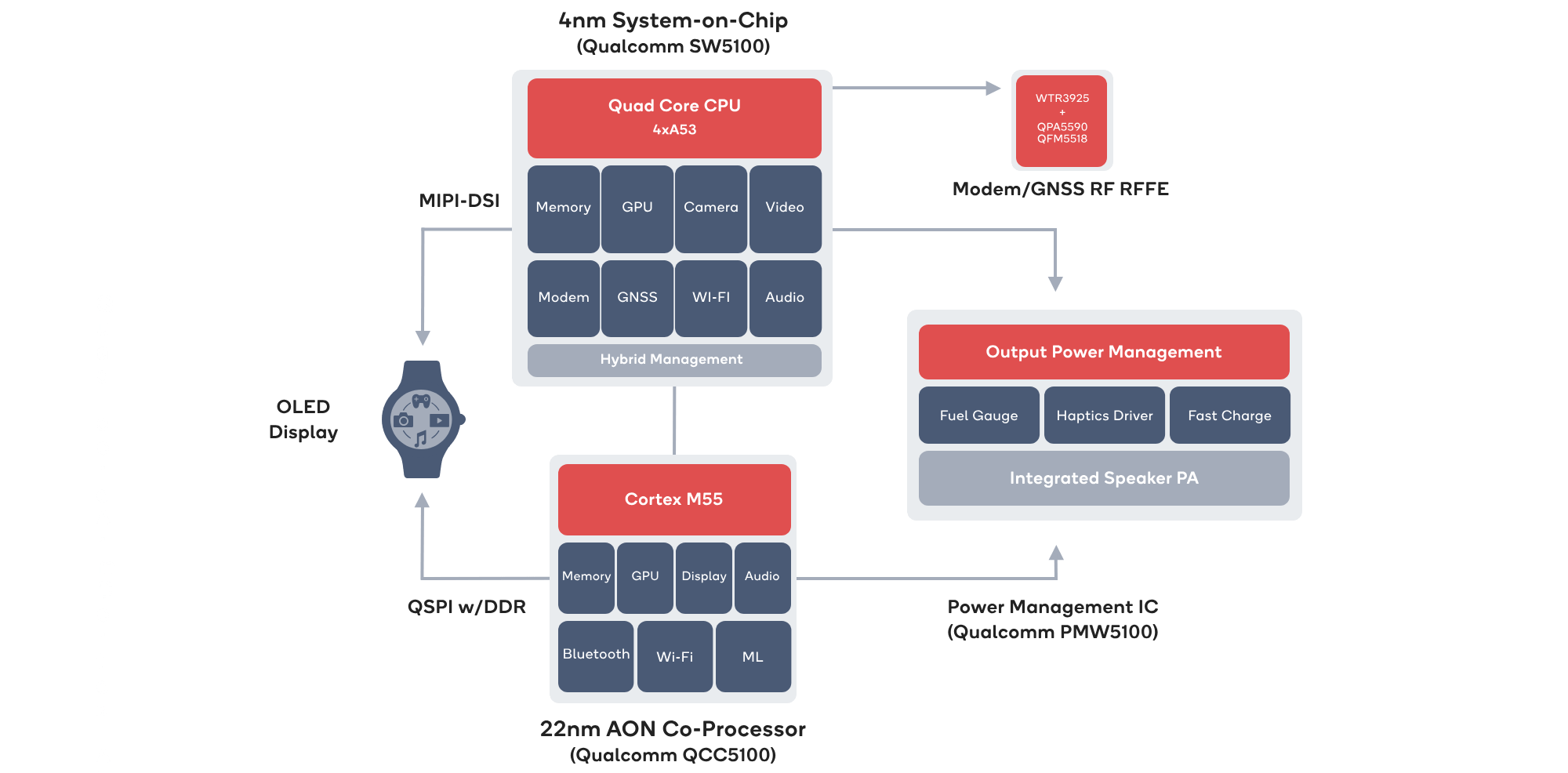

Snapdragon W5+ Gen1可穿戴硬件平台 / 高通

在最新的W5+ Gen1平台中,高通依然沿用了4核A53加协处理器的设计,只不过主CPU工艺从12nm换成了4nm,而协处理器也从QCC1110(Cortex-M0)换成了QCC5100(Cortex-M55)。依照高通的说法,其协处理器主要是用来支持谷歌Wear OS、ASOP和RTOS,而且其只需要用到22nm的成熟工艺。

在高通与谷歌的联合公告中,也明确表示新平台主要用于支持Wear OS,这样看来高通新的RISC-V硬件既有可能作为主CPU,也有可能作为协处理器。无论如何,两家公司都已经加入了RISC-V的软件生态系统(RISE)中,无论是哪种设计方案,都会给RISC-V在可穿戴领域的软件开发带来新的突破。

MIPS:主打高性能处理器

曾几何时,MIPS也是市场主流的RISC处理器架构,甚至有望比肩Arm、x86,就连国内的龙芯在发展LoongArch架构之前,用的也是MIPS架构。MIPS以设计具有多流水线、多流水线和支持虚拟化的处理器闻名,甚至目前不少ADAS系统都还运行在MIPS处理器上。

然而在成功推出了几代32位和64位RISC处理器之后,MIPS并没有超越x86,反而被崛起的Arm掩盖了光芒。MIPS在这期间甚至尝试过开源方案,但依旧陷入了无人问津的境地。因此2021年3月,MIPS宣布终止了MIPS架构的开发,同时公司整个转向RISC-V架构。

尽管在收购和转型中,MIPS经历了各种波折,但手上还是留有一些微架构专利,也有丰富的处理器设计与开发经验,对于同为RISC的RISC-V来说,MIPS本身还是存在不小的优势。

2022年,MIPS推出了其全新开发的RISC-V处理器系列,eVocore,目前只有P8700和I8500两大多处理器IP核。其中P8700针对数据中心的高性能计算场景设计,P8700采用了少见16级流水线设计,加上多发射乱序执行和多线程,而且可拓展性可以使其支持到512个内核。MIPS表示其单线程性能远超市面上现有的其他RISC-V CPU IP,但并没有提供具体的跑分参数。

除了P8700这类高性能通用CPU核心外,MIPS近期的动向表明其也在发力AI计算。比如MIPS在今年迎来了新的首席架构师Brad Burgess,此前他在SiFive参与了P870处理器的乱序矢量单元设计。此外,他们也在美国开设了新的研发中心,计划与当地大学合作,开发汽车、数据中心和嵌入式市场的AI计算创新方案。

写在最后

可以看到,对于绝大多数大厂而言,RISC-V都是一个愈发可行的产品设计方向。这也充分说明了RISC-V的开放性,以及更加成熟的软硬件开发环境,和更低的设计风险。尽管多数厂商目前依然抱着尝试的心态,但随着RISC-V生态的持续壮大,相信会有更多的大厂投入RISC-V的怀抱。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

RISC

+关注

关注

6文章

468浏览量

84048 -

RISC架构

+关注

关注

0文章

5浏览量

5424 -

RISC-V

+关注

关注

46文章

2357浏览量

46959

发布评论请先 登录

相关推荐

贸泽电推出RISC-V技术资源中心

Mouser推出内容丰富的RISC-V资源中心,为设计工程师提供新技术和新应用的相关知识。随着开源架构日益普及,RISC-V从众多选项中脱颖而出,成为开发未来先进软硬件的新途径。从智能手机和IoT设备,再到高性能计算,

RISC-V内核是如何与FPGA内核进行资源共享的?

我们知道RISC-V内核支持的精简指令集,FPGA又是要求性能相对比较高的模块,这两者在同一个产品中可否共存?若能,两者的资源又是通过哪些接口进行传输共享的呢?

发表于 10-27 17:05

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未来 !

加入RISC-VAdvocate行列!我们正在寻找来自世界各地的RISC-V爱好者,通过全球推广和参与,成为支持RISC-V进步的关键参与者。作为一名RISC-VAdvocate,您将

万物智联时代,RISC-V与AI的融合之路该如何走?

人工智能与机器学习专委会主席谢涛发表了《万物智联时代RISC-V+AI之路》演讲,分析了RISC-V与AI技术的结合及其发展路径探索。他在发言中,尽管国产AI芯片在硬件

RISC-V Summit China 2024 青稞RISC-V+接口PHY,赋能RISC-V高效落地

沁恒在历届峰会上分享RISC-V在MCU领域的创新成果,和大家共同见证了本土RISC-V产业的成长。早在第一届RISC-V中国峰会上,沁恒就公开了青稞RISC-V系列量产芯片的关键技术

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,赋能RISC-V高效落地

01 老朋友伴您走过每一届峰会

沁恒在历届峰会上分享RISC-V在MCU领域的创新成果,和大家共同见证了本土RISC-V产业的成长。早在第一届RISC-V中国峰会上,沁恒就公开了青稞RISC-

发表于 08-30 17:37

2024 RISC-V 中国峰会:华秋电子助力RISC-V生态!

第四届RISC-V中国峰会(RISC-V Summit China 2024)于8月21日至23日在杭州盛大召开,成为RISC-V领域的一次重要盛会

2024 RISC-V 中国峰会:华秋电子助力RISC-V生态!

第四届RISC-V中国峰会(RISC-V Summit China 2024)于8月21日至23日在杭州盛大召开,成为RISC-V领域的一次重要盛会。峰会汇聚了RISC-V国际基金会的

发表于 08-26 16:46

risc-v的发展历史

RISC-V的发展历史可以追溯到2006年左右,当时David Patterson和其他研究者开始探索创建一个开放和可扩展的指令集架构(ISA)。以下是RISC-V发展的主要里程碑:

一、起源与初步

发表于 07-29 17:20

rIsc-v的缺的是什么?

RISC-V作为一种开源的指令集架构(ISA),自其诞生以来就受到广泛关注和应用,但它也存在一些不足之处。以下是RISC-V架构目前存在的主要缺点:

1. 性能问题

相对于专用ISA的性能差距:尽管

发表于 07-29 17:18

RISC-V的MCU与ARM对比

开发者提供了丰富的资源和支持,降低了开发难度和成本。

成本

RISC-V :由于RISC-V是开源的,因此使用RISC-V的MCU可以显著降低芯片设计和制造的费用。此外,

发表于 05-27 15:58

RISC-V有哪些优点和缺点

RISC-V作为一种开源的指令集架构(ISA),具有一系列显著的优点和潜在的缺点。以下是RISC-V的主要优点和缺点概述:

优点:

开源与开放性:RISC-V是开源的,这意味着任何人都可以获取、修改

发表于 04-28 09:03

解锁RISC-V技术力量丨曹英杰:RISC-V与大模型探索

4月12日,第二期“大家来谈芯|解锁RISC-V技术力量”在上海临港新片区顶科永久会址举办,本期沙龙聚焦RISC-V技术,围绕AI时代的RISC-V市场机会、RISC-V在汽车领域的应

什么是RISC-V?RISC-V的关键技术

RISC-V不仅仅是一个流行语;它建立在坚实的技术基础之上,使其有别于其他指令集架构 (ISA)。RISC-V的核心是基于精简指令集计算(RISC)原则,强调效率和性能。

发表于 03-26 09:34

•3925次阅读

RISC-V 基础学习:RISC-V 基础介绍

复用资源,因此,其面积开销是比较大的,但是由于可以让不同的流水线级数同时做不同的事情,而达到流水的效果,提高了性能,优化了时序,增加了吞吐率。

9. RISC-V

在了解了 RISC 和 CISC 两种

发表于 03-12 10:25

设计资源倾斜,大厂们的RISC-V之路

设计资源倾斜,大厂们的RISC-V之路

评论