引言:基于K7+C665x为核心的电路板中用到了DDR3存储芯片,现将FPGA外接DDR3时硬件设计中的一些心得做一个简单的分享。

1. DDR3与K7-410T互联设计

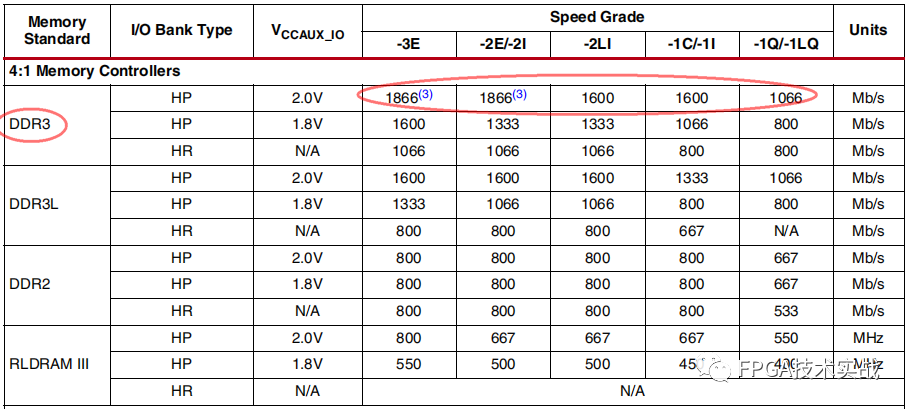

在数据速率带宽约束方面,DDR3运行速度受限于其与K7-410T FPGA互联的I/O Bank 管脚以及FPGA器件的速度等级。如下表所示,当FPGA选定时,如需DDR3运行最大工作频率时,需要将DDR3互联至FPGA的HP I/O Bank上,同时也要将Vccaux_io的供电电压调整为2.0V。

表1、FPGA I/O支持DDR3外设最大接口数据速率

DDR3本身可以互联至普通的HR I/O Bank上,但是速度性能是下降的,通常在互联时会将DDR3互联至HP I/O Bank上,以保证器件性能发挥至最佳。

2. DDR3与K7-410T原理图设计

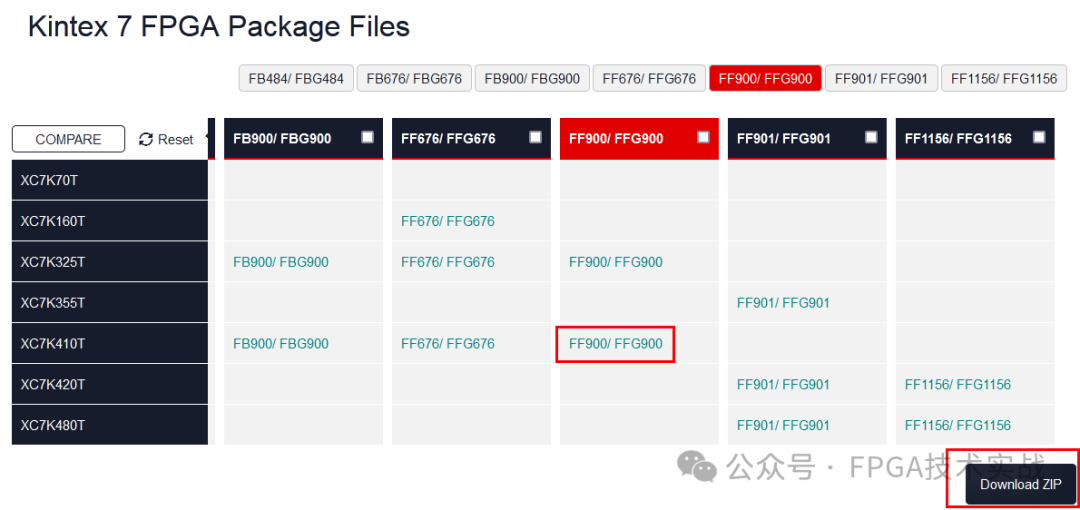

在确定好将DDR3连接至HP Bank上后,在具体原理图设计时,可以在Xilinx官网下载一份Pinout资料,如下图所示。

图1:FPGA Pintout下载

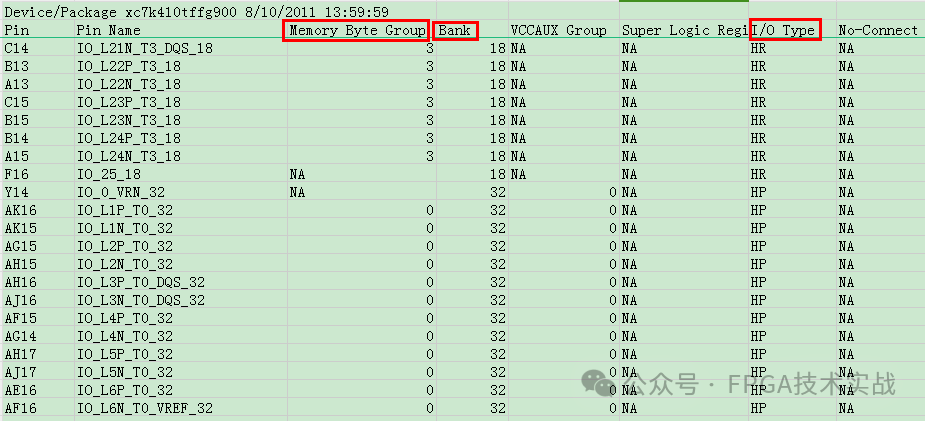

在下载的pinout.csv文件中,可以方便的查看IO所在的存储器Byte组,Bank以及I/O类型等,如下图所示。图中存储器Byte一个Bank内按照T0、T1、T2、T3划分,除了DQS,同一一个Tx组内的DQ IO是可以互换的。

图2:FPGA Pintout文件内容

在绘制原理图时,可以先按照Byte组来进行IO放置,最终IO的放置,还要根据PCB工程师布线的便利性,在同一个Tx组内进行调整。有两点需要注意的:

1)DDR3管脚IO的分配强烈建议通过Vivado软件例化DDR3 IP核验证FPGA IO分配的正确性!

2)如果DDR3所在的BANK上有其他外设IO,也要一起验证IO,确保满足IO bank电平兼容性。

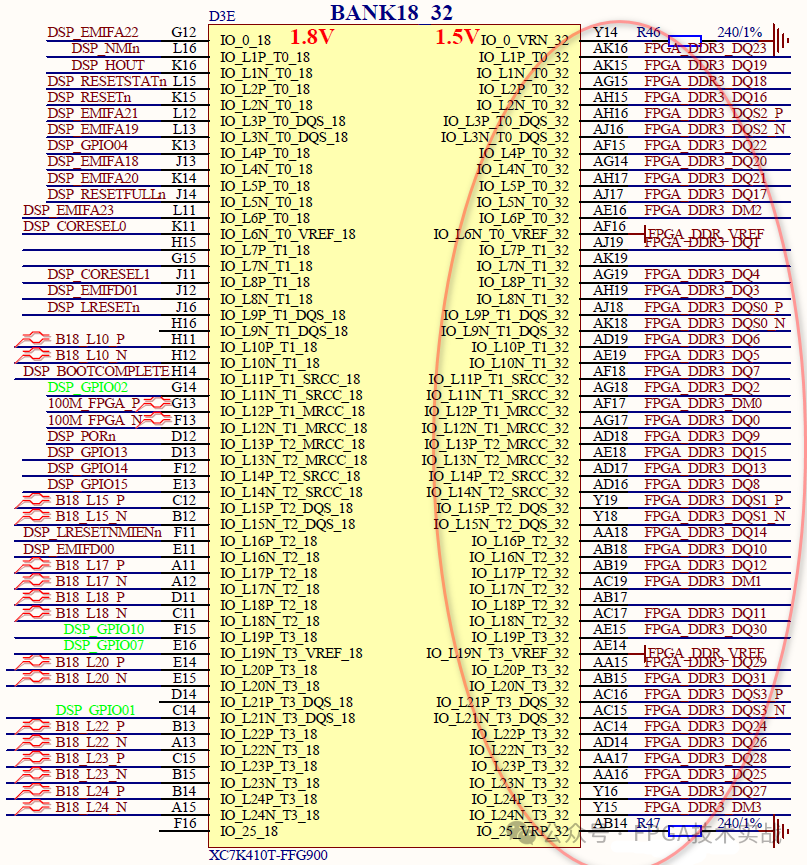

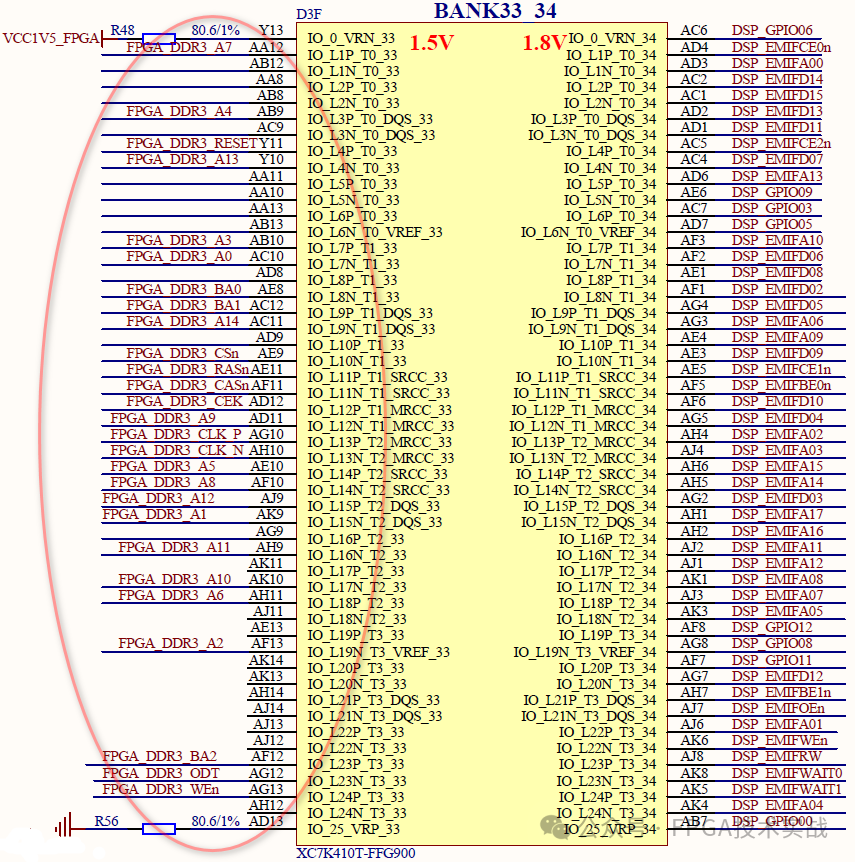

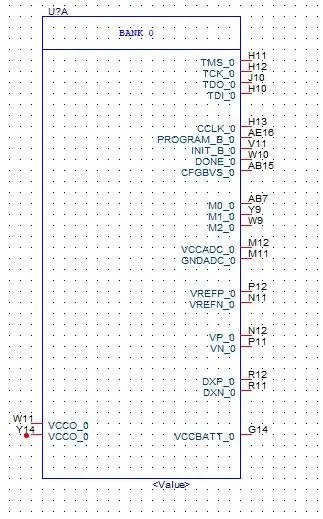

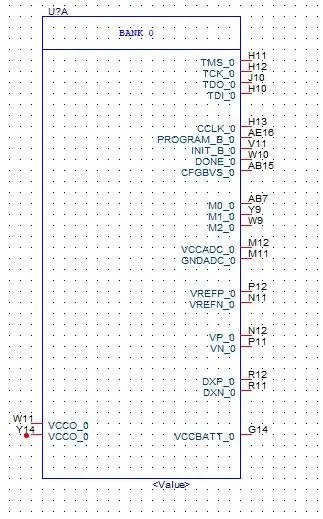

DDR3的 CLK_P/CLK_N时钟建议放置在FPGA芯片_SRCC或者_MRCC专用时钟管脚上,以保证时钟最佳性能。DDR3地址信号及控制信号放在DQ临近的HP Bank上即可。本设计中,DDR3 DQ数据组放置在HP Bank32上,时钟、地址及控制信号放置在HP Bank33上。如下图所示。

图3:FPGA DDR3 DQ数据组

图4:FPGA DDR3 时钟、地址及控制组

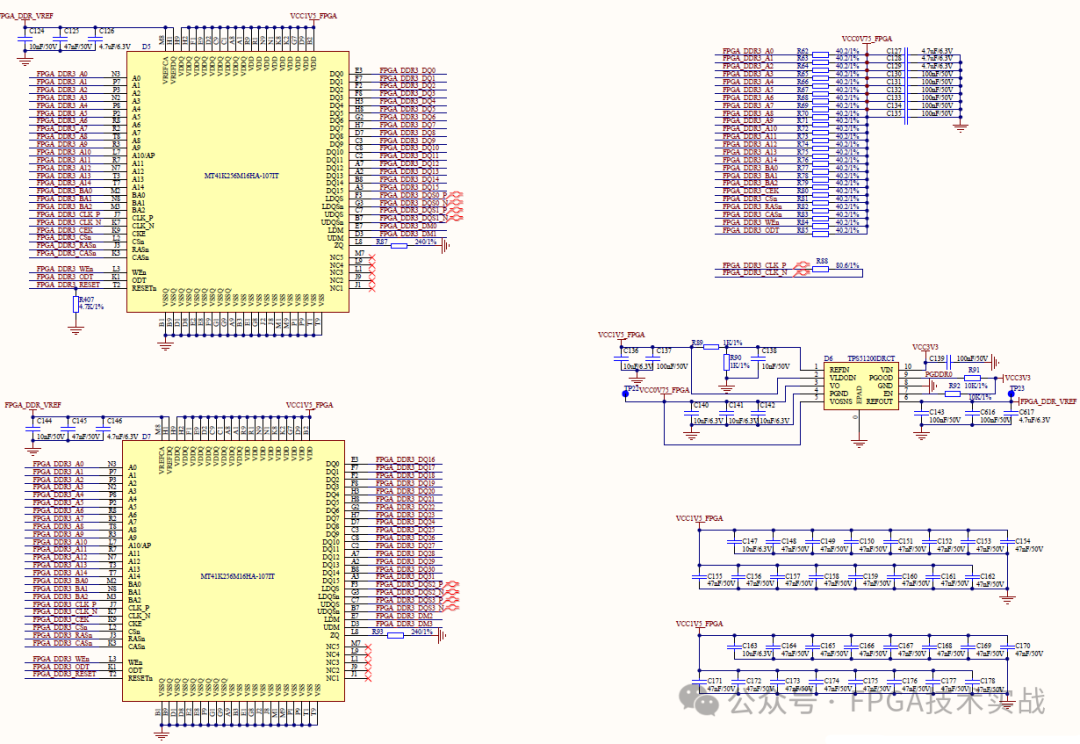

图5:DDR3 原理图设计

图5:DDR3 原理图设计

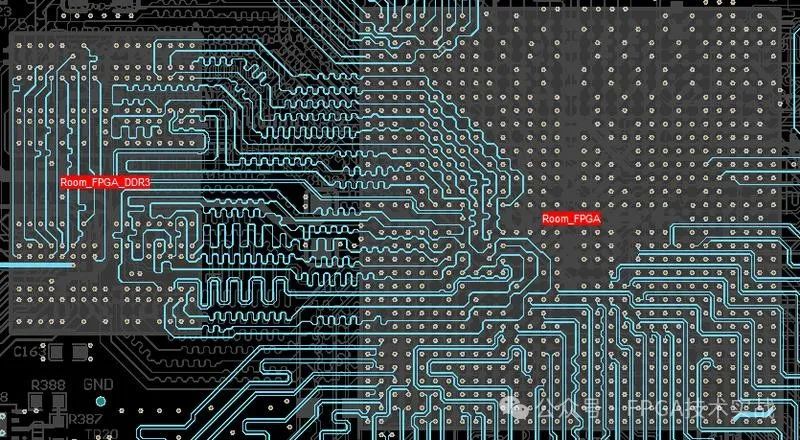

3. DDR3与K7-410T 互联PCB版图设计

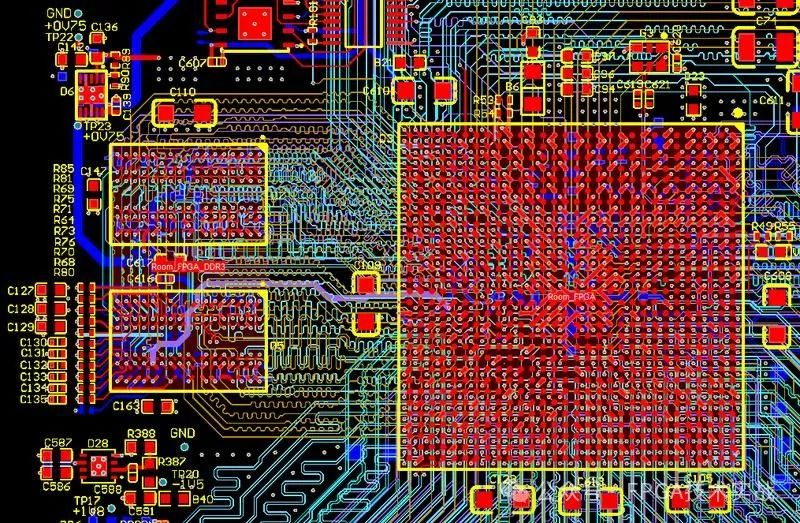

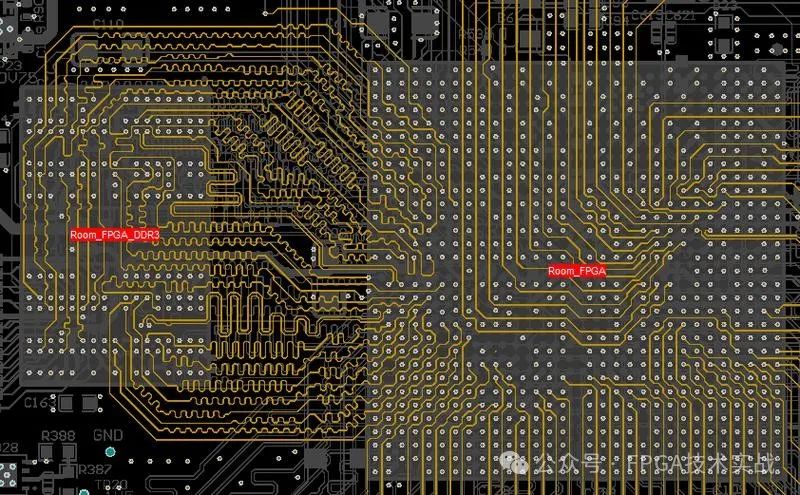

关于DDR3的PCB设计,需要遵循一些设计规则,主要包括PCB层叠设计、DDR3布局(含阻容器件)、走线阻抗约束、等长处理等。 这个项目中设计采用:XC7K410T-FFG900,FPGA外挂两片4Gbit,DDR3:MT41K256M16HA-107IT。PCB采用Fly-by布线,数据总位宽32bit,共用地址、控制、时钟。FPGA及外设DDR3走线如下图所示。

图6:整体布线

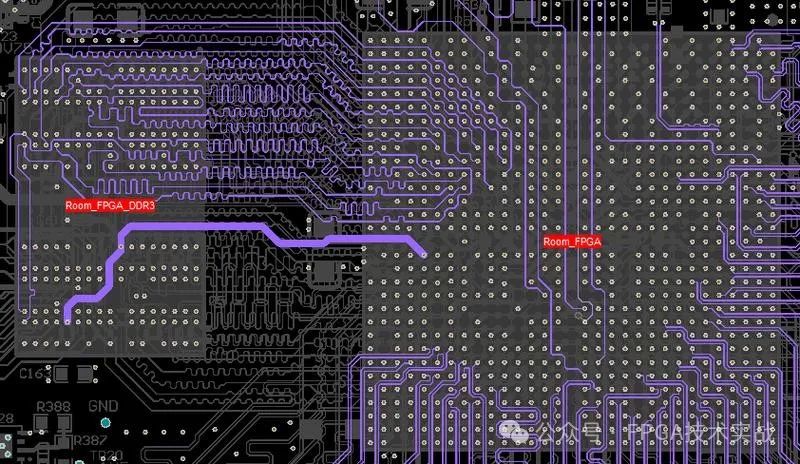

图7:数据组1

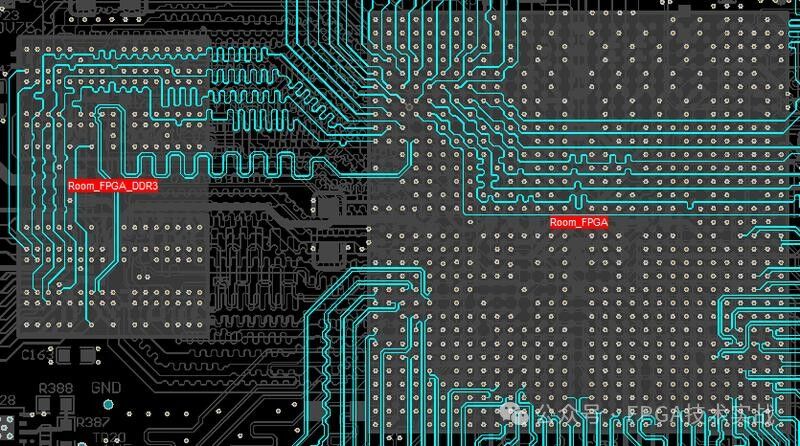

图8:数据组2

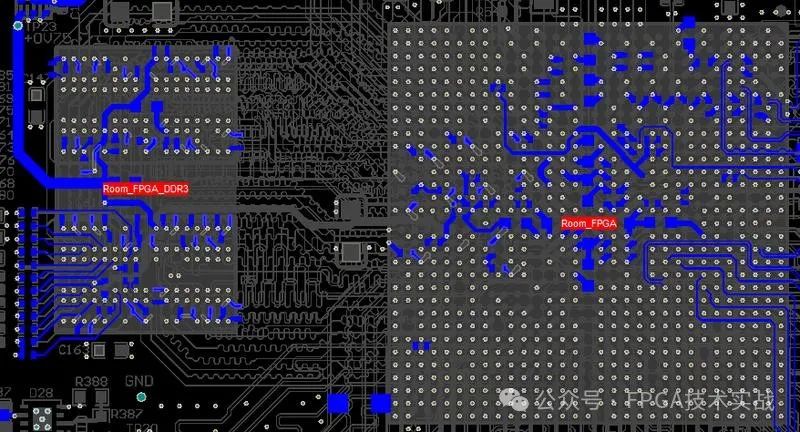

图9:地址/控制组1

图10:地址/控制组2

图11:地址/控制组3

DDR3布线相对不复杂,有几点要注意:

1)PCB布局要合理,滤波电容放置要合理,便于PCB走线;

2)PCB走线需要进行阻抗控制;

3)PCB层叠可以自己设计或者让PCB制版厂提供,根据自己的阻抗,线宽,BGA间距等要求;

4)VREF参考电压走线要≥20mil;

5)DQ/DQS/DM信号组要有完整的参考电源层,控制线、地址线、时钟线也应一样,避免跨参考分割带来信号完整性问题。

审核编辑:刘清

-

FPGA

+关注

关注

1632文章

21816浏览量

607002 -

DDR3

+关注

关注

2文章

277浏览量

42468 -

存储器

+关注

关注

38文章

7538浏览量

164540 -

Xilinx

+关注

关注

71文章

2172浏览量

122444 -

信号完整性

+关注

关注

68文章

1417浏览量

95705 -

时钟芯片

+关注

关注

2文章

254浏览量

40026 -

FPGA器件

+关注

关注

1文章

22浏览量

11658

原文标题:Xilinx Kintex-7系列XC7K410T-FFG900外设之DDR3硬件设计

文章出处:【微信号:FPGA技术实战,微信公众号:FPGA技术实战】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于FPGA的DDR3多端口读写存储管理系统设计

基于XC7K325T的四路万兆PCIe光纤收发卡

基于Xilinx Kintex-7 FPGA K7 XC7K325T PCIeX8 四路光纤卡

237-基于Xilinx Kintex-7 XC7K325T 的FMC/千兆以太网/SATA/四路光纤数据转发卡

XC7K160T-2FFG676C国宇航芯特价订货

XC7K410T-2FBG900C 原厂直供***

DDR3地址线疑问解答

请问XC7K325T-2FFG900支持PCIE PHY GEN3吗?

求XC7K325T-FFG676(Kintex-7)的文档?

Kintex-7板卡学习资料第136篇 :KC705E增强版基于FMC接口的 Kintex-7 XC7K325T PCIeX8 接口卡

XC7K325T-2FFG900I现场可编程门阵列

光纤收发卡设计资料第295篇:基于 Kintex-7 XC7K325T的半高PCIe x4双路万兆光纤收发卡

Xilinx_A7_K7_V7系列Cadence符号库

Xilinx A7 K7 V7系列Cadence符号库及PCB库免费下载

设计原理图:KC705E增强版基于FMC接口的 Kintex-7 XC7K325T PCIeX8 接口卡

XC7K410T-FFG900外设之DDR3硬件设计方案分享

XC7K410T-FFG900外设之DDR3硬件设计方案分享

评论