今天给大侠带来Intel altera opencl 入门,话不多说,上货。

概述

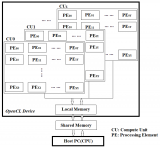

Intel altera 的 OpenCL 主要面向信号处理类应用的客户,是用C语言开发FPGA的利器,开放计算语言(OpenCL)联盟著名的公司有 FPGA巨头Intel altera、两大显卡GPU巨头AMD和英伟达、CPU巨头Intel、软件和服务器巨头IBM以及全世界最大的公司Apple(苹果)等等。不过AMD和英伟达是用GPU实现的OpenCL并行运算,Intel altera是用FPGA实现并行运算。

1. 系统要求

• Microsoft 64-bit Windows 7专业版或者更高。

• 对于Windows操作系统, 要安装微软公司的Visual Studio 2010或者2012专业版(推荐)。

或者:

• Red Hat Enterprise 64-bit Linux (RHEL) 5或者6。

• 对于Linux操作系统, 安装操作系统过程中要把C编译器包括GCC勾选上。

2.安装Altera的软件和搭建OpenCL环境(以Windows为例,Linux也类似):

•安装Quartus II 13.1 Update4(或者14.0)

•安装Altera OpenCL 13.1 Update4(AOCLSetup-13.1.4.182.exe)(或者14.0)

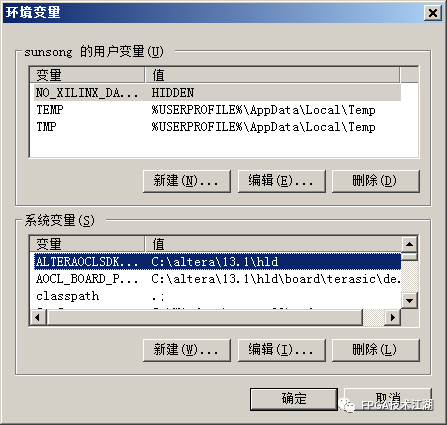

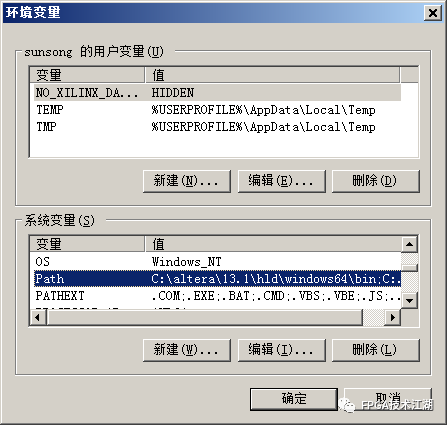

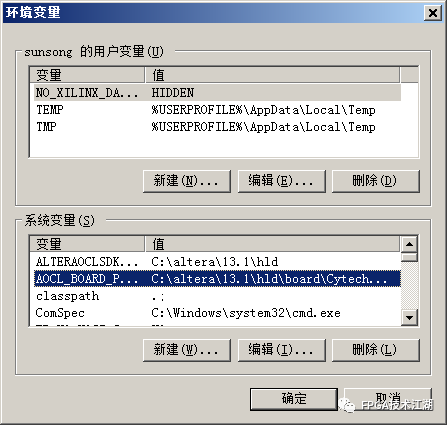

设置环境变量(基于默认的安装路径):

变量和值如下:

ALTERAOCLSDKROOT和C:altera13.1hld(或者C:altera14.0hld)

PATH和C:altera13.1hldwindows64in(或者C:altera14.0hldin;C:altera14.0hldhostwindows64in)

LM_LICENSE_FILE和c:alteralicense.dat

参考下图:

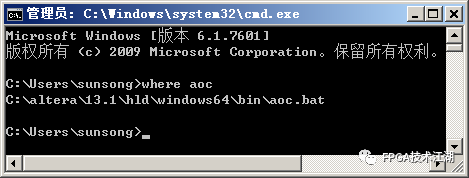

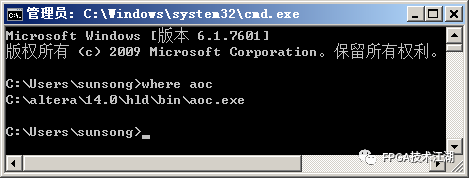

然后在命令行里面运行where aoc,测试一下软件是否安装正确以及环境变量是否设置正确,如果正确,如下图;如果不正确,修改错误再来。

或者(14.0)

3.开发板环境的安装和测试(以台湾友晶的DE5-Net开发板为例,不过没有开发板也可以,开发板不是必需的):

1)。 准备工作:下载DE5-Net开发板的全套软件安装包,http://www.terasic.com/downloads 。.. 5NET_openCL_BSP.zip 136MB,把里面的terasic文件夹解压缩到C:altera13.1hldoard下。

设置DE5-Net开发板的环境变量:

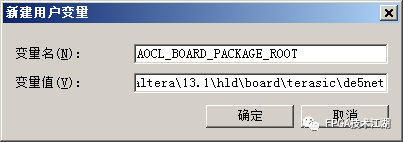

变量和值如下:

AOCL_BOARD_PACKAGE_ROOT和C:altera13.1hldoard erasicde5net

参考下图:

然后在命令行里面运行aocl install来安装开发板驱动。

关闭你的PC,安装和连接开发板硬件后,重新开机,在命令行里面运行aoc --list-boards,如果硬件安装连接成功,会显示开发板名字de5net_a7,如果开发板不存在,显示none found。

2)。 测试开发板:

在命令行里面运行 cd C:altera13.1hldoard erasic estslank,运行aocl program blank.aocx,如果开发板已经安装连接好,aocx里面的sof文件会通过PCI-E接口下载,并且会返回成功的信息,如果开发板不存在或者没有安装连接好,会自动解压缩出reprogram_temp.sof,用户可以通过USB下载电缆去下载。

备注:没有开发板的客户可以在设置环境变量后跳过后面的步骤,继续。

4.编译和测试OpenCL工程:

1)。 编译OpenCL工程:

在命令行里面运行cd C:altera13.1hldoard erasic estsoardtest进入工程文件夹,运行aoc boardtest.cl --sw-dimm-partition开始编译,编译时间大约1个小时,最终产生的boardtest.aocx里面包含了sof文件,可以给开发板编程进去。

2)。 测试OpenCL工程(通过开发板):

在命令行里面运行 cd C:altera13.1hldoard erasic estslank,运行aocl program boardtest.aocx,如果开发板已经安装连接好,aocx里面的sof文件会通过PCI-E接口下载,并且会返回成功的信息,如果开发板不存在或者没有安装连接好,会自动解压缩出reprogram_temp.sof,用户可以通过USB下载电缆去下载。

提示:没有开发板的客户可以跳过上面的步骤,直接编译下面不需要开发板的例子,有开发板的客户可以直接到第五步:

下面完全脱离真实的开发板来运行Cytech_C5SOC.zip:

设置“虚拟”板的环境变量(替换原来的环境变量):

变量和值如下:

AOCL_BOARD_PACKAGE_ROOT和 C:altera13.1hldoardCytech_C5SOC

参考下图:

解压缩Cytech_C5SOC.zip里面的内容到C:altera13.1hldoard(也可以是其它文件夹),把例子exm_opencl_hello_world_windows64.zip里面的hello_world.cl也复制到这个文件夹下,在命令行里面运行cd C:altera13.1hldoard,运行aoc hello_world.cl开始编译。----因为Cyclone V SOC的5CSXFC6容量比Stratix V的5SGSMD5小几倍,所以编译时间只有20分钟左右,最终产生的hello_world.aocx里面包含了sof文件,同时也产生了转换后的.V源码和整个编译后的Quartus II完整工程,包括大量的底层配套的各种IP源码。

再演示3个不同的例子,分别是vector_add、matrix_mult和FFT,也是完全脱离真实的开发板来运行:

不改变上面“虚拟”板的环境变量,目的是继续使用Cyclone V SOC的5CSXFC6,可以产生为这个系列优化的源码。

分别解压缩3个zip例子到C:altera13.1hldoard(也可以是其它目录),然后分别在在命令行里面:

1.运行cd C:altera13.1hldoardvector_adddevice,然后运行aoc vectorAdd.cl开始编译。

2.运行cd C:altera13.1hldoardmatrix_multdevice,然后运行aoc matrix_mult.cl开始编译。

3.运行cd C:altera13.1hldoardfft1ddevice,然后运行aoc fft1d.cl开始编译。

3个例子之间没有任何联系,可以单独运行,如果你的PC内存足够大,可以一起运行。

在产生的不同Quartus II工程中,可以找到matrix_mult.v、vectorAdd.v和fft1d.v这些转换出的源码。特别注意的是,这些最终的源码是acl_kernel_interface接口,这种接口比较简单,和FIFO差不多,只不过多了几个启动结束控制线,如start,valid等等。

备注:大家可以把这些源码复制到自己的工程中和自己写的其它逻辑模块连接起来即可。如果想产生基于Stratix V器件优化的源码,可以在环境变量的路径中把台湾友晶的DE5-Net开发板作为虚拟板(也就是恢复第三步的环境变量),然后编译cl文件即可。

5.编译Host程序:

启动Visual Studio 2012,点击“文件打开项目”,选择C:altera13.1hldoard erasic estsoardtesthostoardtest.sln(或者直接在硬盘上双击这个sln文件,VS 2012会自动完成上述步骤),然后点击“生成生成解决方案”,最后在……hostx64Release下产生了boardtest.exe,不过这个exe不能运行,因为缺少几个dll文件,把C:altera13.1hldwindows64in下的所有的6个dll文件复制过来,和这个exe放在同一个文件夹下就可以运行了。

备注:没有开发板的客户可以跳过上面这个步骤。

6.查看结果:

把第四步产生的aocx文件下载到开发板,成功后会返回信息,然后运行第五步产生的exe即可在PC屏幕上看到开发板返回的最终结果。

备注:没有开发板的客户可以跳过上面这个步骤。

没有开发板的客户只需要走1、2、4步即可。

参考资料、例子和其它:

1.参考资料:http://www.altera.com.cn/product 。.. l/opencl-index.html

网页最下面3个入门文档:

面向OpenCL的Altera SDK开始设计:aocl_getting_started.pdf

面向OpenCL的Altera SDK编程指南:aocl_programming_guide.pdf

面向OpenCL的Altera SDK优化指南:aocl_optimization_guide.pdf

其中13.1版本对应的aocl_getting_started.pdf第8页是错的,PATH应该是C:altera13.1hldwindows64in,14.0里面改正了。

2.Altera目前有13个OpenCL的例子在http://www.altera.com.cn/support/examples/opencl/opencl.html 里面,上面第4步用到的exm_opencl_hello_world_windows64.zip例子就来自于这个网页。

3.Cl文件是OpenCL的源码文件,aocx是cl文件编译后的编程文件,里面包括sof文件。PC机那边的Host软件不是必需的,做host软件仅仅是为了和开发板通信来获取开发板运行openCL的信息。没有开发板的用户只要写一个cl文件然后自己建立一个Quartus II工程就可以编译了,最后产生了转换后的.V源码和整个编译后的Quartus II完整工程,包括大量的底层配套的各种IP源码。

4.因为事先设置了环境变量的缘故,所以cl文件放到任何路径下都可以编译,编译后会在cl文件所在的文件夹里面产生完整的Quartus II整个工程,里面就有转换后的.v文件。

-

FPGA

+关注

关注

1630文章

21796浏览量

605645 -

编译器

+关注

关注

1文章

1642浏览量

49257 -

OpenCL

+关注

关注

2文章

48浏览量

33372

原文标题:Intel altera opencl 入门

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Altera正式独立运营:FPGA行业格局将迎来新变局

Altera发布全新合作伙伴加速计划

Altera推出解决方案合作伙伴加速计划

Altera宣布正式独立,结束与英特尔8年从属关系

5CGTFD7D5F27C7N Intel/Altera可编程逻辑器件(CPLD/FPGA)

英特尔拟出售Altera股权,估值达170亿美元

英特尔考虑出售Altera股权

Intel的AI Playground入门级人工智能工具亮相

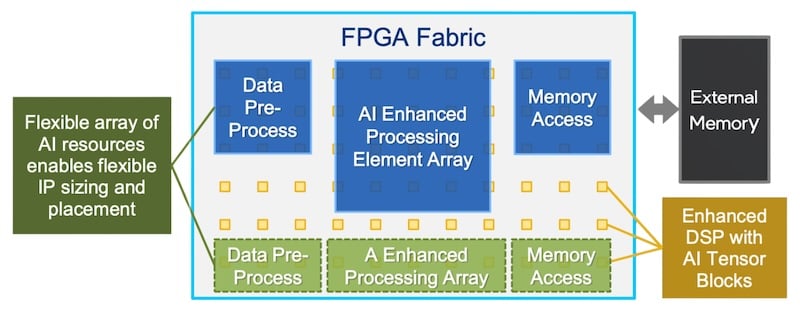

Altera将AI注入新的中端FPGA

使用Altera Interface Planner高效设计FPGA引脚布局

Intel altera opencl入门

Intel altera opencl入门

评论