概述

目前人们对于高清视频的需求日益普遍,极致的视觉体验带来的是技术上的革新,高清视频数据带宽在HD视频的基础上不断增长,以单路4Kx2K分辨率,30Hz刷新率超高清视频而言为例,单帧无压缩视频数据量约为3840x2160x24≈189.84Mbits,每秒需完成缓存的数据量约为189.84x30≈5.56Gbits,如何传输及实时处理大量的高清视频数据成为当前的一大技术需求。

对此,本作品设计了一种基于FPGA的分布式视频处理平台,能够将高清视频流通过PCIE接口以及SFP光传输接口进行从上位机到分布式视频处理平台以及分布式视频处理平台之间的高速传输。同时,本作品采用FPGA并行处理视频流,具有低时延,高算法拓展能力的特点,可以实现高带宽高清视频流的实时处理。

本项目平台设计了PCIE 2.0*8接口、2路SFP/SFP+高速光传输接口以及4路HDMI输出接口,针对高清视频数据,兼具远距离高速传输、实时处理以及本地同步显示的能力,最多能传输处理10路以上的1080p高清视频流。同时本项目平台具有高达4GB容量的高速图像缓存,以支持多路高清视频流的缓存与算法处理。在FPGA基础上,本项目平台具有的双核ARM Cortex-A9以及1GB容量的程序执行缓存,可以支持更高层算法的实现。

主要创新点

1.提出了一个针对高分辨率的视频流的高速传输与实时处理方案,包含了驱动卡与接收卡两个部分。

本作品平台为基于FPGA的分布式视频处理平台,面向高分辨率的视频流实现高带宽视频数据的高速传输与实时处理,平台系统完备,包含了视频驱动卡与接收卡两个部分。

2.软硬件全部自主设计开发,系统完善

本作品硬件软件自主设计开发。硬件部分包括43页原理图和12层高速PCB设计。软件部分包括发送高清视频流数据的上位机软件模块、本地视频数据接收与转发的视频处理平台模块、分布式视频数据接收显示的视频处理平台模块,包含PCIE数据接收模块、SFP数据转发模块、视频分割算法、DDR3高速缓存读写控制、视频数据输出模块、视频处理芯片配置模块等,有很强的原创性和先进性。

3.采用Xilinx Zynq-7000 SoC系列Zynq7045芯片,包含350K可编程逻辑资源以及Cortex-A9的双核ARM,FPGA与ARM通信接口采用AXI总线协议,稳定性好。

本设计采用的SoC芯片资源丰富,结合了FPGA与ARM的优点,从硬件设计层面提高了算法开发容量和算法处理效率,保障了高清视频数据处理的实时性,与现有技术相比,具有视频处理速度快、延时低、扩展性好等优势。

4.针对视频处理与程序执行部分分别设计了4GB与1GB的高速缓存,提升系统性能。

本系统FPGA部分采用多片DDR3高速存储颗粒应对大量的视频数据,能够保证视频传输处理的实时性和高效性。同时ARM部分也配备了多片DDR3高速存储颗粒,保障程序执行,为后续算法拓展提供支持。

5.通过PCIE*8接口从上位机获取高清视频数据,最高数据速率理论可达32Gbps

本作品可通过一路PCI Express8-lane接口,从上位机读取4k高清视频流数据,串行传输速率理论最高能达到32Gbps,最高支持2路4k@60Hz视频数据的吞吐。

6.通过2路SFP/SFP+光传输接口进行分布式视频处理平台间的高清视频数据传输,最高数据速率理论可达10Gbps/路

本作品可通过两路SFP/SFP+光传输接口,收发高清视频流数据,两路光传输接口可通过主从模式同时工作,最高支持20Gbps的数据吞吐。

7.每一块分布式视频处理平台系统同时具备4路2K视频的HDMI输出接口,能够实现视频数据传输的同时进行本地分割显示

本作品搭载4片视频处理芯片ADV7511,可支持1920*1080@60Hz的高清视频输出,因此每一块视频处理平台都拥有一路4k视频数据的分割输出功能,支持高速转发的同时,本地显示视频数据。

系统架构

1.系统方案

随着视频技术的不断革新,为了解决超高分辨率,例如2K、4K、8K、16K甚至更高分辨率的视频传输处理需求,需要硬件上能支持高清视频输入输出,高速大容量数据实时处理,软件层面上具备多种算法处理能力,各种数据通信交互,且系统要能支持性能拓展,以便使系统兼容处理更大范围的任务强度。

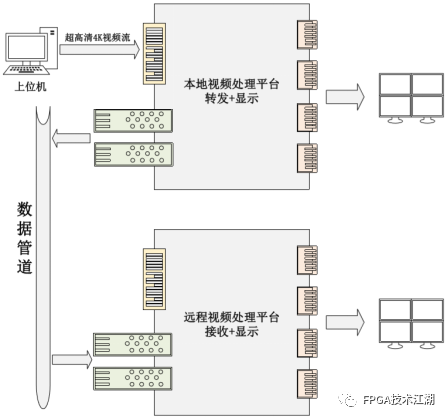

分布式视频处理平台系统主要分为三部分:发送高清视频流数据的上位机、2块及以上的基于FPGA的分布式视频处理平台、作为一组完整4K视频显示的4块2K显示屏。该系统基本结构如图2-1所示。本作品为基于FPGA的分布式视频处理平台。主要实现视频信号发生输出以及视频信号接收这两个工作模式。

图2-1分布式视频处理平台系统

2.硬件方案

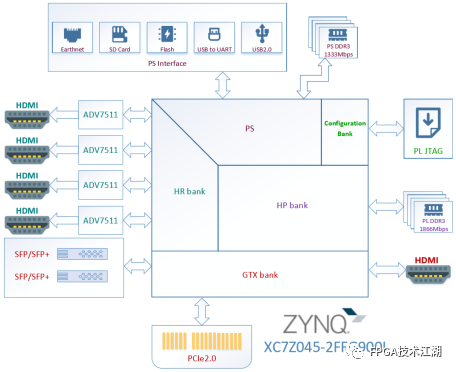

本基于FPGA的分布式视频处理平台需要将高清视频流通过PCIE接口以及SFP光传输接口进行从上位机到分布式视频处理平台以及分布式视频处理平台之间的高速传输。同时需要4路HDMI输出接口,在高速传输高清视频流的同时,通过FPGA超低时延的并行处理能力,能同步进行高清视频的分布式拼接显示。为支持以上要求,本作品搭载了Xilinx公司的Zynq-7000 SoC系列Zynq7045芯片作为核心处理器进行视频数据的传输及实时处理。

为完成对视频处理过程的控制,本系统需要利用芯片自带的双核Cortex-A9作为系统控制部分,对视频处理芯片进行寄存器配置,同时挂载大容量SDRAM,实现对大量系统数据参数的存储。

本作品需要满足大量视频数据的高速缓存要求。以最高单路4Kx2K分辨率,30Hz刷新率超高清视频而言为例,单帧无压缩视频数据量约为3840x2160x24≈189.84Mbits,每秒需完成缓存的数据量约为189.84x30≈5.56Gbits。本系统可支持PCIE 32Gbps带宽以内的超高清视频输入,则需要外接大容量高速存储设备,实现对多路视频数据的缓存。

因此,本系统采用4片共32Gbits高速DDR3存储颗粒,可满足实时处理视频流数据时对缓存空间的需求。本系统中FPGA核心处理器与存储芯片接口数据位宽共64bits,单根数据线传输速率可达1866Mbps,可满足对多路超高清视频流数据的高速缓存需求。

根据以上的分析,制定出的本作品硬件设计方案如下:

视频实时处理方案:XilinxZynq-7000 SoC系列Zynq7045芯片的FPGA部分作为视频核心处理器

视频接收方案:一路PCI Express 8-lane接口

视频发送方案:两路SFP/SFP+光传输接口

视频输出方案:四路ADV7511视频处理器,4个HDMI1.4视频输出接口

视频流缓存方案:32GBitsDDR3存储颗粒高速缓存

视频控制方案:Zynq7045芯片的ARM部分,双核Cortex-A9,2片128MB QSPI Flash和8Gbits SDRAM

系统接口设计方案:USB2.0接口、UART、1000M以太网口

图2-2平台结构框图

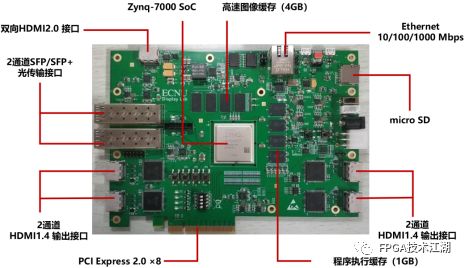

本作品实际结构图如图2-3所示。

图2-3平台实际结构图

3.软件方案

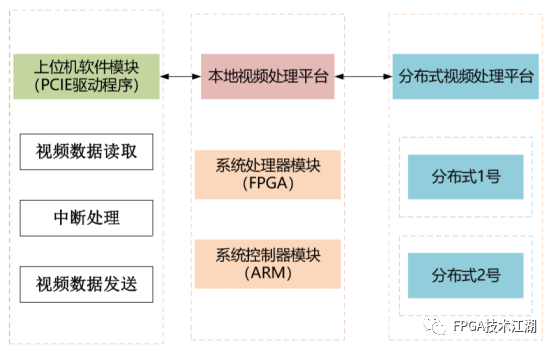

基于FPGA的分布式视频处理平台的软件整体设计如图2-4所示,其中主要包括三个模块:发送高清视频流数据的上位机软件模块、本地视频数据接收与转发的视频处理平台模块、分布式视频数据接收显示的视频处理平台模块。

图2-4系统软件整体框架图

其中上位机PCIE驱动部分,实现了指定路径下的视频流数据文件的读取与发送,根据用户给定的中断参数,实现上位机吞吐速率的控制以及数据发送操作的开关选择。

本地视频数据接收与转发的视频处理平台的软件设计较为复杂,分为PCIE数据接收模块、SFP数据转发模块、视频重组分割算法、DDR3高速缓存读写控制、视频数据输出模块、视频处理芯片寄存器配置等部分。

分布式视频数据接收显示的视频处理平台模块,分为SFP数据接收模块,视频重组算法、DDR3高速缓存读写控制、视频输出模块、视频处理芯片寄存器配置等部分。

设计演示

1.基于FPGA的分布式视频处理平台单板性能测试

以下给出电源、时钟及复位信号和DDR3等几方面测试过程及结果。

1.1电源测试

电源的稳定运行是电路系统正常工作的前提条件,因此,在对电路系统各部分进行测试前,需要先对系统电源部分测试,确保电源电压、纹波等参数能够满足要求。本系统的电源使用了TI公司的TPS53355、TPS62130和TPS51200。

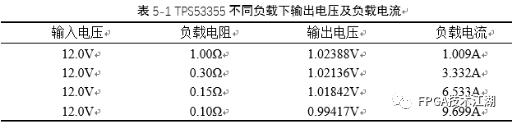

对TPS53355电源评估电路进行测试,可得到如表5-1所示的测量结果。

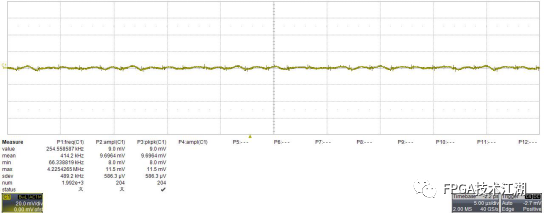

通过对电源输出电压进行分析,可见在较低负载和较高负载下都能够满足FPGA核心处理器0.97V至1.03V的电压范围要求。通过示波器可以测得在不同负载情况下的纹波,其中负载电流为9.699A时的纹波测试结果如图5-1所示。

图5-1 TPS53355负载电流为9.699A时的纹波

此时,可观测到电源的开关频率约为500KHz,电源纹波幅度的最小值为8.0mV,最大值为11.5mV,满足电路系统设计要求。

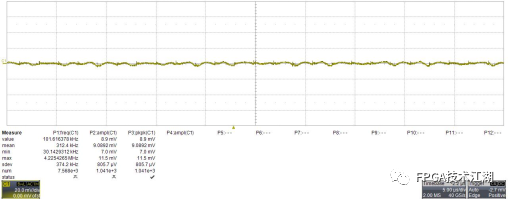

通过对实际电路中1.0V电源进行测试,纹波如图5-2所示,同样满足设计要求。

图5-2 TPS53355在系统工作时的纹波波形

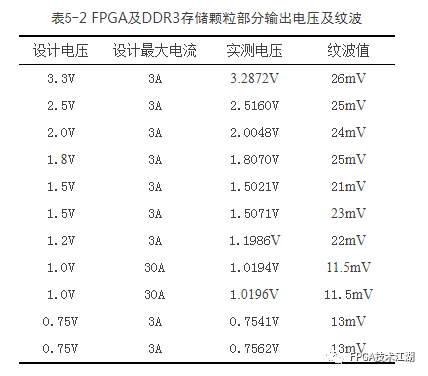

分别对本系统中其他部分电源电路进行测量,其中FPGA核心处理器及DDR3存储颗粒部分各电源输出电压及纹波如表5-2所示,都能够满足设计要求。

1.2时钟及复位信号测试

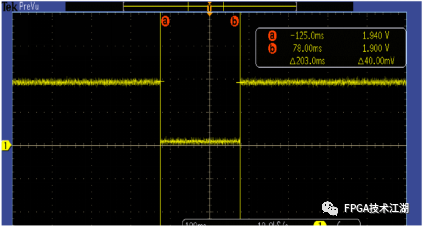

系统的复位信号是测试部分首先考虑的对象。在本系统中,我们对于ZYNQ中ARM部分的复位芯片MAX16025输出的全局复位信号进行测试。如图5-3所示,当按键被按下时,全局复位信号被置为低电平,且低电平保持203.0ms;当按键被松开时,全局复位信号恢复成高电平。

图5-3系统全局复位信号测试 其次测试系统的时钟信号。在整个系统中,以下三个时钟较为关键。

ZYNQ处理器FPGA部分200MHz差分时钟(逻辑触发时钟);

ZYNQ处理器GTX部分SFP光传输接口IP核的156.25MHz差分时钟;

ZYNQ 处理器 ARM 部分 33.33333MHz 单端时钟。

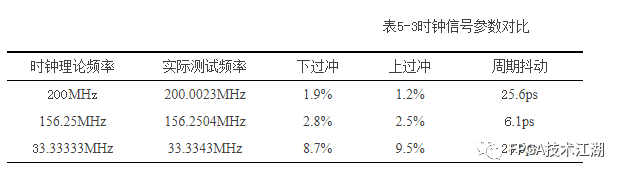

其中,差分时钟需要利用差分探头进行测试。 在测试时钟时,示波器的采样率被设置为1GHz,上述三个时钟的时钟波形如图5-4所示。

图5-4系统时钟信号测试 三个关键时钟信号测量所得参数如表5-3所示。

由上表可见,相对于33.33333MHz的单端时钟,200MHz和156.25MHz的差分时钟利用了抑制相互串扰的性质,时间精度较高,并且在信号的上过冲、下过冲和周期抖动指标上具有优势。

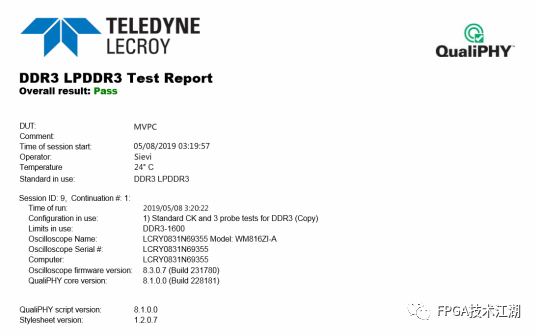

1.3DDR3眼图测试

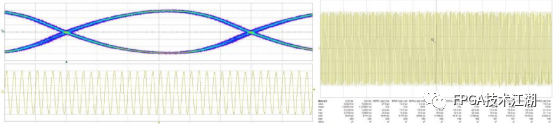

这部分介绍系统ZYNQ中的FPGA部分连接的DDR3的信号完整性测试过程与结果。DDR3速率为1600Mbps,通过编写测试程序的方式来实现持续对DDR3进行读写,以进行测试。示波器测试800MHz差分时钟眼图,如图5-5所示

图5-5DDR3差分时钟眼图测试

由图5-5可知示波器读出该信号眼高为1.1366V,眼宽为578ps,眼交叉比为50.37%,差分时钟设计指标通过了LeCroy示波器的QualiPHY对于1600Mbps的DDR3的标准测试,因此眼图各指标符合设计要求。

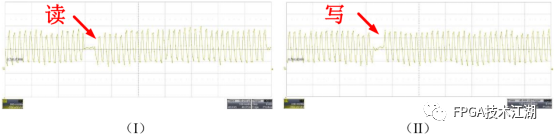

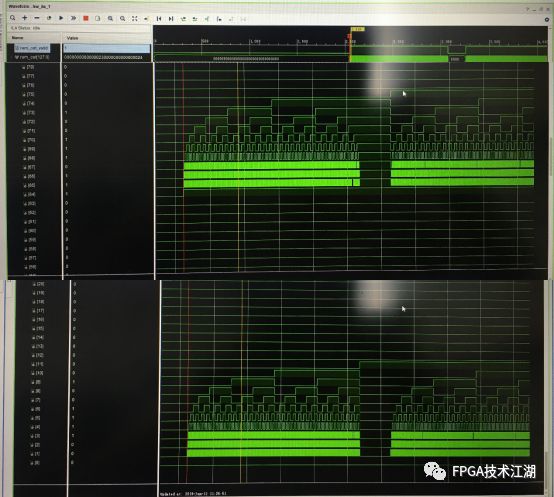

进一步利用示波器观察DDR3时序:DQS信号如图5-6所示:当DDR3进入读状态时,DQS前导码先产生负脉冲。相反,当DDR3进入写状态时,DQS前导码先产生正脉冲。

图5-6DDR3 DQS信号测试

示波器自带的QualiPHY功能能够对DDR3各项性能进行测试,测试完成后将会生成一份测试报告,如图5-7所示。在测试报告中将详细列出各项参数的测量值和理论值,并对是否达标进行分析。

图5-7差分时钟线测试报告

1.4ADV7511视频处理器验证

为验证ADV7511视频处理器芯片部分的电路设计,编写测试代码以完成验证。在进行该部分的测试过程中,我们基于ZYNQARM部分编写IIC配置接口,配置ADV7511寄存器,使能芯片,同时,FPGA部分按照时序要求编写测试图像,并输出到ADV7511,最终板级输出效果如图5-8所示。

图5-8ADV7511测试图像图

由上图可知,ADV7511寄存器配置正确,芯片正常使能,FPGA时序发生正确,能够正常显示图像。

1.5 PCIE系统接口验证

图5-9上位机数据发送窗口为验证PCIE系统接口的功能,我们通过上位机向系统的PCIE接口发送数据文件,如图5-9所示。

通过Vivado的ILA工具采得数据传输波形,如图5-10所示。从图5-10的波形中,对比上位机发送的文件数据,可知PCIE读取的数据文件正确无误。

图5-10系统PCIE接口数据文件抓取波形图

2.系统联调

整体系统联调效果图如图5-11所示:

图5-11系统整体效果图

通过以上的效果可以看出,本作品可以实现本地视频处理平台PCIE接口从上位机接收超高清4K视频流的数据,并经过SFP/SFP+高速光传输接口高速传送至分布式视频处理平台,同时本地与分布式视频处理平台兼有4K视频分割显示的实时处理能力。

审核编辑:刘清

-

FPGA

+关注

关注

1629文章

21729浏览量

602964 -

DDR3

+关注

关注

2文章

276浏览量

42240 -

PCB设计

+关注

关注

394文章

4683浏览量

85539 -

CORTEX-A9

+关注

关注

0文章

38浏览量

35231 -

PCIe接口

+关注

关注

0文章

120浏览量

9701

原文标题:基于FPGA的分布式视频处理平台

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何利用FPGA设计无线分布式采集系统?

分布式系统的优势是什么?

分布式KVM坐席拼控系统解决方案

如何高效完成HarmonyOS分布式应用测试?

基于混沌置乱预处理的分布式视频编码

应用分布式算法在FPGA平台实现FIR低通滤波器

FIR数字滤波器分布式算法的原理及FPGA实现

WMSN的分布式视频编码技术研究

基于FPGA的分布式视频处理平台设计方案

基于FPGA的分布式视频处理平台设计方案

评论