09

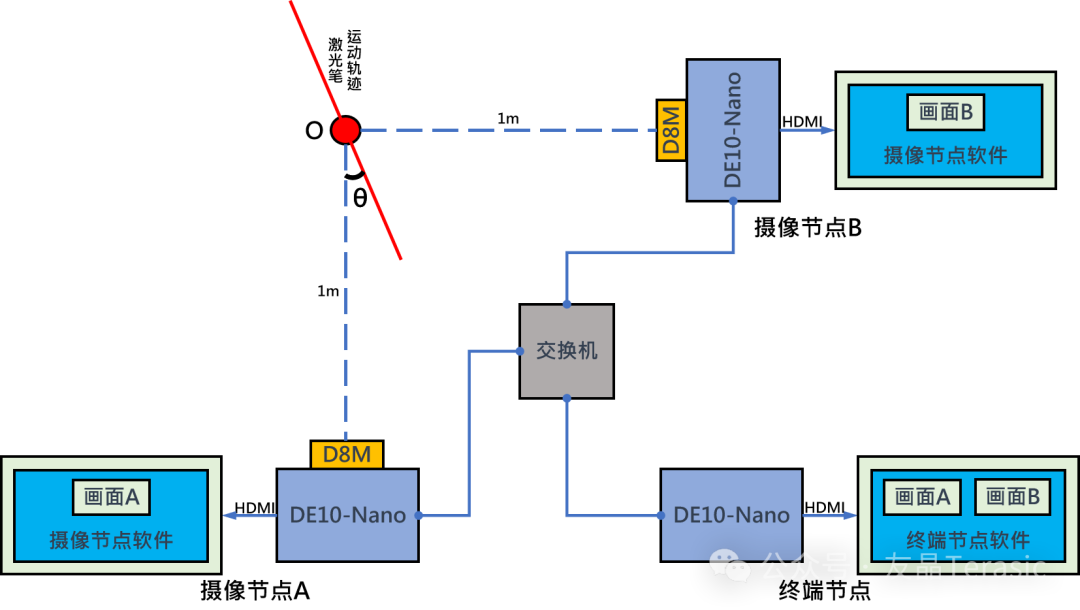

前面介绍了系统的硬件框图如下:

硬件基本分为三块,两个摄像节点,一个终端节点。

1. 摄像节点硬件

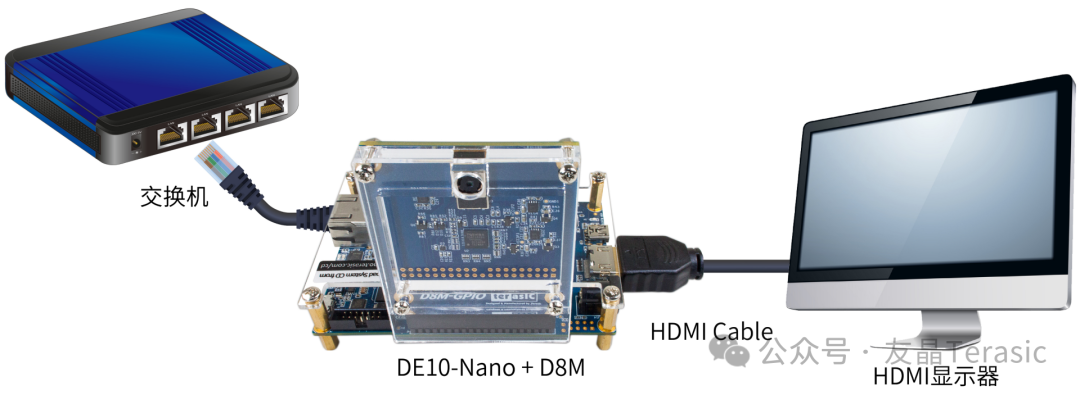

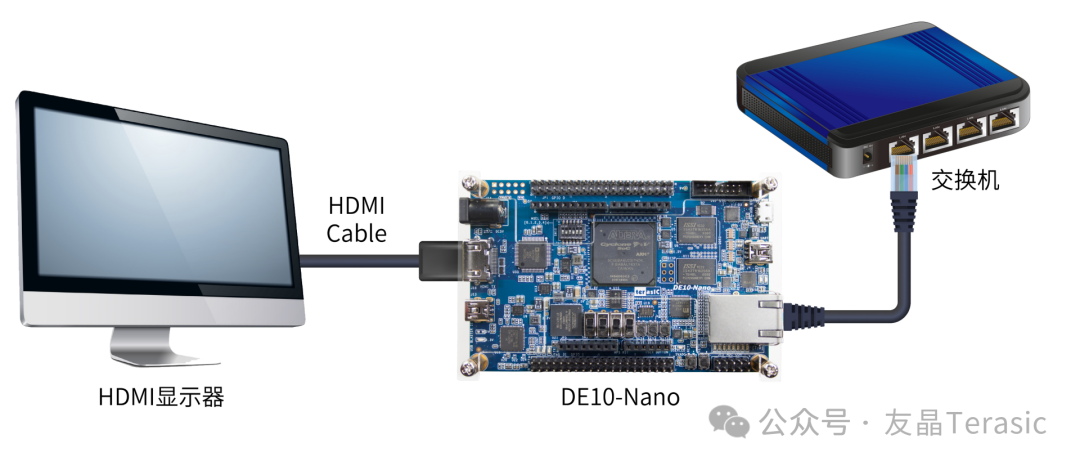

摄像节点由一个DE10-Nano开发板和一个D8M摄像头实现,DE10-Nano开发板的HDMI接口外接HDMI显示器来显示拍摄到的视频。

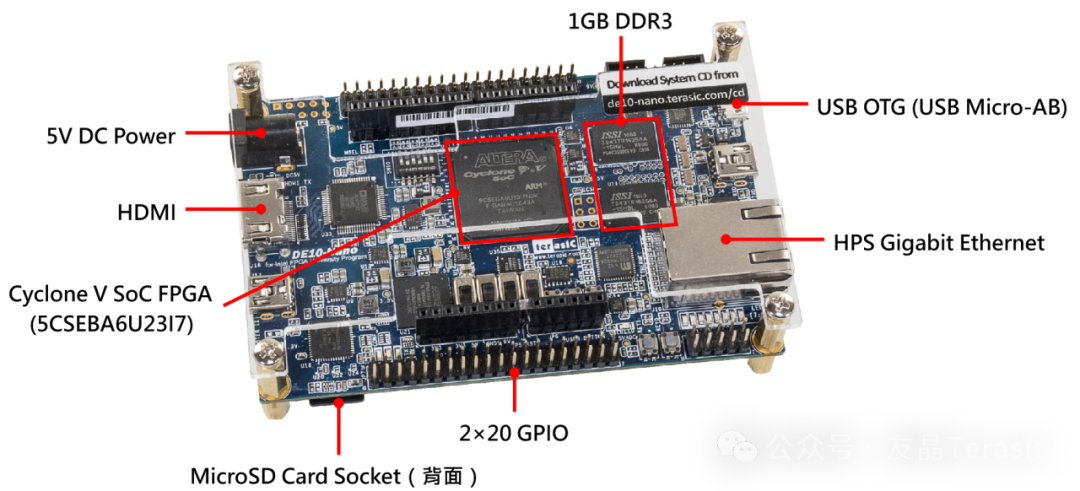

DE10-Nano开发板硬件

DE10-Nano开发板基于Cyclone V SoC FPGA,拥有110K逻辑单元和ARM Cortex A9双核处理器,其FPGA资源可用于算法加速。

FPGA端包含HDMI接口,可连接HDMI显示器显示视频;2×20的GPIO接口,可连接GPIO接口的子卡。

HPS端包含1GB容量的DDR3内存;USB OTG接口,支持USB摄像头、鼠标、键盘等硬件;千兆以太网口,可实现网络传输。

MicroSD卡插槽,可以插入烧写了镜像的SD卡,运行Linux系统。

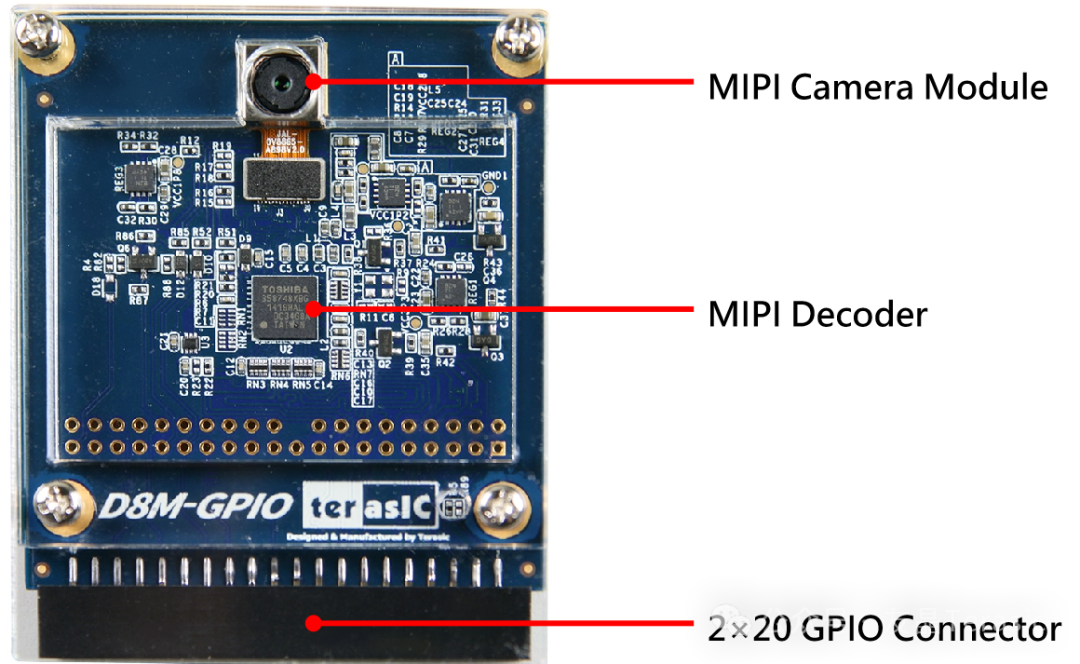

D8M摄像模块硬件

D8M-GPIO是 一个2×20 pin GPIO接口的八百万像素摄像头子卡,包含MIPI Camera Module和MIPI Decoder。(Mobile Industry Processor Interface简称MIPI。)

MIPI Camera module拍摄视频后输出MIPI视频信号数据包,通过MIPI decoder转换成拜耳阵列(bayer pattern,10-bits parallel),最终由2x20 pin GPIO接口输出。

2. 终端节点硬件

终端节点由一个DE10-Nano开发板实现,并外接HDMI显示器来显示摄像节点传输过来的视频以及测量结果。并用声光提示模块发出声光提示信息。

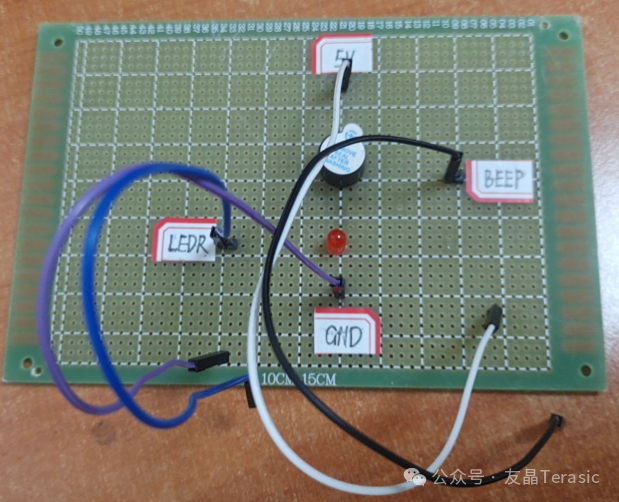

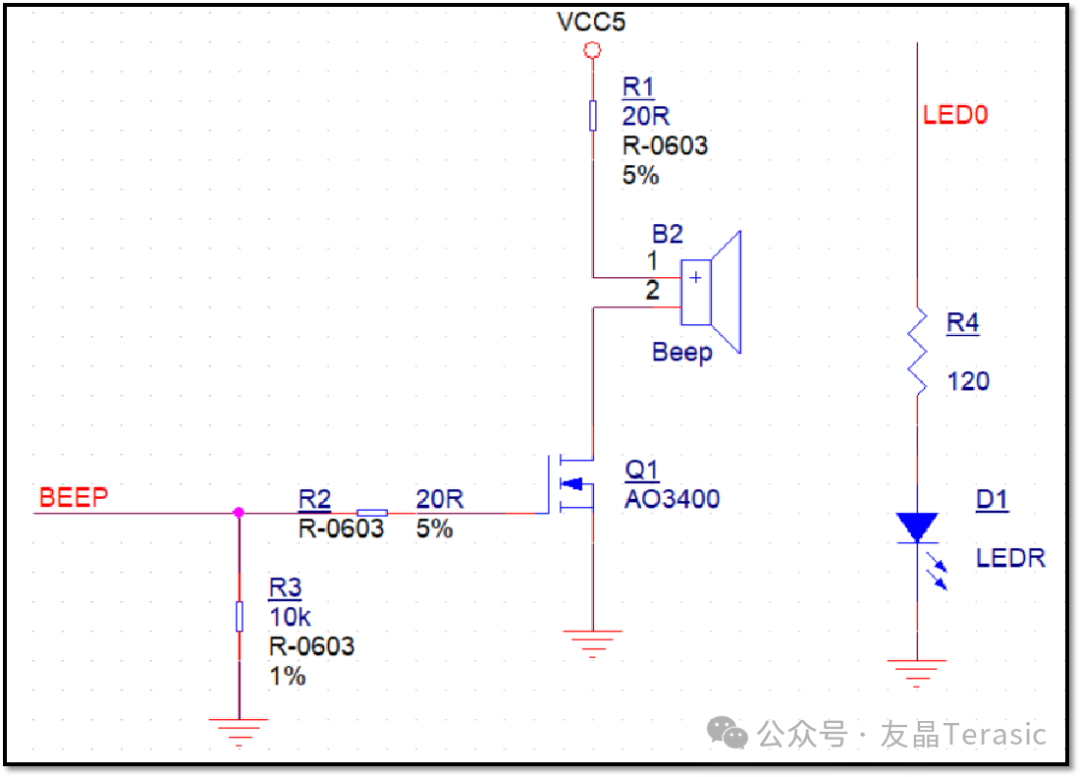

声光提示电路

实现声光提示功能的电路由一个蜂鸣器和一个红色LED组成,这是一个简单的蜂鸣器驱动模块。

10

摄像节点程序设计

1. 摄像节点整体介绍

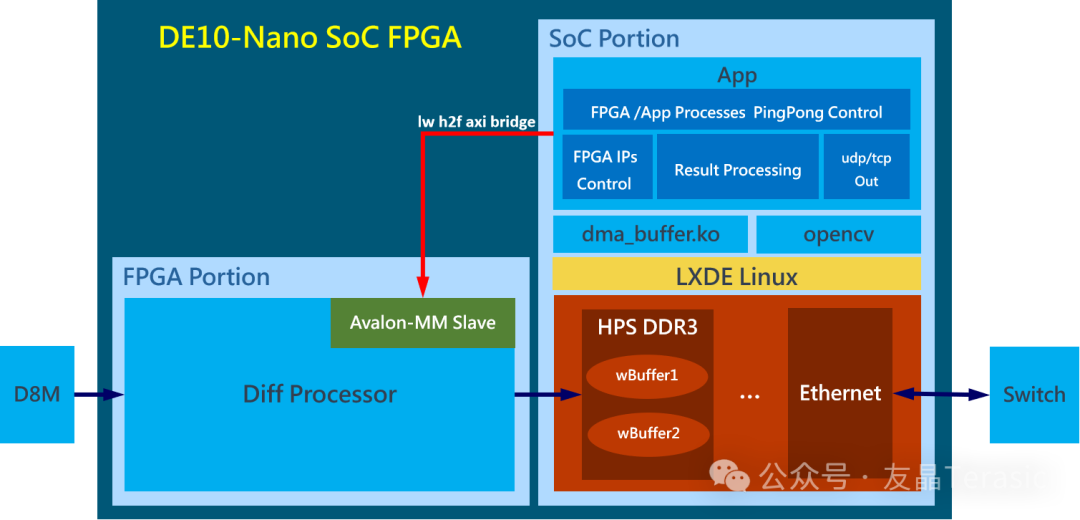

摄像节点程序包含FPGA和SoC两部分,FPGA中实现了一个Diff Processor,Diff Processor获取D8M摄像头拍摄到的视频流数据并进行处理,然后将处理的结果写入HPS DDR3内存中。

SoC中的应用程序初始化Diff Processor中的IP并配置帧间差分法的阈值,通过乒乓控制决定将Diff Processor的结果写入wBuffer1或wBuffer2,然后读取wBuffer得到Diff Processor处理的结果再进行进一步的处理,最后将图像结果通过UDP发送到终端节点,数据结果通过TCP发送到终端节点。

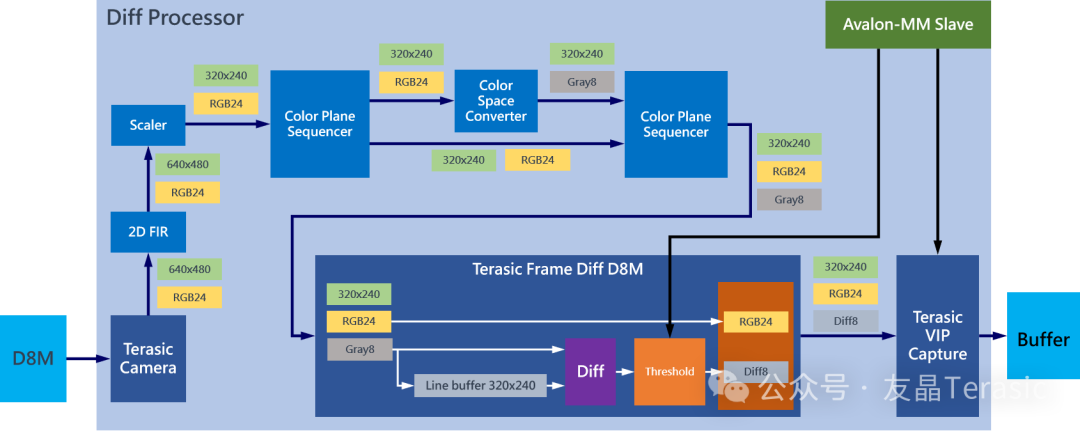

2. FPGA端的Diff Processor设计

这是FPGA中Diff Processer的框图,Diff Processer系统是使用Platform Designer工具搭建的,其中2D FIR(2D滤波)、Scaler(缩放)、Color Plane Sequencer(色彩平面定序器)、Color Space Converter(色彩空间转换) IP为Quartus Prime软件中已有的视频处理IP;Terasic Camera、Terasic Frame Diff D8M、Terasic VIP Capture IP为友晶自定义IP。

Diff Processer的处理过程为:Terasic Camera将D8M摄像头获取的拜耳阵列转换为RGB24图像,大小为640×480,然后使用2D FIR进行滤波处理,再使用Scaler将图像缩放为320×240,通过Color Plane Sequencer将图像复制为两份,一份保持不变,一份通过Color Space Converter将图像转换为灰度图,再次通过Color Plane Sequencer将原图像与灰度图合并,得到320×240的RGB+Gray的4通道图像。Terasic Frame Diff D8M处理图像的过程为,Line Buffer缓存上一帧灰度图,与当前帧的灰度图做差分并判断是否大于阈值,然后将帧间差分结果图像与原图像合并得到结果帧。最后用Terasic VIP Capture 将结果帧写到Buffer。

Terasic Camera自定义IP用于实现将拜尔阵列转换为RGB图像,并将frame输出为Avalon-ST(Avalon-Streaming,Avalon流)。

- Terasic Frame Diff D8M自定义IP采用Streaming协议处理1路输入,使用Line buffer缓存,缓存帧与当前帧进行差分,还包含1路结果视频流输出;并且实现了控制寄存器,可以设置帧间差分法阈值变化。为了兼顾视频流和数据集的采集,这里将原图像与差分结果组合成4通道的图像进行输出。

Terasic VIP Capture自定义IP用于实现接收Streaming协议视频流和动态切换指定目标buffer地址。

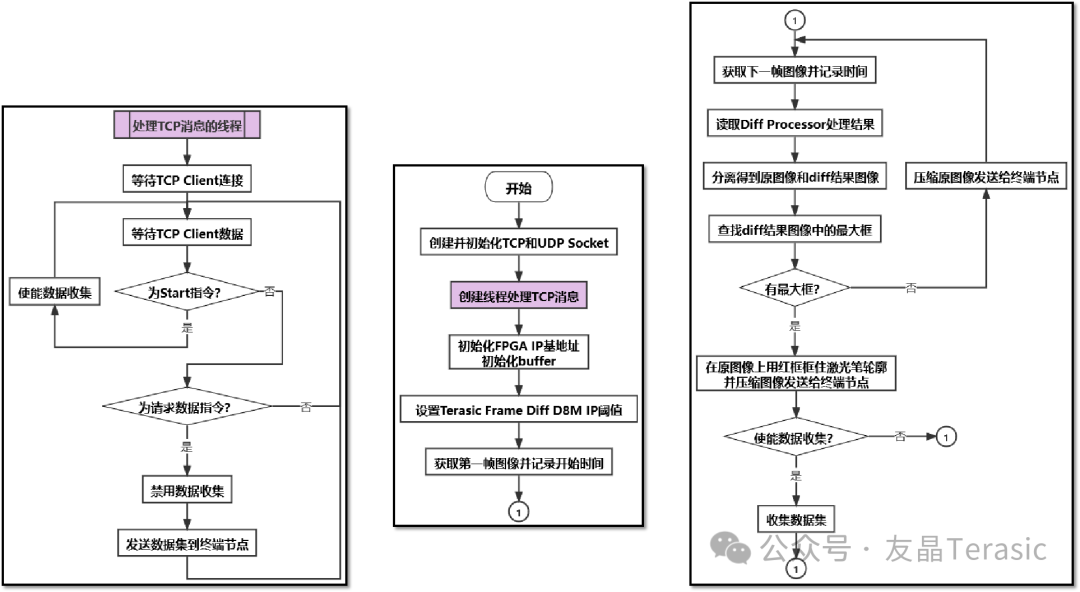

3. HPS端的C程序设计

首先创建并初始化TCP和UDP Socket,TCP用来传输数据,UDP用来传输图像,接着创建线程处理TCP消息,在这个线程中,摄像节点等待终端节点发送的start指令和请求数据指令,如果是start指令,就开始收集数据,如果是请求数据指令,则停止数据收集并发送数据集到终端节点,然后初始化FPGA IP基地址和buffer,并设置帧间差分法的阈值,接着获取第一帧图像并记录时刻t,再获取下一帧并记录时刻t,然后diff processor会对两帧图像进行处理,读取处理结果并分离得到原图像和帧间差分结果图像,在帧间差分结果图像中查找最大框,如果有最大框就用红框框住激光笔轮廓并压缩图像发送到终端节点,如果没有最大框就压缩原图像发送到终端节点,最后根据终端节点发送的指令来判断是否收集数据集。

11

终端节点程序设计

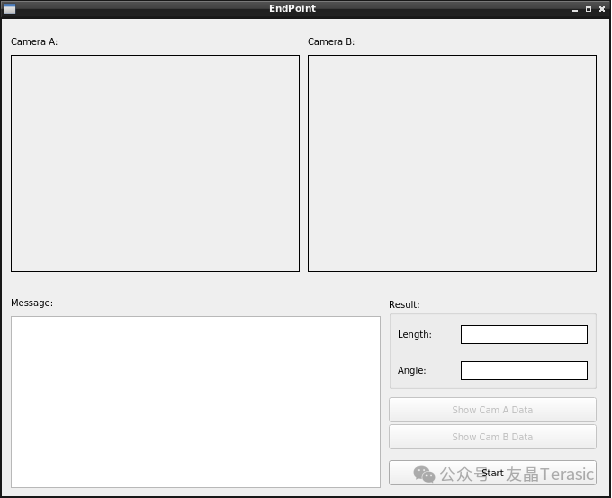

初始化用户界要有摄像节点A和B的画面显示、消息显示框以及测量结果的显示:

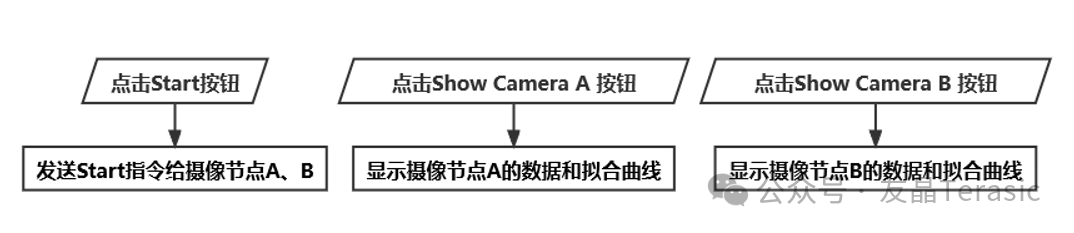

此外还有三个按钮,Start按钮用来发送指令给摄像节点A和B,Show Camera A按钮用来显示摄像节点A的数据和拟合曲线,Show Camera B按钮用来显示摄像节点B的数据和拟合曲线。

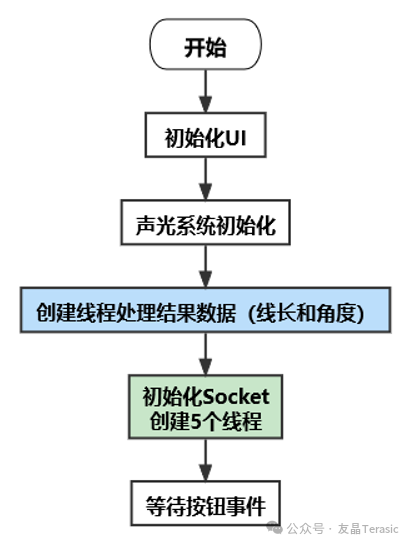

然后是声光系统初始化,再接着创建一个线程用于处理结果数据,初始化Socke并创建5个线程,最后等待按钮事件。

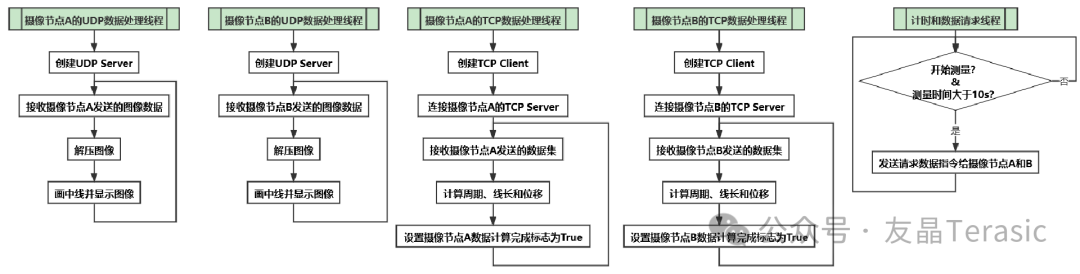

下面我们具体介绍创建的5个线程,分别是摄像节点A、B的UDP数据处理线程和TCP数据处理线程,还有一个计时和数据请求线程。

其中,UDP数据处理线程首先创建UDP Server,然后等待接收摄像节点A、B发送的图像数据,然后解压图像并显示。

TCP数据处理线程首先创建TCP Client,然后连接摄像节点A、B的TCP Server,之后等待接收摄像节点发送的数据集,计算得到周期、线长和位移,计算完成后设置标志为True。

计时和数据请求线程主要是判断是否开始测量以及测量时间是否大于10s,如果测量时间达到10s,就发送请求数据指令给摄像节点。

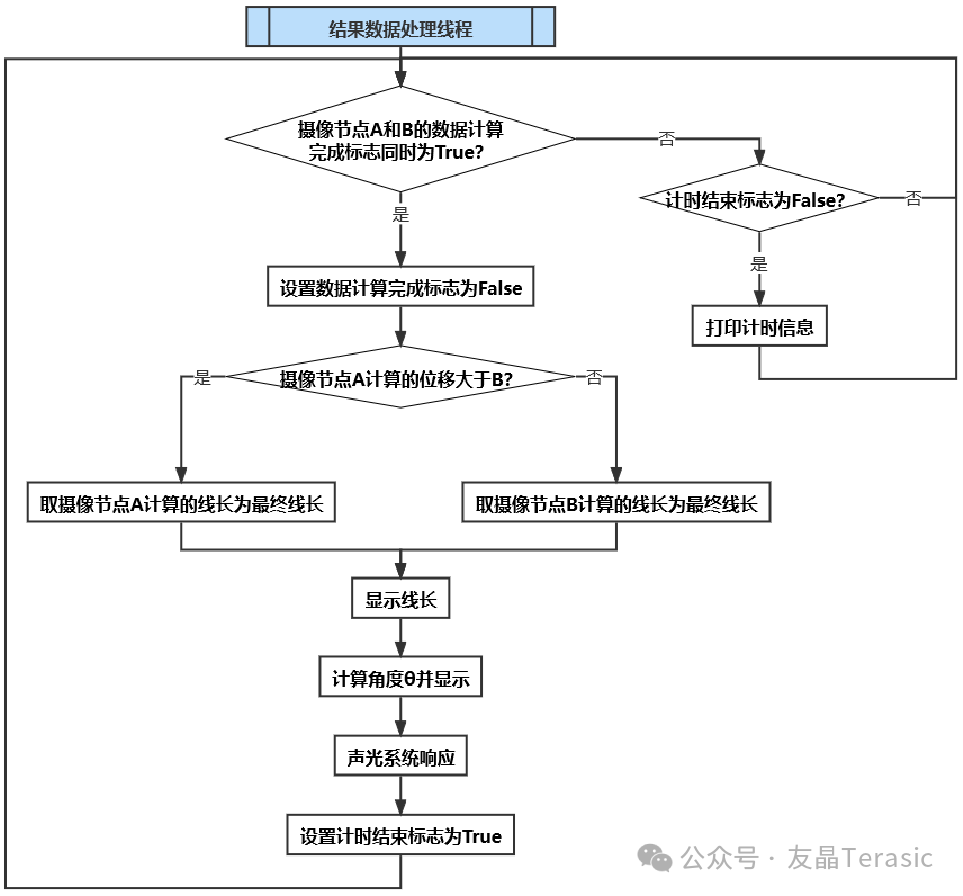

最后是结果数据处理线程,先判断摄像节点A、B是否计算完成,如果没有计算完,则先判断是否还在计时,如果是则打印计时消息并继续等待摄像节点计算完成。

当摄像节点A和B都计算完成后,首先将标志位清零,然后判断摄像节点A的位移和B的位移哪一个更大,选择位移较大的节点计算的线长作为最终线长并显示,接着计算角度θ并显示,然后声光提示,最后停止计时。

12

拟合cos函数程序设计

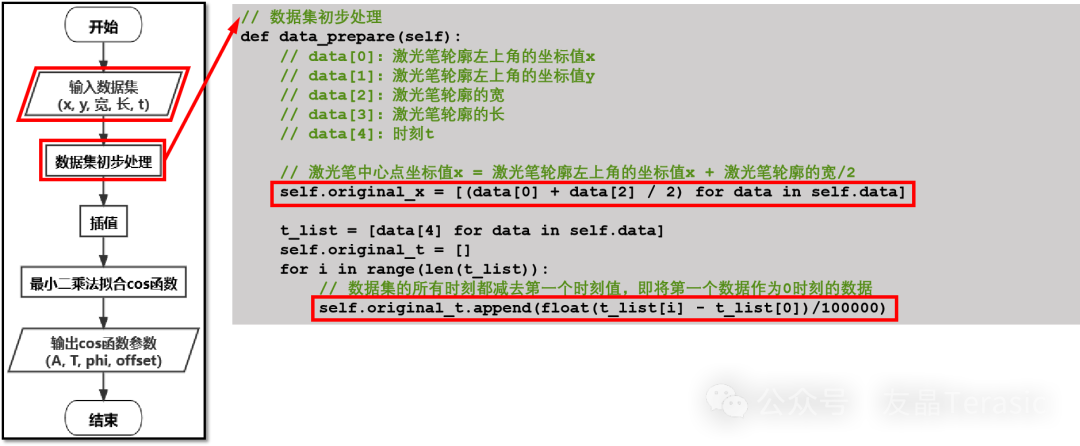

当终端节点收到摄像节点采集到的数据集(包含激光笔轮廓左上角的坐标x和y、轮廓的宽和长以及时刻t)时会对数据集进行初步的处理。

首先是将激光笔左上角的坐标值x+激光笔轮廓的宽/2,得到激光笔中心点的坐标值x。然后再将数据集的所有时刻都减去第一个时刻值,也就是将第一个数据作为0时刻的数据。

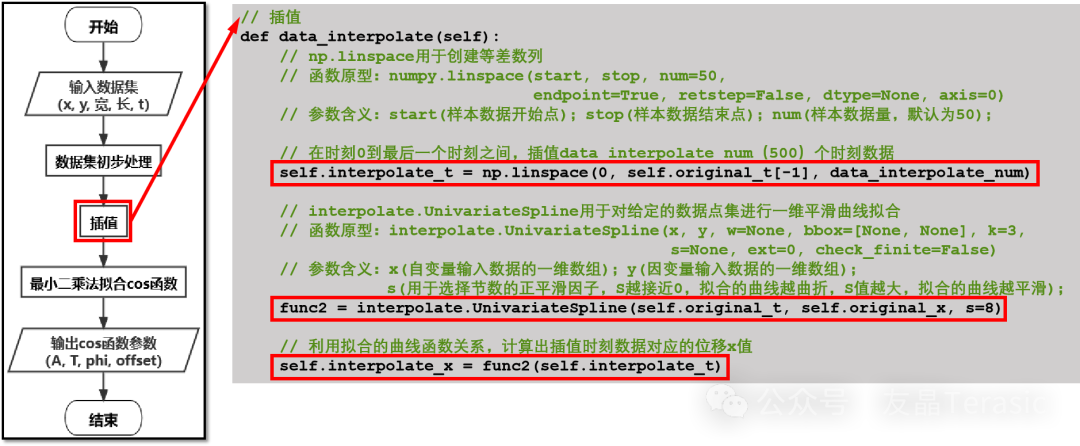

接着通过插值来增加数据量。

先是使用Linear space函数创建时刻t的等差数列,函数的第一个参数为样本数据开始点,也就是时刻0,第二个参数为样本数据的结束点,也就是最后一个时刻值,第三个参数为样本数据量,这里我们插值500个时刻数据。

接下来使用Univariate Spline函数对已有的数据集进行平滑曲线拟合,得到函数关系式function2,然后利用拟合的函数关系,计算出插值时刻对应的位移x。

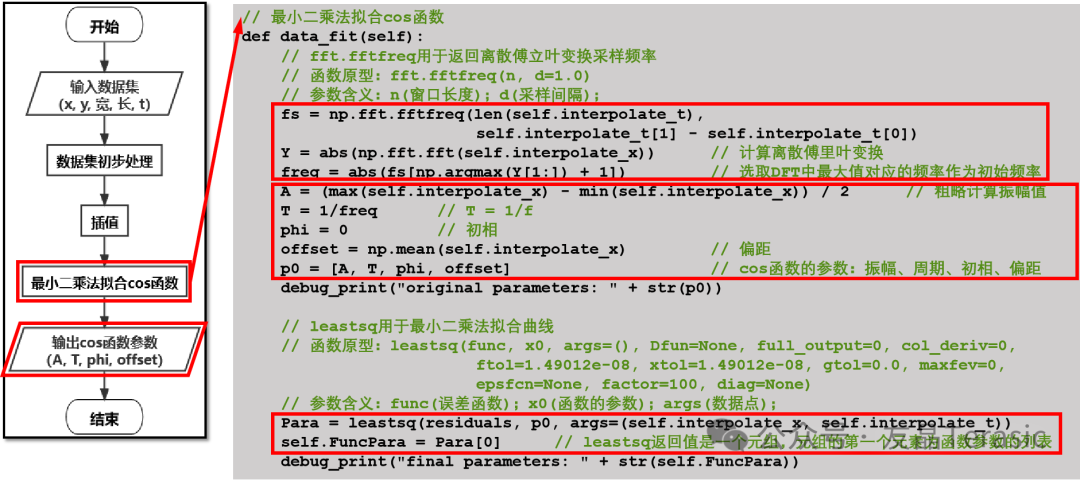

最后使用最小二乘法拟合cos函数。

第一步是使用fft frequency函数得到傅里叶变换的采样频率,然后使用fft函数计算离散傅里叶变化。由于离散傅里叶变化在一段有限长的离散信号中,找出它含有的各个频率的正弦波分量,因此我们可以选取离散傅里叶变化中最大值对应的频率作为cos函数的初始频率,

接着用最大位移-最小位移,/2,得到初始振幅值,周期=1/频率,初相设为0,计算所有位移的平均值作为偏距。

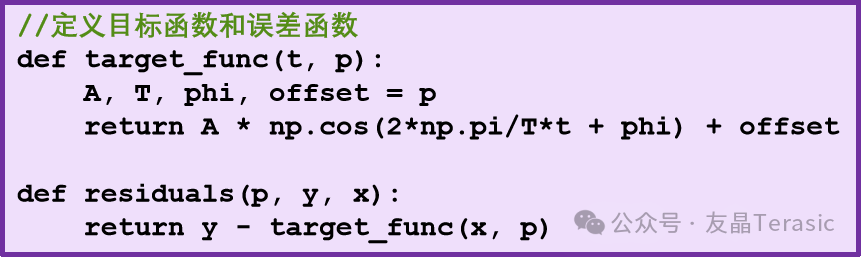

然后使用least square函数拟合cos函数,第一个参数为误差函数,首先定义目标函数为Acos(2pi/T*t+phi)+偏距,那么误差函数为:y-目标函数值。第二个参数为函数的参数p0。第三个参数为数据集,least square函数的返回值parameter是一个元组,元组的第一个元素为cos函数的参数列表,最后输出cos函数的参数。

审核编辑:黄飞

-

HDMI

+关注

关注

32文章

1694浏览量

151864 -

电路设计

+关注

关注

6673文章

2451浏览量

204167 -

互联网

+关注

关注

54文章

11148浏览量

103236 -

摄像头

+关注

关注

59文章

4836浏览量

95600 -

摄像系统

+关注

关注

0文章

19浏览量

12087

原文标题:2021年全国大学生电子设计竞赛D题——基于互联网的摄像测量系统(二)

文章出处:【微信号:友晶FPGA,微信公众号:友晶FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于互联网的摄像测量系统(二)

基于互联网的摄像测量系统(二)

评论