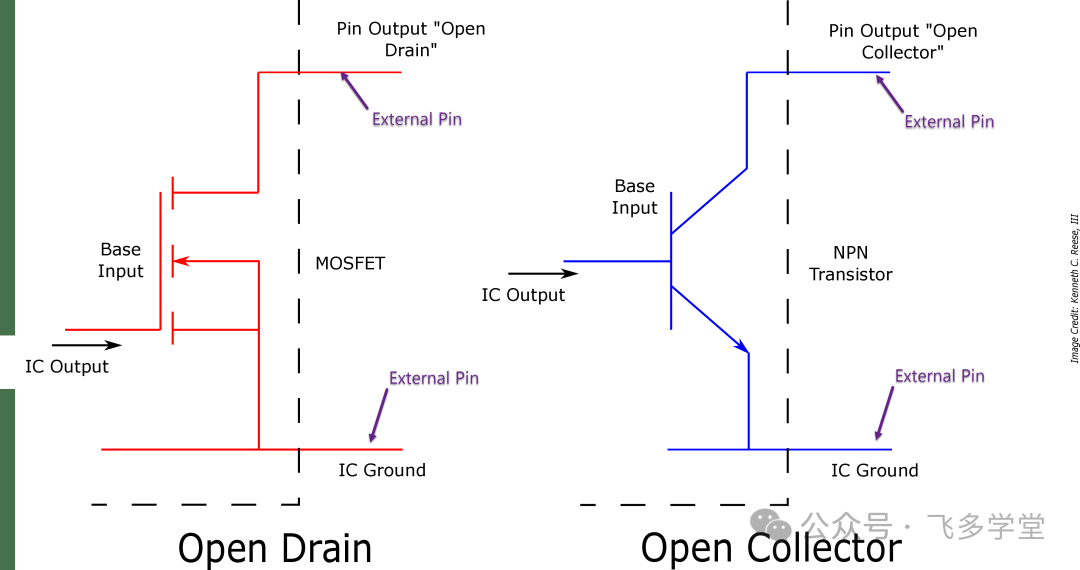

开漏(open-drain)或开集电极(open-collector)输出引脚由单个晶体管驱动,将引脚拉到只有一个电压(通常是接地)。当输出设备关闭时,引脚被悬空(开启,或高阻态)。

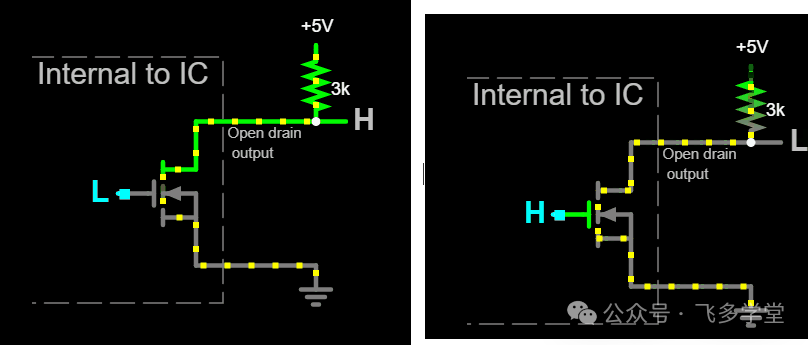

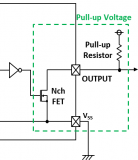

一个常见的例子是n沟道晶体管,当晶体管导通时,将信号拉向地,或者当晶体管关断时,将信号保持开路。

开漏指的是在场效应晶体管技术中实现的这种电路,因为晶体管的漏极端口连接到输出端;开集指的是双极晶体管的集电极连接到输出。

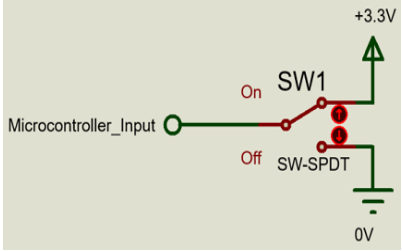

当晶体管关断时,信号可以被另一个设备驱动,或者可以通过电阻上拉或下拉。电阻可防止未定义的漂浮状态(高阻态)。

什么是开集输出

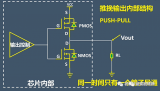

Open collector(开集)是一种电路输出结构,它允许多个输出设备共享一个电路线。在Open collector电路中,输出器件可以将输出线拉低(接地),但不能将其拉高。因此,当输出器件拉低时,输出线将被拉低,而当输出器件不拉低时,输出线将由上拉电阻上拉到高电平。这种结构通常用于数字电路和总线系统中。

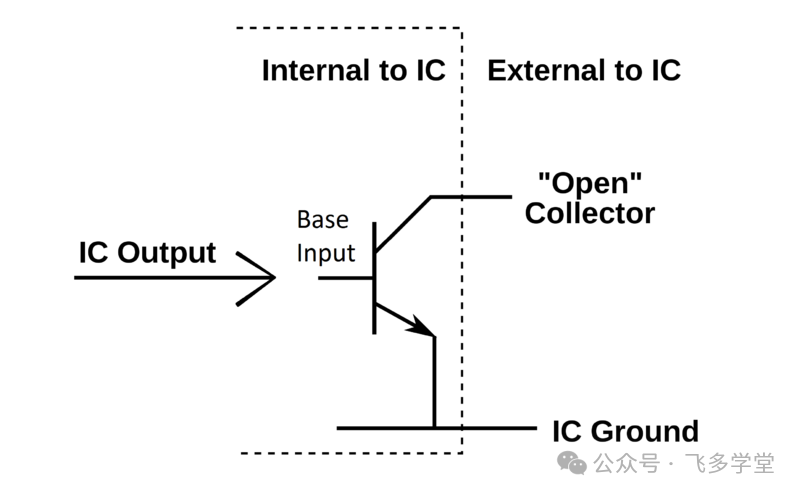

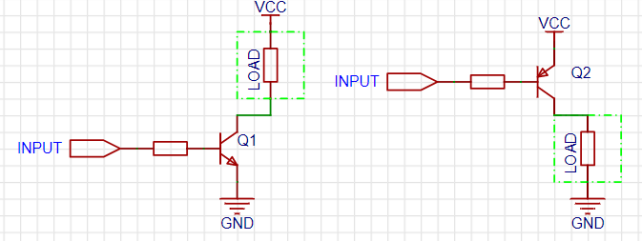

集电极开路输出通过内部双极结型晶体管 (BJT) 的基极处理 IC 的输出,该晶体管的集电极暴露为外部输出引脚。

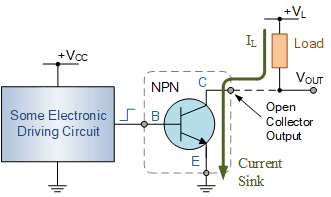

对于 NPN 开路集电极输出,NPN 晶体管的发射极在内部接地, 因此 NPN 开路集电极在内部形成短路(技术上低阻抗或“低 Z”)连接到晶体管导通时的低电压(可能接地),或晶体管关闭时的开路(技术上高阻抗或“hi-Z”)。输出通常连接到外部上拉电阻,当晶体管关闭时,该电阻将输出电压拉至电阻的电源电压。

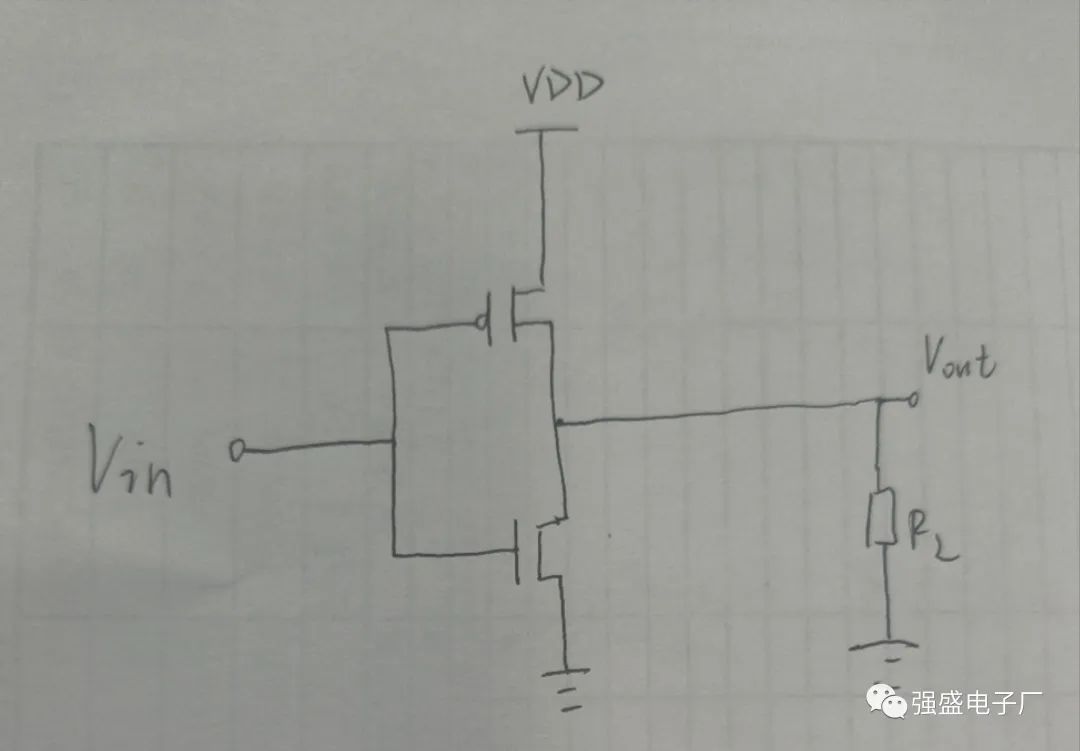

对于NPN开漏输出,NPN晶体管的发射极内部连接到地,因此当晶体管开启时,NPN开漏内部形成短路(技术上是低阻抗或“低-Z”)连接到低电压(可能是地线),或者当晶体管关闭时形成开路(技术上是高阻抗或“高-Z”)。输出通常连接到外部上拉电阻,当晶体管关闭时,上拉电阻将输出电压拉到电阻的供电电压。

对于 PNP 集电极开路输出,PNP 晶体管的发射极在内部连接到正电压轨,因此集电极在晶体管导通时输出高电压,在晶体管截止时输出高阻态。这有时称为“集电极开路,驱动高”。

什么是开漏输出

开漏输出(Open drain)是一种电路设计中常见的输出模式,它允许多个设备共享同一输出线。在这种模式下,输出端口可以被拉低以接地,但不能被拉高。这种设计可以用于连接到其他设备的输入端口,以便它们可以通过外部上拉电阻来拉高输出端口。

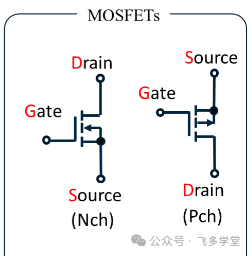

上图中的 Drain 是漏极,Source 是源极。

开漏输出使用 MOS 晶体管 (MOSFET) 代替 BJT,并将 MOSFET 的漏极暴露为输出。

如果没有外部上拉电阻,当高电压施加到 MOSFET 栅极时,nMOS 开漏输出接地,OK 没问题。但是,当低电压施加到栅极时呈现高阻抗。由于 MOSFET 不导通,该高阻抗状态下的电压将是浮动的(未定义),这就是为什么 nMOS 开漏输出需要一个连接到正电压轨的上拉电阻器以产生高输出电压。

使用 nMOS 开漏输出的 MOS 管可能会提供“弱”(高电阻,通常约为 100 kΩ)内部上拉电阻,以将相关引脚连接到器件的正电源,因此它们的输出电压不会漂浮。这种弱上拉电阻由于其较低的 而降低了功耗,并且可能避免对外部上拉的需要。外部上拉可能会“更强”(较低的电阻,也许 3 kΩ),以减少信号上升时间(如 I²C)或最大限度地减少噪声(如系统 RESET 输入)。

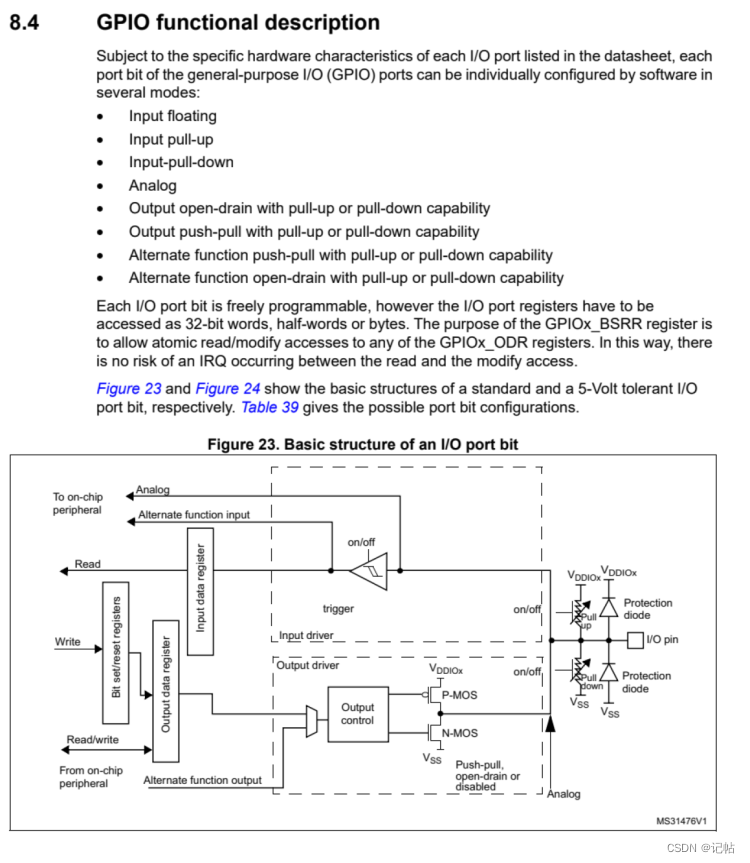

现代微控制器可能允许对特定输出引脚进行编程,以使用开漏输出而不是推挽输出、内部上拉的强度,并允许在不需要时禁用内部上拉。

对于 pMOS 开漏极,当晶体管导通时,输出连接到正电源轨,而当晶体管关断时,输出为高阻抗。这有时称为“开漏,驱动高”。

应用

开漏输出和开集输出是两种常用的电路输出模式,它们的区别在于使用的器件不同,开漏输出使用MOS管,开集输出使用三极管。这两种输出模式的共同特点是高电平时输出高阻,需要借助外部上拉电阻才能输出高电平。这样可以实现以下几个方面的应用:

电平转换:由于输出电平由上拉电阻连接的电源电平决定,所以可以很方便地实现不同电平之间的转换,例如从3.3V转换到5V,或者从5V转换到12V等。

线与功能:由于多个开漏输出或开集输出可以直接连接在一起,形成一个总线,所以可以实现线与功能,即只有当所有信号全部为高电平时,总线为高电平;只要有任意一个或者多个信号为低电平,则总线为低电平。这样可以实现信号的逻辑运算和同步控制,例如在I2C总线中,就使用了开漏输出来实现线与功能。

电流放大:由于开漏输出或开集输出的输出电流由上拉电阻的大小决定,所以可以通过调节上拉电阻的阻值来实现电流的放大,例如在LED驱动中,就可以使用开漏输出或开集输出来提供较大的电流。

当然,开漏输出和开集输出也有一些缺点,例如:

输出速度慢:由于输出高电平时需要通过上拉电阻充电,而上拉电阻的阻值不能太小,否则会造成过大的功耗,所以输出高电平的速度会受到限制,不能达到很高的频率。

功耗大:由于输出低电平时需要通过上拉电阻放电,而上拉电阻的阻值不能太大,否则会影响输出电平的稳定性,所以输出低电平时会有较大的功耗,不能实现低功耗的设计。

审核编辑:刘清

-

上拉电阻

+关注

关注

5文章

359浏览量

30607 -

MOS管

+关注

关注

108文章

2410浏览量

66759 -

晶体管

+关注

关注

77文章

9682浏览量

138080 -

电源电压

+关注

关注

2文章

989浏览量

23969 -

开漏输出

+关注

关注

0文章

34浏览量

7319

原文标题:开漏输出和开集输出的原理、特点和应用

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

GPIO推挽输出和开漏输出模式区别详解

一文详解开漏输出和开集输出的原理、特点和应用

一文详解开漏输出和开集输出的原理、特点和应用

评论