结论

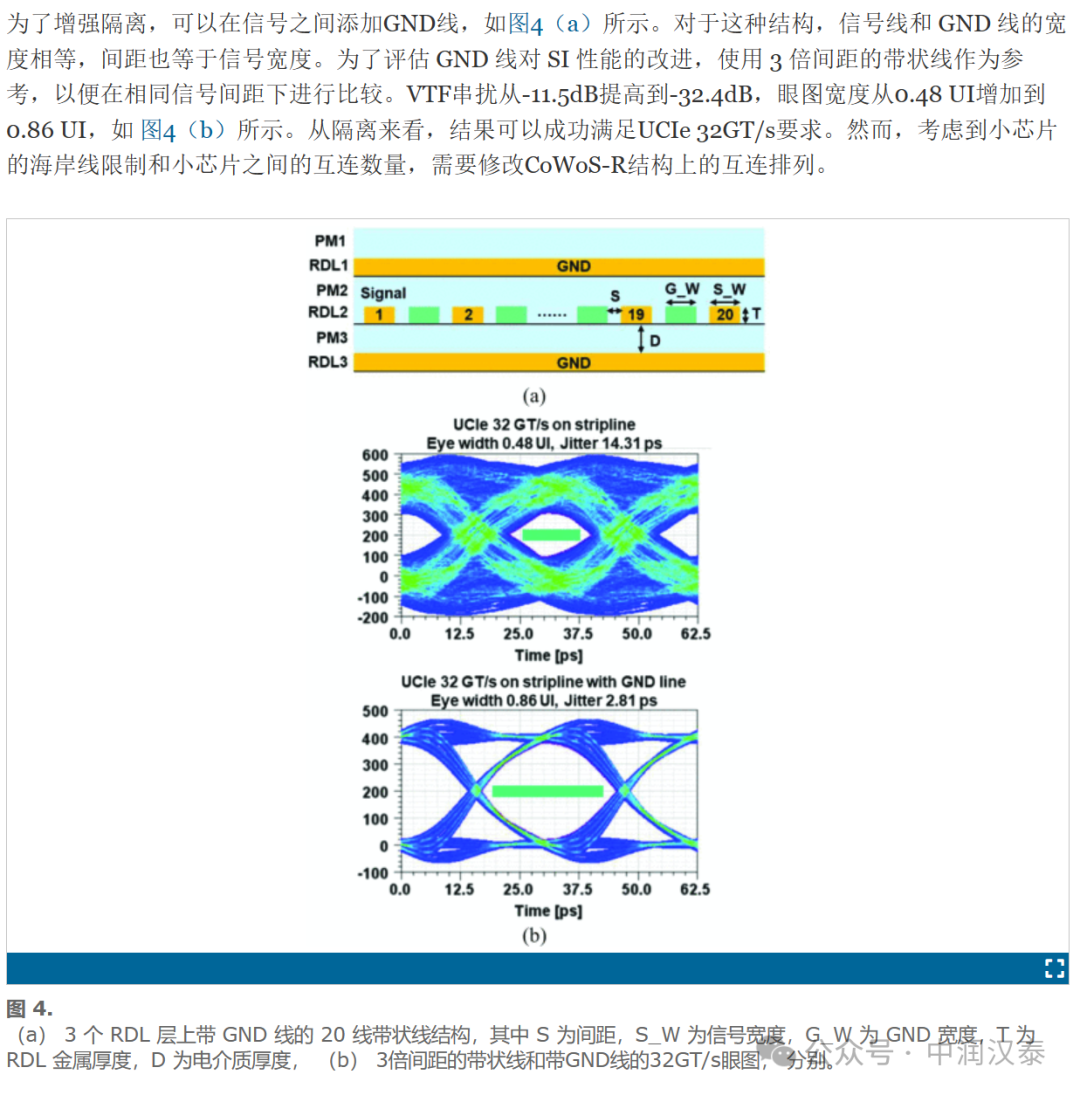

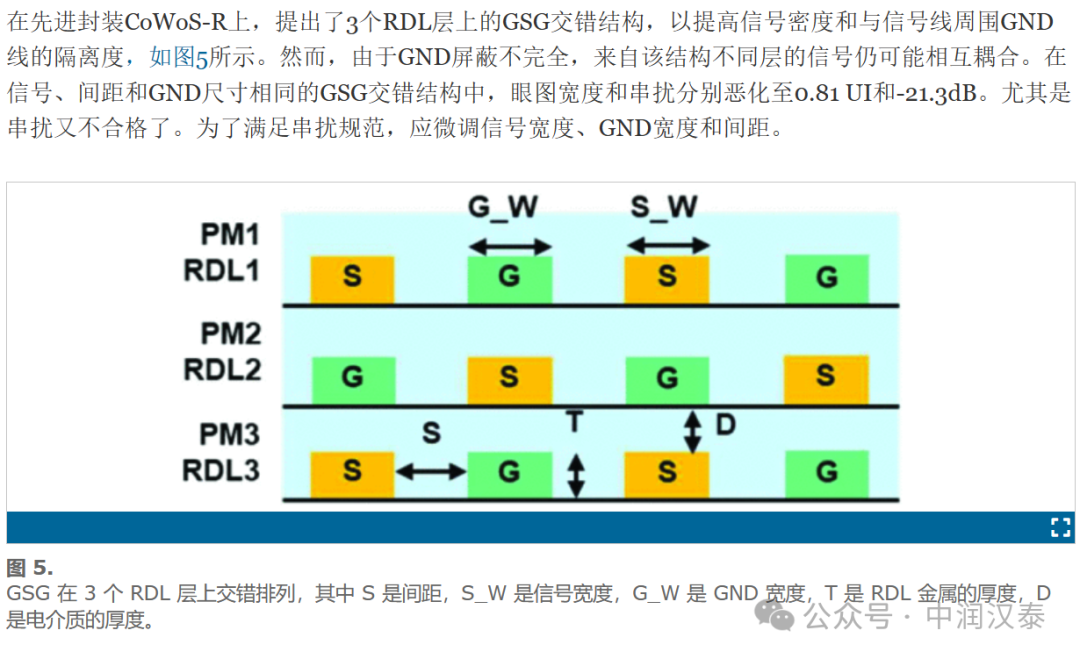

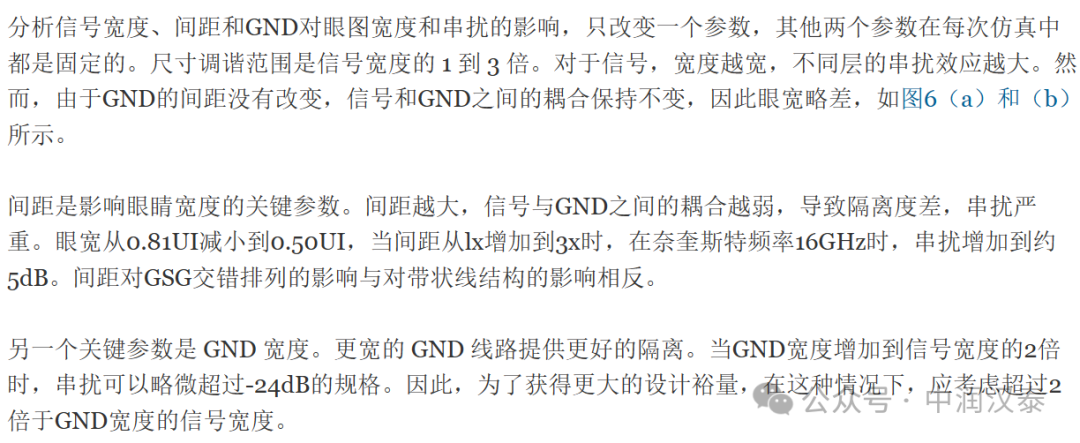

基于 CoWoS-R 技术的 UCIe 协议与 IPD 的高速互连是小芯片集成和 HPC 应用的重要平台。对于SI性能,研究了信号宽度、间隔和GND宽度对电气性能的影响。对于最高数据的 UCIe 32GT/s,信号线之间的接地屏蔽对于降低 VTF 串扰至关重要。在多层RDL结构中,GSG交错结构具有良好的串扰隔离和高带宽信号密度。最后,微调信号线、间距和GND线的尺寸,以获得CoWoS-R技术上最高的数据速率UCIe 32GT/s路由。

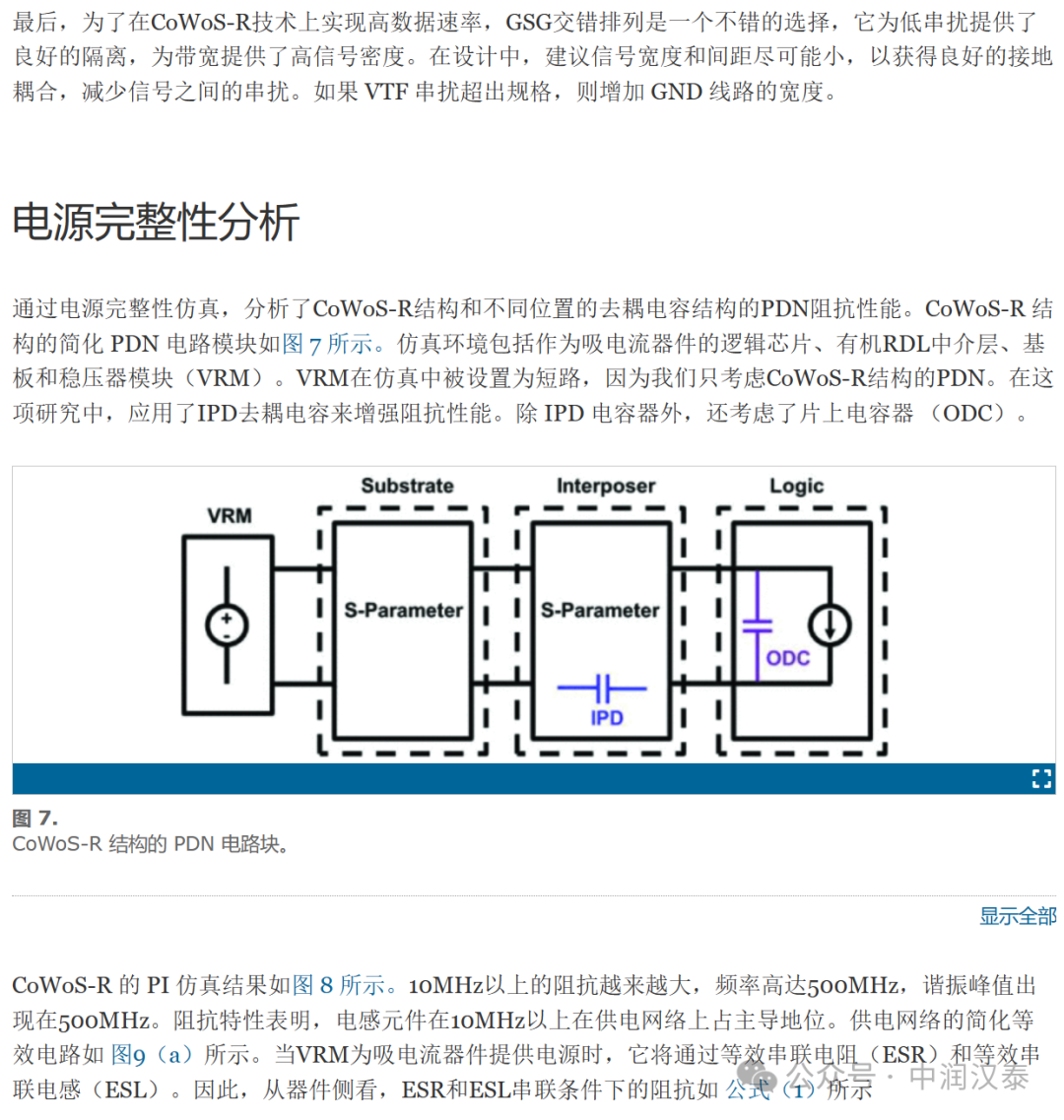

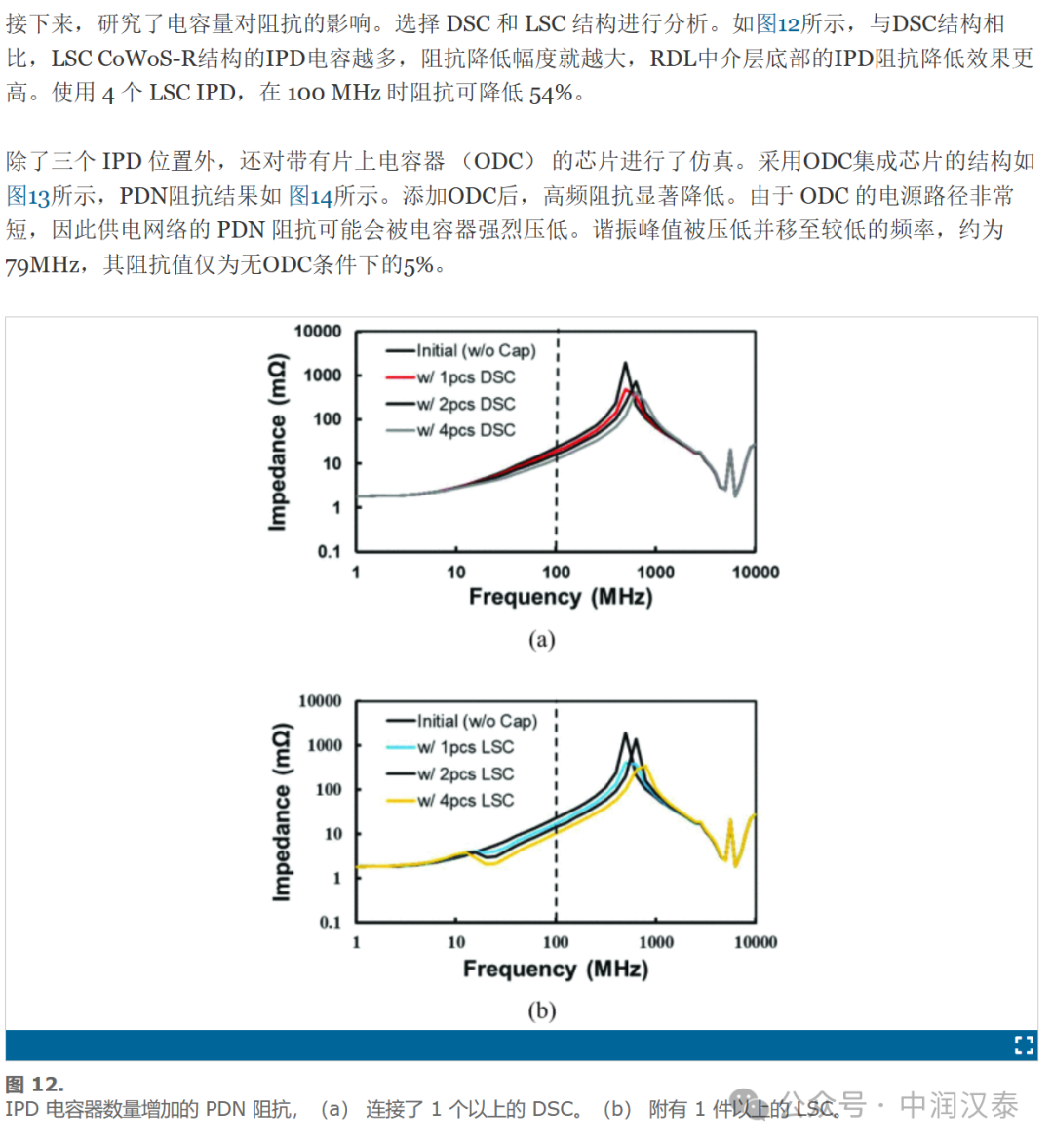

对于PI性能,分析了结构的PDN阻抗。为了降低总PDN阻抗,施加了IPD去耦电容。RDL中介层底部的IPD电容称为陆侧电容,在100 MHz时阻抗降低23%。使用 IPD 的 4,阻抗可以进一步降低 54%。除地面电容器外,还研究了片上电容器对阻抗的影响。它可以进一步降低谐振峰值和更高频率下的阻抗。

本篇摘自:CT,Wang, etc:Signal and Power Integrity Performance of CoWoS-R in Chiplet Integration Applications 2023

审核编辑:刘清

-

信号完整性

+关注

关注

68文章

1403浏览量

95454 -

电源完整性

+关注

关注

9文章

209浏览量

20725 -

HPC

+关注

关注

0文章

315浏览量

23748 -

CoWoS

+关注

关注

0文章

137浏览量

10485 -

chiplet

+关注

关注

6文章

431浏览量

12582

原文标题:灵活与变化:CoWoS封装在Chiplet中的信号及电源完整性

文章出处:【微信号:SinoEngineer,微信公众号:中润汉泰】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

CoWoS封装在Chiplet中的信号及电源完整性介绍

CoWoS封装在Chiplet中的信号及电源完整性介绍

评论