工程界常常使用保护地线进行隔离,来抑制信号间的相互干扰。的确,保护地线有时能够提高信号间的隔离度,但是保护地线并不是总是有效的,有时甚至反而会使干扰更加恶化。使用保护地线必须根据实际情况仔细分析,并认真处理。

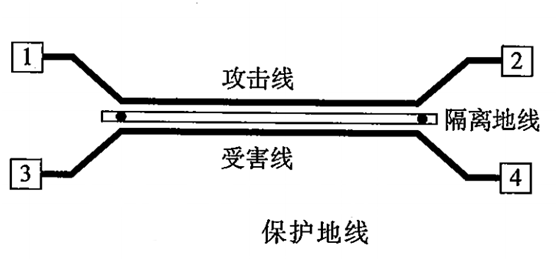

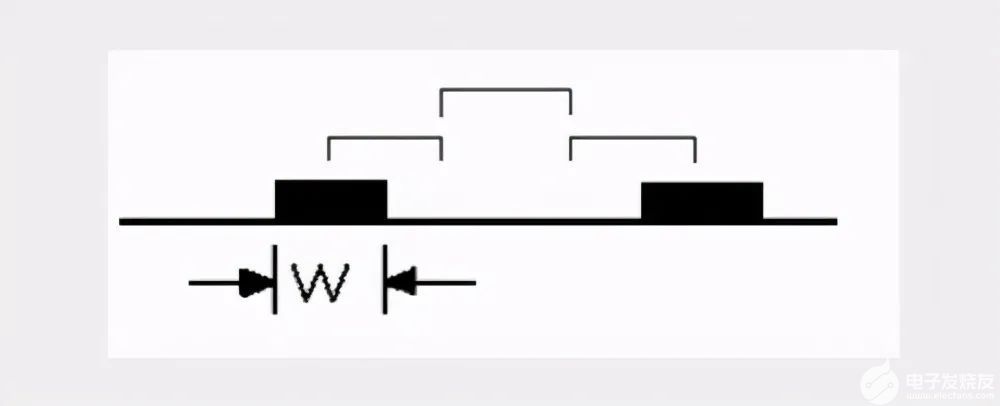

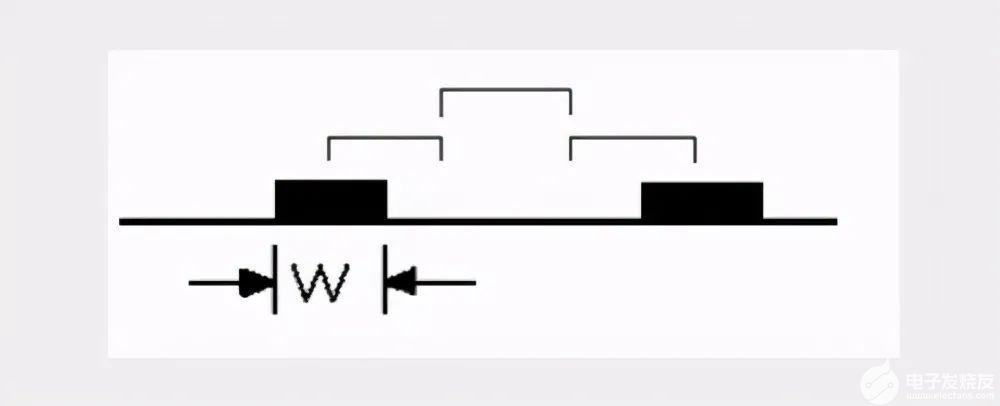

保护地线是指在两个信号线之间插入一根网络为GND的走线,用于将两个信号隔离开,地线两端打GND过孔和GND平面相连,如图所示。有时敏感信号的两侧都放置保护地线。

要想加入保护地线,首先必须把两个信号线的间距拉开到足以容纳一根保护地线的空间,由于拉开了信号线的间距,即使不插入保护地线,也会减小串扰。插入保护地线会有多大的作用?

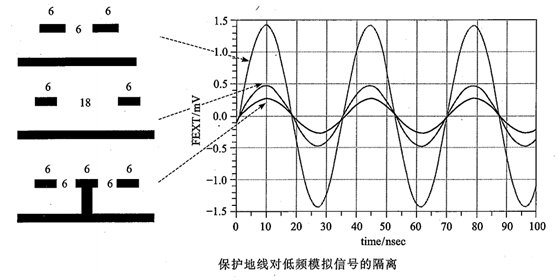

低频模拟信号包地

我们来看表层微带线情况下串扰的大小。假设走线是50Ω阻抗控制的,线宽为6mil,介质厚度为3.6mil,介电常数为4.5。并假设两路信号都是载波频率为30Mhz,带宽为2Mhz的模拟信号。

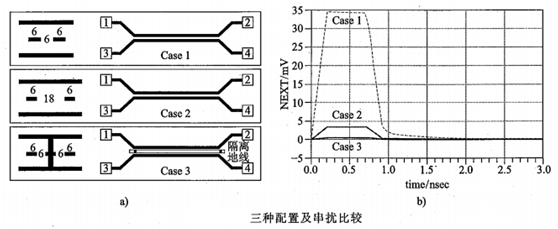

下图显示了三种情况下的远端串扰情况。当线间距为6mil时,由于两条线紧密耦合,远端串扰较大。把间距增加到18mil,远端串扰明显减小。进一步,在两条线之间加入保护地线,地线两端使用过孔连接到地面,远端串扰进一步减小。

对于低频模拟信号之间的隔离,保护地线的确很有用。这也是很多低频板上经常见到的“包地”的原因。但是,如果需要隔离的数字信号,情况会有所不同。我们分表层微带线和内层带状线两种情况来讨论保护地线对数字信号的隔离效果。以下讨论我没假定PCB走线都是50Ω阻抗控制的。

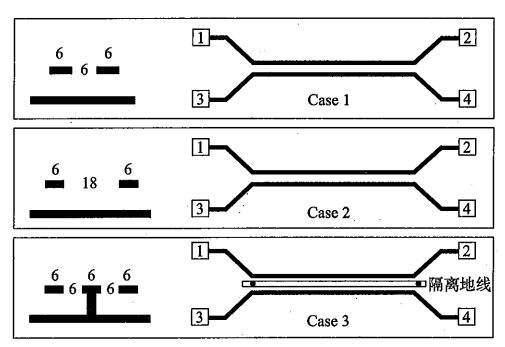

表层走线

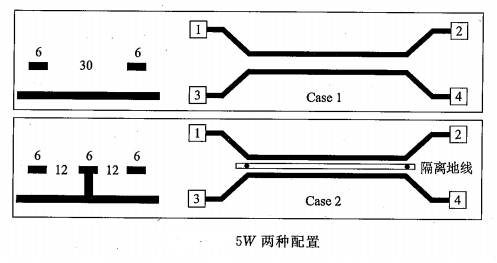

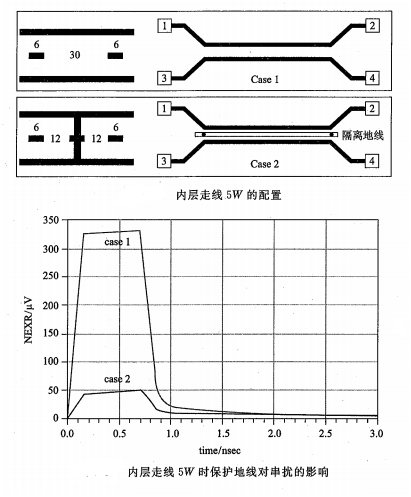

仍然使用上面的表层走线叠层结构,线宽为6mil,介质厚度为3.6mil,介电常数为4.5。攻击信号为上升时间Tr=200ps的阶跃波形。考虑以下三种情况下的近端串扰和远端串扰的情况,如下图所示,其中耦合段长度为2000mil。

Case1:两条走线间距gap=1w(w=6mil表示线宽);

Case2:两条走线间距gap=3w,仅仅拉大道能够放下一条保护线的间距,但不适用保护线;

Case3:两条线间距gap=3w,中间使用保护地线,并在两端打GND过孔。

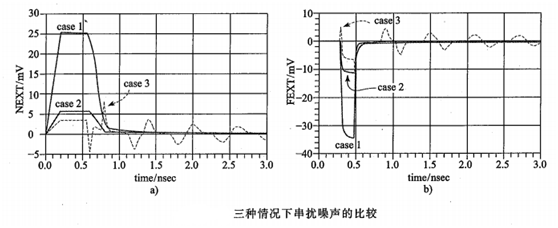

下图显示了三种情况下串扰波形,无论是近端串扰还是远端串扰,走线间距从1w增加到3w时,串扰都明显减小。在此基础上,走线间插入保护地线,串扰如下图中Case 3所示,相比Case 2,插入保护地线,不但没有起到进一步减小串扰的作用,反而增大了串扰噪声。

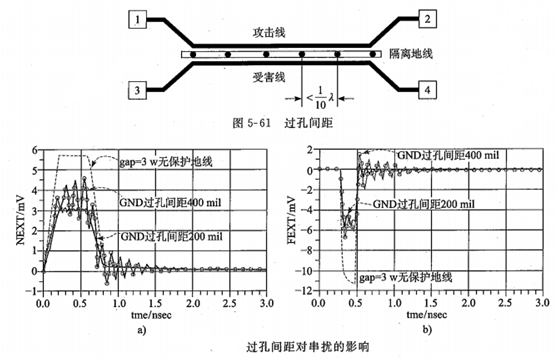

这个例子表明,拉开走线间距是最有效的减小串扰的方法。保护地线如果使用不当,可能反而会恶化串扰。因此,在使用保护地线时,需要根据实际情况仔细分析。保护地线要想起到应有的隔离作用,需要再地线上添加很多GND过孔,过孔间距应小于1/10λ,如图所示。λ为信号中最高频率成分对应的波长。

内层走线

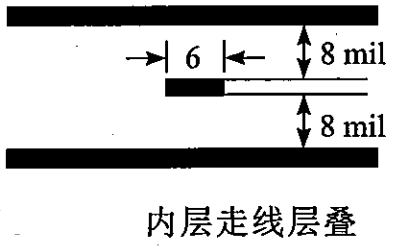

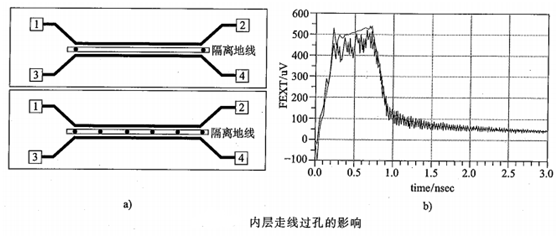

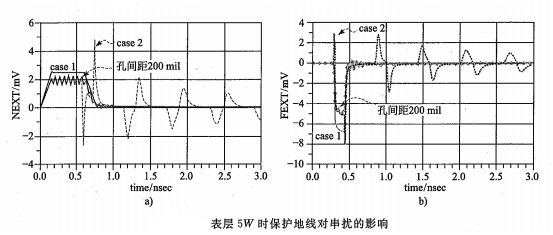

对于内层走线,如下图所示:

介电常数为4.5,阻抗为50Ω。考虑到下图三种情况。攻击信号为上升时间Tr=200ps的阶跃波形,入射信号幅度500mv,耦合长度为2000mil,近端串扰如图所示,加入了保护地线,近端串扰从3.44mV进一步减小到了0.5mV。信号隔离度提高了16B。对于内层走线,加入保护地线能够获得更大的隔离度。

对于表层走线来说,使用密集型的GND过孔,对提升隔离效果是有好处的。但是,对于内层走线来说,使用密集型的GND过孔几乎得不到额外的好处,下图对比了GND过孔间距为2000mil(保护地线两端打GND过孔)和GND过孔间距为400mil时的近端串扰情况,串扰量几乎没有变化。

间距增加到5w时情况如何?

当走线间距进一步加大,保护地线仍保持在6mil的线宽时,对于表层走线来说,保护地线的作用减小。在下图中,两条线间距拉到5w时,两种情况下近端串扰和远端串扰量和不使用保护地线情况相当,没有明显改善。因此,对于表层走线来说,走线间距很大时,中间再加入保护地线,几乎没有什么效果,如果处理不好反而会使串扰恶化。

对于内层走线来说,保护地线仍然会起很大作用。如下图,内层间距为5W,两种情况下近端串扰噪声波形如图。中间加入了保护地线,能明显改善近端串扰。

结论

1)保护地线对低频模拟信号的隔离通常都是有效的。但是在数字信号之间的保护走线并不是那么有用,有时反而会使情况更恶化。

2)对于表层走线,如果保护地线的GDN孔间距很大,可能会使串扰更加严重,必须使用非常密集的GND孔才能起到隔离的效果。

3)对于内层走线,保护地线可以减小近端串扰。

-

PCB设计

+关注

关注

394文章

4683浏览量

85563 -

模拟信号

+关注

关注

8文章

1128浏览量

52445 -

PCB走线

+关注

关注

3文章

135浏览量

13918 -

GND

+关注

关注

2文章

539浏览量

38697

原文标题:高速PCB设计中的打孔包地与串扰分析

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

什么是小间距QFN封装PCB设计串扰抑制?

解决PCB设计消除串扰的办法

高速PCB设计中如何消除串扰?

PCB设计中QFN封装的串扰抑制分析

谈谈高速PCB设计中的打孔包地与串扰

谈谈高速PCB设计中的打孔包地与串扰

评论