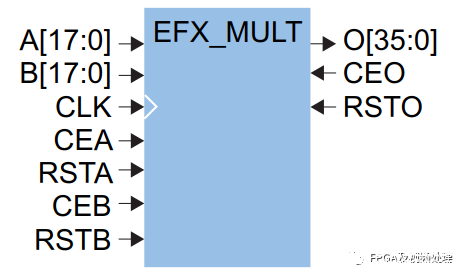

在使用Trion乘法器可能会遇到以下问题:

(1)[EFX-0652 ERROR] 'EFX_MULT' instance 'mult' port 'CEA' is not permanently disabled in the Register Bypass mode.

说明:如果输入寄存器A_REG没有使能,CEA接口要设置为0

(2)[EFX-0652 ERROR] 'EFX_MULT' instance 'mult' port 'RSTA' is not permanently disabled in the Register Bypass mode.

说明:如果输入寄存器A_REG没有使能,RSTA接口要设置为0

(3)[EFX-0652 ERROR] 'EFX_MULT' instance 'mult' port 'CLK' is not permanently disabled in the Register Bypass mode.

说明:如果输入和输出寄存都没有使用的话,时钟也要设置为0。

所以这里提供下面的写法供参考。

EFX_MULT.WIDTH(18),.A_REG(AREG),.B_REG(BREG),.O_REG(OREG),.CLK_POLARITY(1'b1), // 0 falling edge, 1 rising edge.CEA_POLARITY(1'b1), // 0 falling edge, 1 rising edge.RSTA_POLARITY(1'b0), // 0 falling edge, 1 rising edge.RSTA_SYNC(1'b0), // 0 aynchronous, 1 synchronous.RSTA_VALUE(1'b0), // 0 reset, 1 set.CEB_POLARITY(1'b1), // 0 falling edge, 1 rising edge.RSTB_POLARITY(1'b0), // 0 falling edge, 1 rising edge.RSTB_SYNC(1'b0), // 0 aynchronous, 1 synchronous.RSTB_VALUE(1'b0), // 0 reset, 1 set.CEO_POLARITY(1'b1), // 0 falling edge, 1 rising edge.RSTO_POLARITY(1'b0), // 0 falling edge, 1 rising edge.RSTO_SYNC(1'b0), // 0 aynchronous, 1 synchronous.RSTO_VALUE(1'b0) // 0 reset, 1 set) mult (.CLK((AREG || BREG || OREG) ? clk : 0),.CEA(AREG),.RSTA(AREG ? rst : 1),.CEB(BREG),.RSTB(BREG ? rst : 1),.CEO(OREG),.RSTO(OREG ? rst : 1),.A(A_in),.B(B_in),.O(O_out));

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

dsp

+关注

关注

561文章

8269浏览量

368144 -

原语使用

+关注

关注

0文章

2浏览量

1295

发布评论请先 登录

相关推荐

热点推荐

ADSP - 21992:高性能混合信号 DSP 控制器的深度剖析

ADSP - 21992:高性能混合信号 DSP 控制器的深度剖析 在电子工程领域,高性能的 DSP 控制器一直是推动各种应用发展的核心力量。今天,我们就来深入探讨一款功能强大的混合信号 DSP

Cadence推出专为新一代语音AI与音频应用打造的 Tensilica HiFi iQ DSP

第六代 HiFi DSP 为基于语音的 AI 应用和最新沉浸式音频格式带来更出色的性能与能效表现 1 中国上海,2026 年 3 月 19 日 —— 楷登电子(美国 Cadence 公司

Xilinx FPGA输入延迟原语介绍

在高速接口设计中,时序收敛往往是工程师面临的最大“噩梦”。当数据传输速率突破 800Mbps 时,微小的 PCB 走线差异都足以让系统崩溃。本文将深度剖析 Xilinx 7 系列(IDELAYE2)与 UltraScale 系列(IDELAYE3)的底层原理,带你彻底攻克输入延迟校准难题。

基于4片DSP6678+FPGA KU115 的VPX高速信号处理平台

Ø DDR4:1组32bit,2GB,2400MT/sØ 加载方式:BPI NorFlashl互联:Ø DSP1和DSP2间:Hyperlink x4Ø DSP3和

发表于 03-06 14:58

RDMA设计46:RoCE v2原语功能:单边语义

本博文主要交流设计思路,在本博客已给出相关博文约170篇,希望对初学者有用。注意这里只是抛砖引玉,切莫认为参考这就可以完成商用IP设计。

续上,为便于查看,给出表1部分表1 RoCE v2原语功能

发表于 03-01 23:14

RDMA设计45:RoCE v2 原语功能验证与分析2

本博文主要交流设计思路,在本博客已给出相关博文约170篇,希望对初学者有用。注意这里只是抛砖引玉,切莫认为参考这就可以完成商用IP设计。续上,为便于查看,给出表1部分

表1 RoCE v2原语功能

发表于 02-26 07:52

进程的控制

如下(创建原语):

1. 为新进程分配一个唯一的进程标识号,并申请一个空白的PCB(PCB是有限的)。若PCB申请失败则创建失败。

2. 为进程分配资源,为新进程的程序和数据、以及用户栈分配必要

发表于 01-15 06:05

DSP的基础

高速数字信号处理技术是以DSP为核心,具有高速,实时的特点的一种信息处理技术。其本质是信息的变换和提取。DSP(Digital Signal Processor),即数字信号处理器,是一种专用

发表于 11-20 06:35

DSP、FPGA之间SRIO通信的问题?

目前在使用DSP和FPGA之间通过SRIO的SWRITE事务完成双向数据通信,大多数情况下都正常,但是在我不停的给DSP进行烧写程序时,会偶尔出错,FPGA无法收到DSP下发的数据。偶尔故障情况下buf_lcl_phy_buf_

发表于 11-15 16:22

【技术贴】解密艾为飞天™DSP黑科技(二):产品迭代与性能飞跃

为飞天DSP目前的产品迭代与演进。艾为飞天DSP产品的演进其中下图是展示了第一代艾为飞天DSP产品到最新一代的主要特性和重点参数的变化。图1艾为飞天

DSP芯片与800G光模块的核心关系:Transmit Retimed DSP、LPO与LRO方案的探讨

本文深入探讨DSP芯片在800G光模块中的核心作用,包括Transmit Retimed DSP架构与新兴LPO/LRO方案的对比分析。DSP在信号均衡、误码控制与长距离传输中不可或缺,而LPO/LRO以低功耗优势适用于短距互联

音频DSP设计与应用

DSP(即数字信号处理器)对于音频处理技术至关重要。

新唐DSP集成了Waves(Maxx音频),DSP 算法的全球领导者。这包括专用的扬声器校准算法和心理声学算法。此外,它还具有强大的音频算法

发表于 09-05 07:45

DSP从入门到精通全集

这是一本循序渐进介绍DSP的书籍,从DSP的入门知识介绍到DPS的硬件,接口,应用,从DSP的ADC/DAC到数字滤波器处理。本文除了对DSP的各种软硬件知识进行介绍后,还结合实际,接

发表于 07-12 14:36

Trion DSP 原语使用问题 - 1

Trion DSP 原语使用问题 - 1

评论