在高性能计算(HPC)、大数据和人工智能/机器学习(AI/ML)领域占据主导地位的今天,计数系统成为了热议的焦点。尽管传统上各种计算环境常采用浮点数进行运算,但由于Posit在HPC应用中提供了更高的精度,它逐渐受到开发者的青睐。

位于“印度硅谷”的初创公司CalligoTech,专注于开发针对HPC、大数据和AI/ML的产品和解决方案,推动了Posit算法在硬件和软件领域的商业化。该公司最近推出的加速器TUNGA采用了基于Unum的新一代算术技术,并且是首款应用Posit的多核RISC-V处理器。借助新思科技的数字设计系列,CalligoTech成功完成了这款处理器的流片工作,并正在致力于交付更高能效的CPU。

对于我们这样的初创公司来说,完整的数字设计流程和强有力的支持对我们的成功至关重要。新思科技在这两方面都给予了积极响应,并提供了经过代工厂验证的签核工具,帮助我们顺利完成流片。

为什么Posit如此受关注?

浮点数是计算机编程中实数的数字表示,无论实数大小,都可以用浮点数表示。其中,小数点可以在数字之间“浮动”,从而使得计算更加灵活、结果更加准确。浮点数于20世纪中叶首次引入,自现代计算早期以来一直沿用至今。IEEE浮点运算标准于1985年首次发布。浮点数非常适合一般计算任务,例如图形、声音处理和大多数软件应用。

HPC的兴起对更准确的计数类型提出了需求。于是,Posit应运而生。Posit以数学家John Gustafson博士引入的通用数Unum为基础,是Unum的硬件友好版本。与传统的浮点数相比,Posit可以处理更大范围的数字并提供更高精度的计算,这对于HPC应用来说尤为重要。在HPC应用中,超级计算机需要实时处理繁重的工作负载,因此需要更为准确的计算结果。而且,提高性能并降低功耗是迈向节能CPU的第一步。

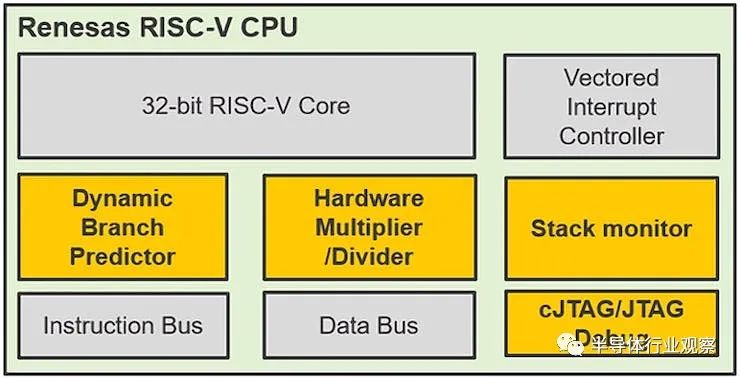

CalligoTech成立于2012年,早期致力于开发基于软件和硬件的加速器,2018年开始专注于硬件解决方案,并于同年开始与新思科技开展合作。从2021年开始,CalligoTech的团队开始致力于将其RISC-V加速器设计转化为具体的芯片。该加速器包含一个协处理器,将根据与RISC-V处理器集成的Posit计数系统执行计算。Posit处理器能够以更少的位数生成准确的结果,相当于以更低的功耗实现更高的处理速度,从而形成一个高能效且计算准确的CPU内核,CalligoTech将这种结合了RISC-V架构和Posit技术的处理器核心命名为“CRISP内核”。与传统方案相比,该加速器仅需较低功耗和内存提供更准确的结果,因此非常适合人工智能和其他HPC应用,例如基因组学、石油和天然气仿真、金融、半导体设计、天气建模和医疗卫生等。

在传统的浮点系统中,对数字进行四舍五入可能会导致出现计算误差,进而对HPC应用造成严重影响。基于Posit的计数系统能够带来更出色的计算性能和准确性。我们正在提供一种替代方案,可以为支持AI等计算密集型应用的下一代设计提供助力,有效降低风险。

150万门级的完整芯片设计流程

CalligoTech率先生产出了基于Posit的商用多核RISC-V加速器芯片。回想设计之初,该公司首先需要选择代工厂和适合的工艺设计套件(PDK)库。PDK库的选择会显著影响芯片的功耗、性能和面积(PPA)以及成本,是一个非常关键的决策,需要清晰地了解项目的各方面内容,包括技术节点、设计约束、制造工艺以及与电子设计自动化(EDA)工具的兼容性。

经过综合评估,CalligoTech最终决定使用新思科技数字设计系列来支持其RTL到签核流程。在此过程中,新思科技的技术专家与其团队紧密协作,帮助建立PDK库,并为RTL到签核流程提供PPA优化方案,最终助其实现了PPA目标。不仅如此,新思科技还通过密切合作,帮助该团队中原本习惯使用其他竞品流程的开发者在短时间内熟练掌握了新思科技的设计流程。

新思科技团队让我们对IC Compiler II布局布线解决方案充满了信心,相信其完全可以处理我们设计的所有150万门级。这些数字设计工具的稳定性以及高效的设计流程,结合新思科技团队的专业支持,我们的四名开发者才得以在紧迫时间节点内顺利完成了项目。

CalligoTech将继续构建基于Posit的加速器技术,其团队未来计划将新思科技接口IP和内存IP集成到下一代器件中。

-

处理器

+关注

关注

68文章

19159浏览量

229109 -

人工智能

+关注

关注

1791文章

46845浏览量

237531 -

机器学习

+关注

关注

66文章

8377浏览量

132404 -

大数据

+关注

关注

64文章

8863浏览量

137289 -

RISC-V

+关注

关注

44文章

2228浏览量

46023

原文标题:150万门级 + Posit + RISC-V,这款新一代大规模计算芯片流片成功

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

多核RISC-V处理器供应商超睿科技全力支持RT-Thread Smart,共同赋能“大芯片”生态

RISC-V适合什么样的应用场景

请问ESP32s3 ULP RISC-V协处理器是否支持ADC的读取?

risc-v多核芯片在AI方面的应用

国产RISC-V MCU推荐

Achronix与Bluespec联合宣布推出一款支持Linux的RISC-V软处理器

RED Semiconductor宣布推出算法微处理器ISA和硬件设计RISC-V

芯来科技正式发布基于RISC-V处理器的HSM子系统解决方案

CalligoTech推出首款应用Posit的多核RISC-V处理器

CalligoTech推出首款应用Posit的多核RISC-V处理器

评论