引言:上一篇介绍了BGA封装PCB层数估计、BGA焊盘设计、过孔设计、信号走线等内容,本文我们介绍下FPGA BGA封装电源管脚布线。

1. 概述

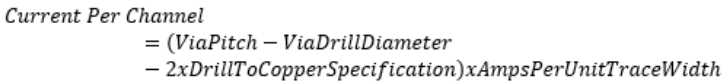

工程师必须在设计阶段早期评估功率需求,以确保有足够的层和面积为需要功率的BGA焊盘提供足够的功率。因为大多数BGA电源引脚位于BGA区域的中心,所以电流行进的路径穿过BGA区域中的无数过孔。过孔之间的空间可以保守地承载约0.05A/mil的走线宽度(对于0.5盎司的铜)。过孔之间的迹线宽度由过孔的节距(通常与BGA的节距相同)、过孔钻头直径和制造厂定义的钻铜规格来定义。下图显示了如何计算可以通过每个通路的电流量。确保电源平面足够宽,足够包容,以便为BGA电源球提供所需的安培数。以下方程可用于计算每个通道的电流:

图1:BGA区域内的电力输送(0.5盎司铜)

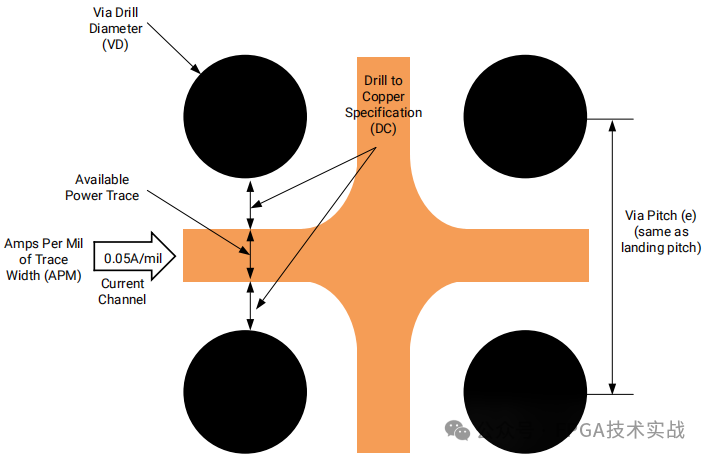

下表显示了0.8 mm和1.0 mm间距器件的每个通道的电流值。由于0.5mm器件的间距非常细,因此不可能在标准过孔之间布线。为了到达电源平面,对于0.5mm焊盘器件建议通过BGA焊盘下的微过孔实现与电源层互联。

表1:0.8 mm、0.92 mm和1.0 mm器件的每通道电流计算

2. 用于远距离电压感测线(Sense Lines)的PCB布线

为了正确补偿由于高电流负载引起的PCB上的IR电压降,电压调节器模块(VRM)感测线的正确布线对于在ACAP管芯处保持适当的电压电平至关重要。

注意:由于调节器的设计、引脚和要求各不相同,请务必始终遵循VRM供应商的感应线建议。

2.1 感应线的用途

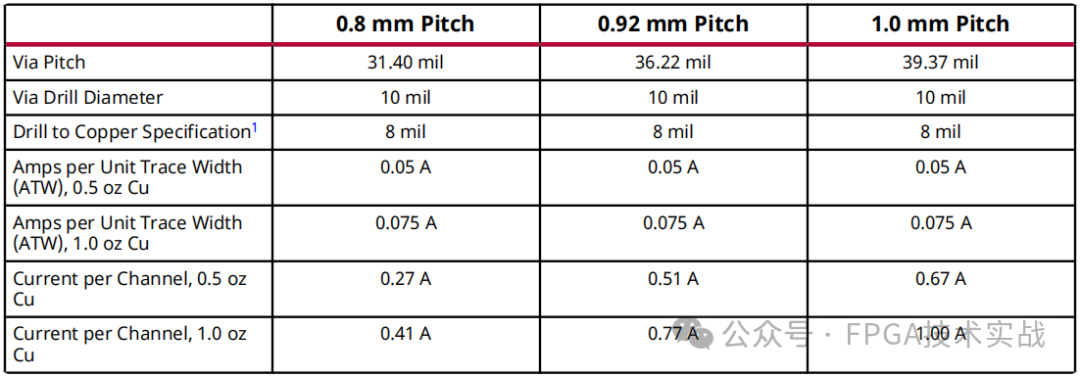

由于电压调节器通常与它们供电的设备相距很远,因此在调节器和负载的主要点之间的电压通常存在DC电压IR下降,特别是在存在高电流负载的情况下。如果调节器没有考虑到这种下降,负载点的电压可能比调节器看到的要低很多。由此产生的较低电压可能超出正确器件操作所需的极限。下图说明了电流的方向和由此产生的电压降。

图2:VRM和负载点之间的直流电压降

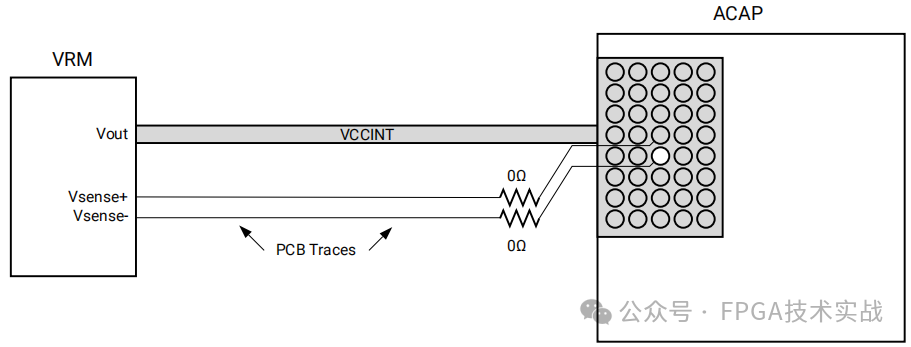

为了克服这种电压降,调节器实现了从调节器直接连接到负载点的感测线。这些感测线是调节器和负载点之间的直接迹线,不携带任何电流。因为它们不携带任何电流,所以调节器感测引脚处的电压与负载点处的电压完全相同。因此,调节器可以根据需要适当地调节其输出电压,使得负载点处的电压在所需的规格内。下图说明了从VRM到负载点的感测线的放置和布线。

图3:感应线示例

2.2 感应线的局限性

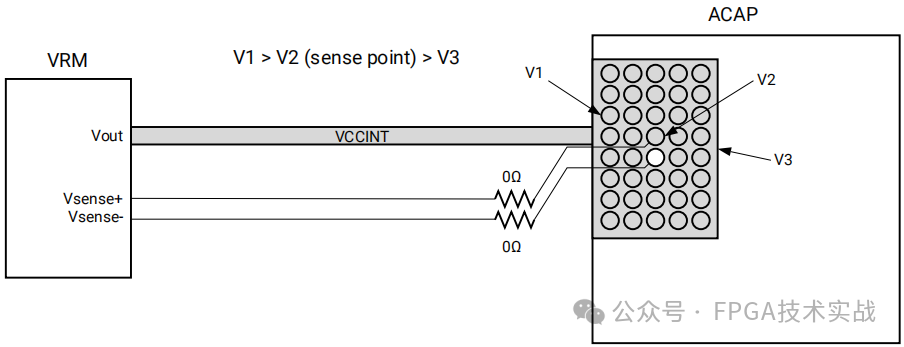

1)电压差

因为感测线只能放置在负载点的一个位置,所以感测点前面的其他区域可能显示出更高的电压,而负载点之外的点可能显示出更低的电压。下图说明了这种电压差异。当电流从VRM流到负载点时,点V1处的电压高于V2处的感测点。同样地,点V3处的电压低于感测点V2处的电压。

图4:BGA引脚中不同点的电压 2)只有一个感测引脚的VRM

某些VRM不包括用于接地的感测引脚。这种布置的主要限制是VRM不考虑负载点处接地电压的波动,导致电压调节不太精确。

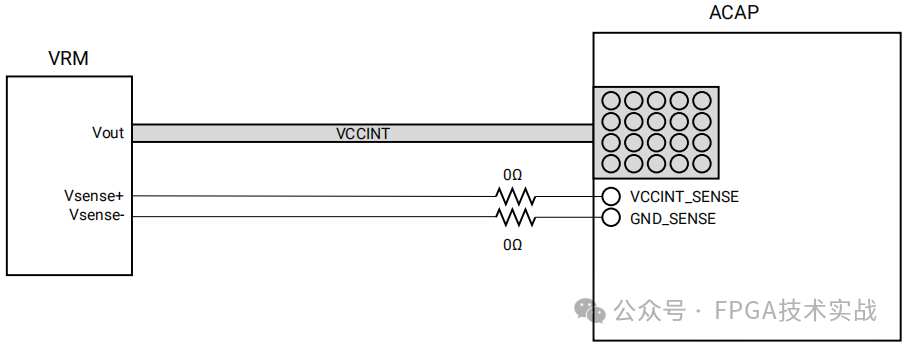

2.3 带专用检测引脚的ACAP

Select Versal ACAP包含用于VCCINT及其相关接地回路的专用远程电压感测引脚。它们提供了对模具最接近的观察。下图显示了具有专用感测引脚的ACAP的推荐感测线路布线。

•在ACAP附近放置内联0Ω电阻器:

○ 需要电阻器来确保感测线被布线为迹线,并且不会掉到平面上。

•将感应线路布线为50Ω松耦合差动传输线路:

○ 需要接地才能感应到电源和接地之间的真正差异。

图5:专用感测引脚布线

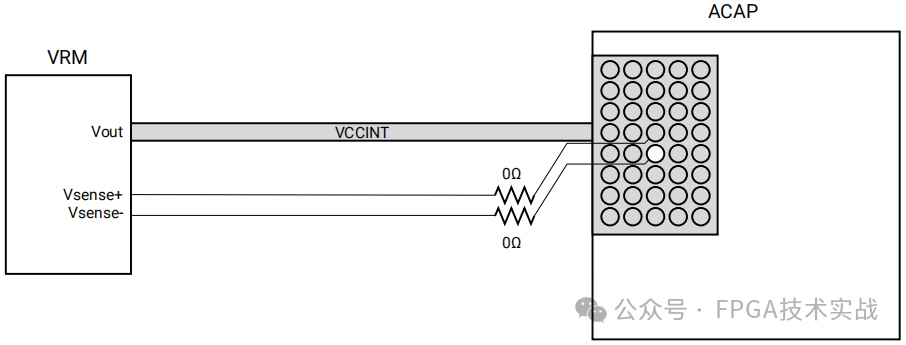

2.4 无专用检测引脚的ACAPS

对于没有专用感测引脚的ACAP,感测线连接应连接到尽可能靠近ACAP上最重要负载点的BGA球。这可以通过直流模拟或Vivado工具中的设备视图进行最佳估计。如果无法估计负载点,建议将感测连接朝向BGA引脚场的中心。将球放置在离调节器最远的位置也是一种选择,但不太可取。

•在ACAP附近放置内联0Ω电阻器:

○ 需要电阻器来确保感测线被布线为迹线,并且不会掉到平面上。

•将感应线路布线为50Ω松耦合差动传输线路:

○ 需要接地才能感应到电源和接地之间的真正差异。

为了实现最佳的功率传输,确保连接到感测线的球完全连接到它们各自的平面,即,不要将它们作为“间谍孔”未连接(见下图)。

图6:没有专用感测引脚的布线

图6:没有专用感测引脚的布线

2.5 路由隧道和感测线的使用

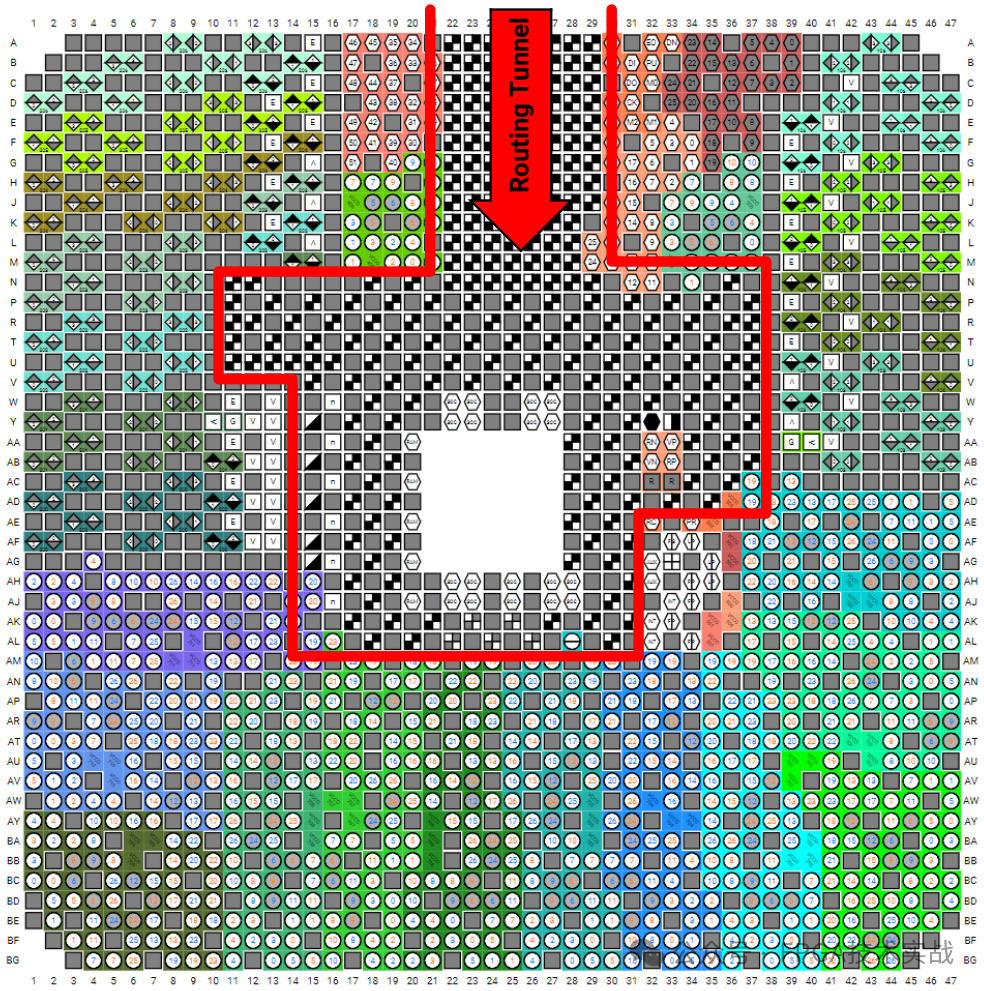

一些Versal ACAP具有专门放置的BGA引脚的专用“隧道”(Tunnel),以便以最小的IR压降提供最大的功率传输。这种所谓的路由隧道消除了导致电源平面出现孔洞的过孔阻挡区域。布线通道中的引脚不会直接连接到ACAP上的管芯。这些引脚的存在只是为了使VCCINT的PCB布线平面不需要来自其他信号或电源轨的过孔。

下图显示了带有VCCINT引脚字段的VC1902-A2197器件的BGA引脚区域。布线隧道区域中的引脚不需要到下面的VCCINT平面的过孔,因此在向VCCINT供电的金属平面中没有孔。最佳感测线放置在VCCINT引脚场上路由隧道外部的任何点上。

图7:带VCCINT路由隧道的VC1902-A2197

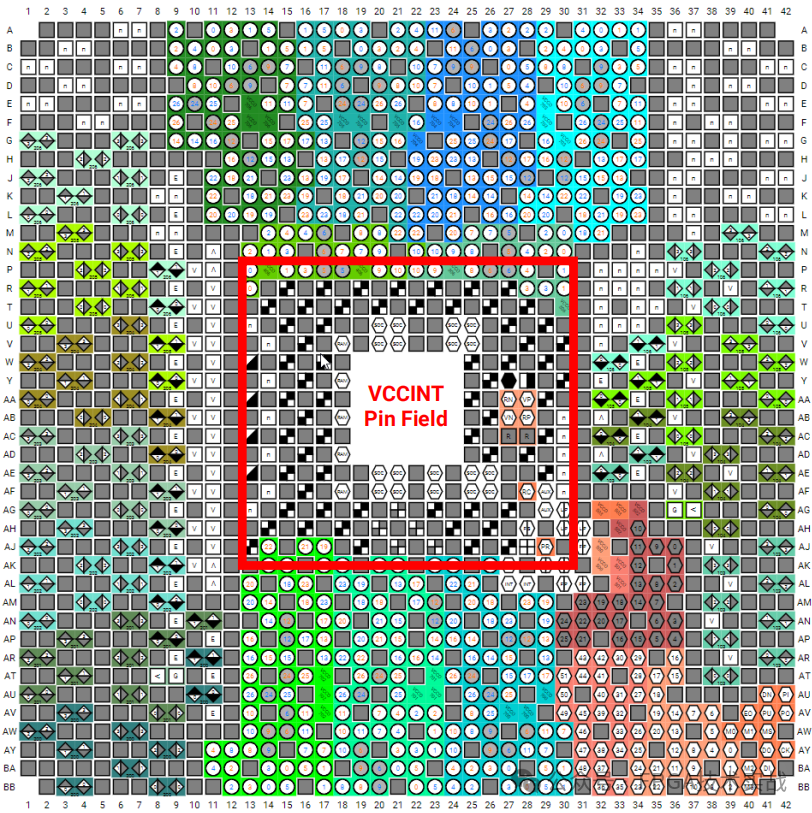

下图显示了带有VCCINT引脚字段的VM1802-C1760器件的BGA引脚字段。该设备上没有路由隧道,因此BGA上的功率平面具有过孔挡板,从而降低了功率传输效率。建议在该引脚场中心附近的任何位置放置感测线。

图8:VM1802-C1760 VCCINT引脚区域

-

FPGA

+关注

关注

1664文章

22553浏览量

640500 -

BGA

+关注

关注

5文章

588浏览量

52027 -

VRM

+关注

关注

0文章

32浏览量

13570 -

电压调节器

+关注

关注

3文章

197浏览量

19133 -

负载电压

+关注

关注

0文章

51浏览量

3126

原文标题:Xilinx FPGA BGA推荐设计规则和策略(二)

文章出处:【微信号:FPGA技术实战,微信公众号:FPGA技术实战】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Xilinx BGA设备的推荐设计规则和策略的用户指南免费下载

Xilinx 7系列FPGA介绍

Xilinx FPGA BGA设计:NSMD和SMD焊盘的区别

Xilinx FPGA BGA推荐设计规则和策略(二)

Xilinx FPGA BGA推荐设计规则和策略(二)

评论