易灵思提供了相关时序约束的PPT,内容非常全面,但是我们还是发现很多客户在使用Efinity时,时序约束存在很多问题。

添加约束

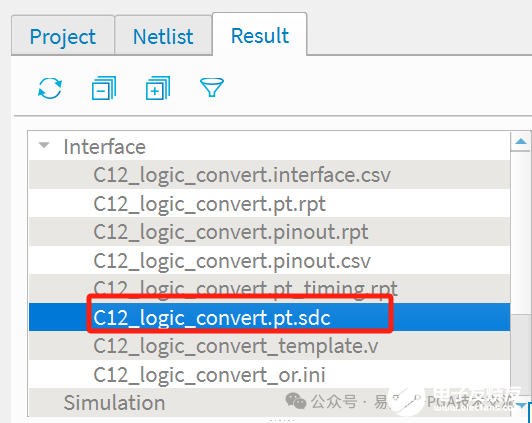

添加约束的目的是为了告诉FPGA你的设计指标及运行情况。在上面的生成约束之后,在Resultàxx.sdc中提供约束参考(请注意该文件不能直接添加到工程中,需要热复制到别的指定目录或者新建自己的SDC文件添加到工程)。

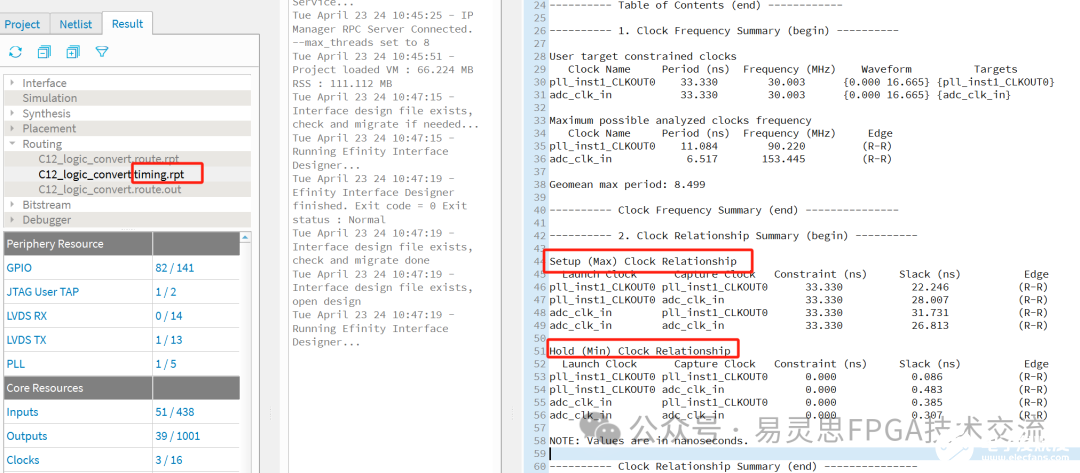

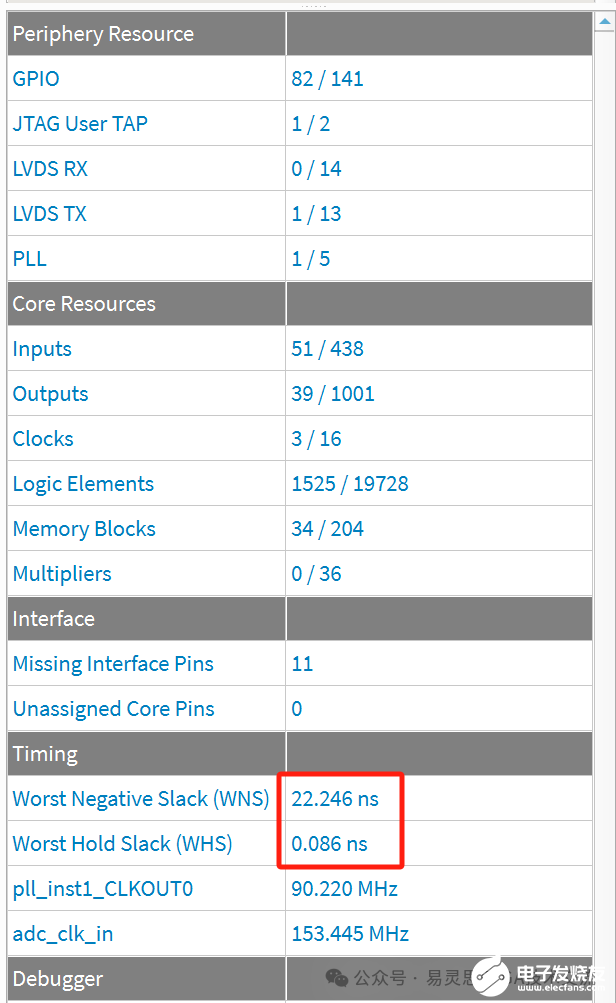

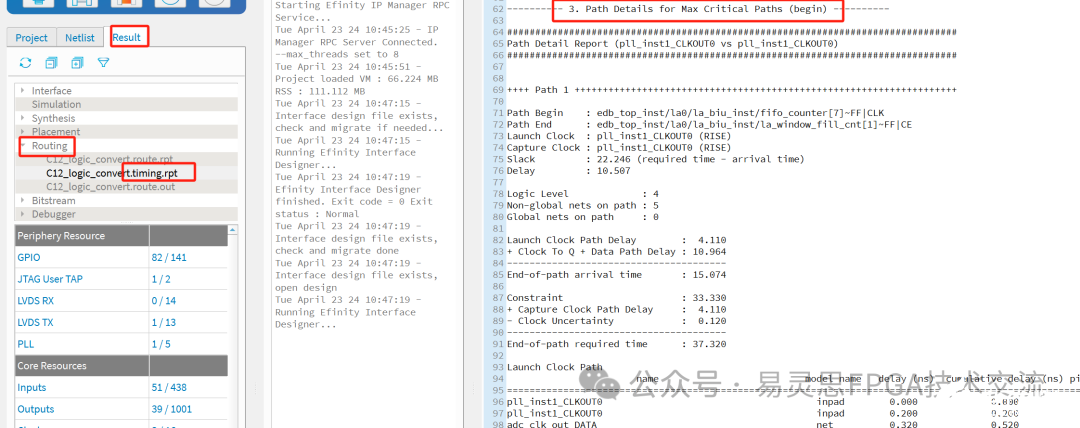

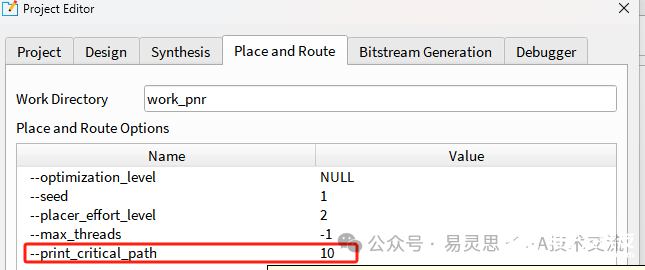

编译完成之后可以查看时序报告,也可以通过routingàxx.timing.rpt来查看路径详细延时信息,如果想查看更可以通过指令来打印或者通过print_critical_path来控制打印的路径数量 。

时钟约束

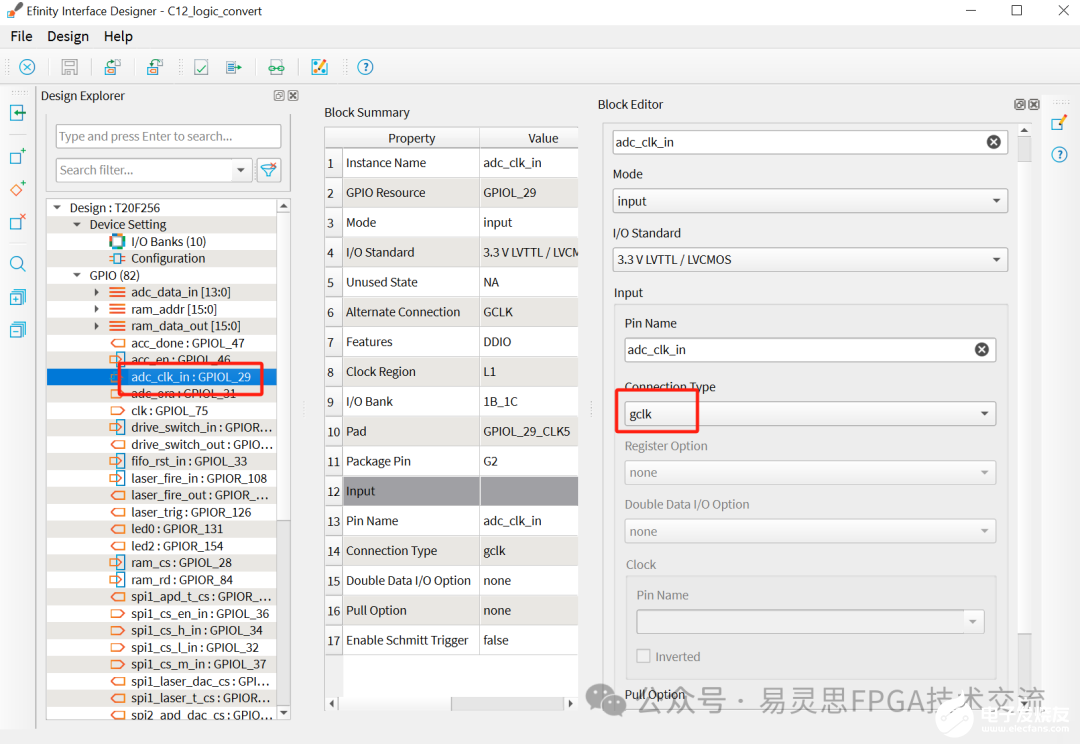

(1)通过IO输入的gclk。

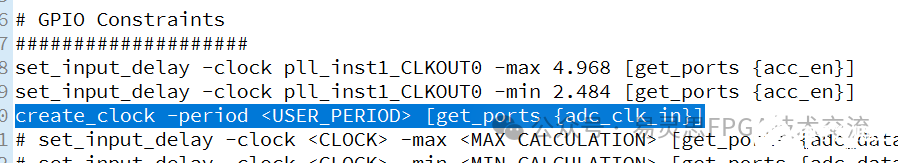

如下图,因为时钟是通过外部IO输入的,所以FPGA并不知道这个时钟频率是多少。打开.pt.sdc可以看到提供相关约束参考。

我们只需要补充相关的时钟周期即可以使用。

比如,我们要约束adc_clk_in为100M:

create_clock-period10.000[get_ports{adc_clk_in}]

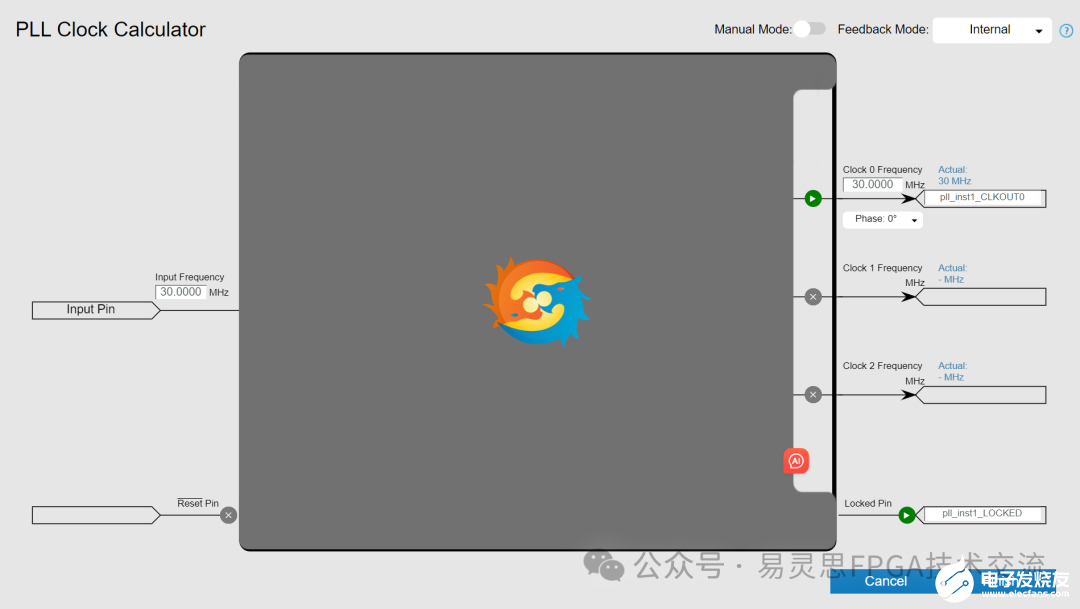

(2)PLL的输出的时钟约束。

因为PLL的输入输出频率都是设置好的,所以软件可以检测到。如下图,输入输出时钟频率都是30MHz.

在pt.sdc文件中会提供相应的约束 。

create_clock -period 33.3333 pll_inst1_CLKOUT0

在时钟约束完成之后,可以查看Routing -->.timing.rpt文件中所有的时钟是否都进行了完整的约束 。

IO约束

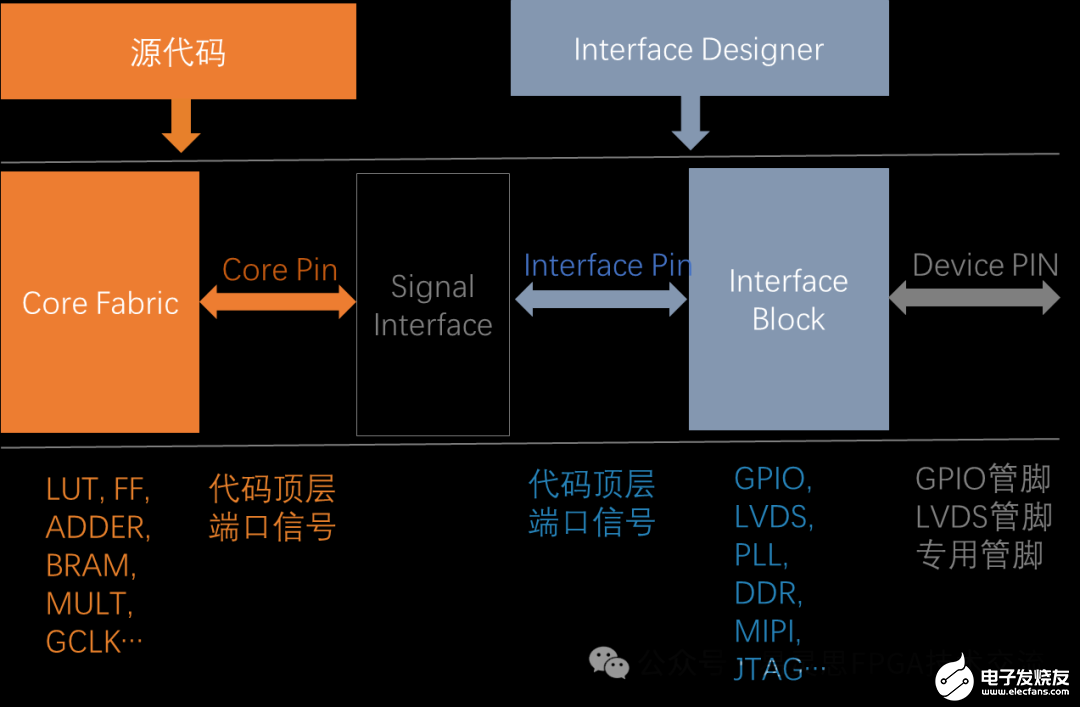

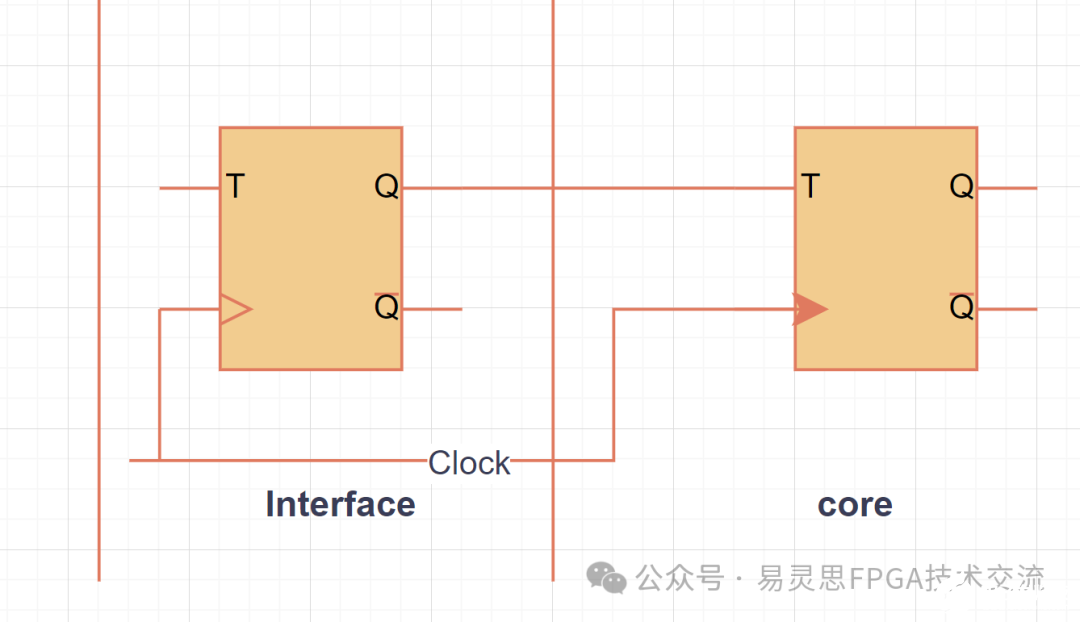

首先我们要了解易灵思的架构是core和interface分开的,相对于core,interface内部的GPIO,LVDS,JTAG及其它都是外设。所以所有针对于input_delay和outpu_delay的约束都是针对于interface的。至于FPGA对于我们平时理解的外设,比如FPGA外部连接一片AD/DA,这种是没有办法约束的。

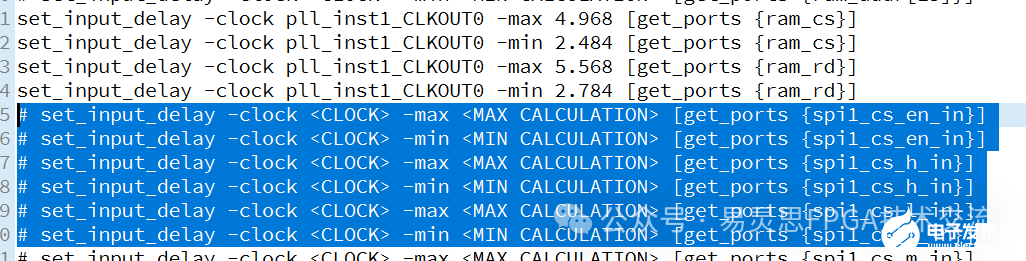

在pt.sdc文件中可以看到关于set_input_delay和set_output_delay的约束。可以看到有些约束是已经屏蔽,那是因为添加的IO没有打开寄存器。

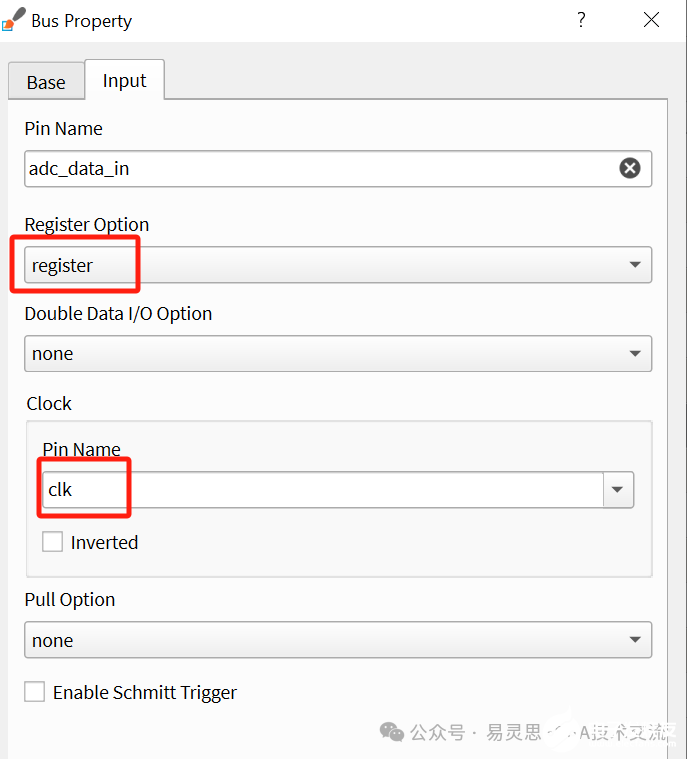

如下图,易灵思建议把所有IO都添加上IO寄存器。

有的客户会有疑问,clock的PIN Name是什么?其实就是与core内连接的寄存器用什么时钟,interface中就用什么时钟。

(3)跨时钟域约束

在保证程序上对跨时钟域做了处理之后,约束上要对跨时钟进行约束 。跨时钟约束的语法是set_clock_groups或者set_false_path,关于用于网上很多,可以自行查找。

set_clock_groups -asynchronous -group {jtag_inst1_TCK jtag_inst1_DRCK}

在所有时钟约束完成之后要保证时序报告的slack都为正值。

编译完成之后可以查看时序报告,也可以通过routingàxx.timing.rpt来查看路径详细延时信息

如果时序上还有违例,在result--> Routing-->timing.rpt文件中查看具体的路径。根据路径来解决具体的时序问题。

如果想查看更可以通过指令来打印或者通过print_critical_path来控制打印的路径数量 。

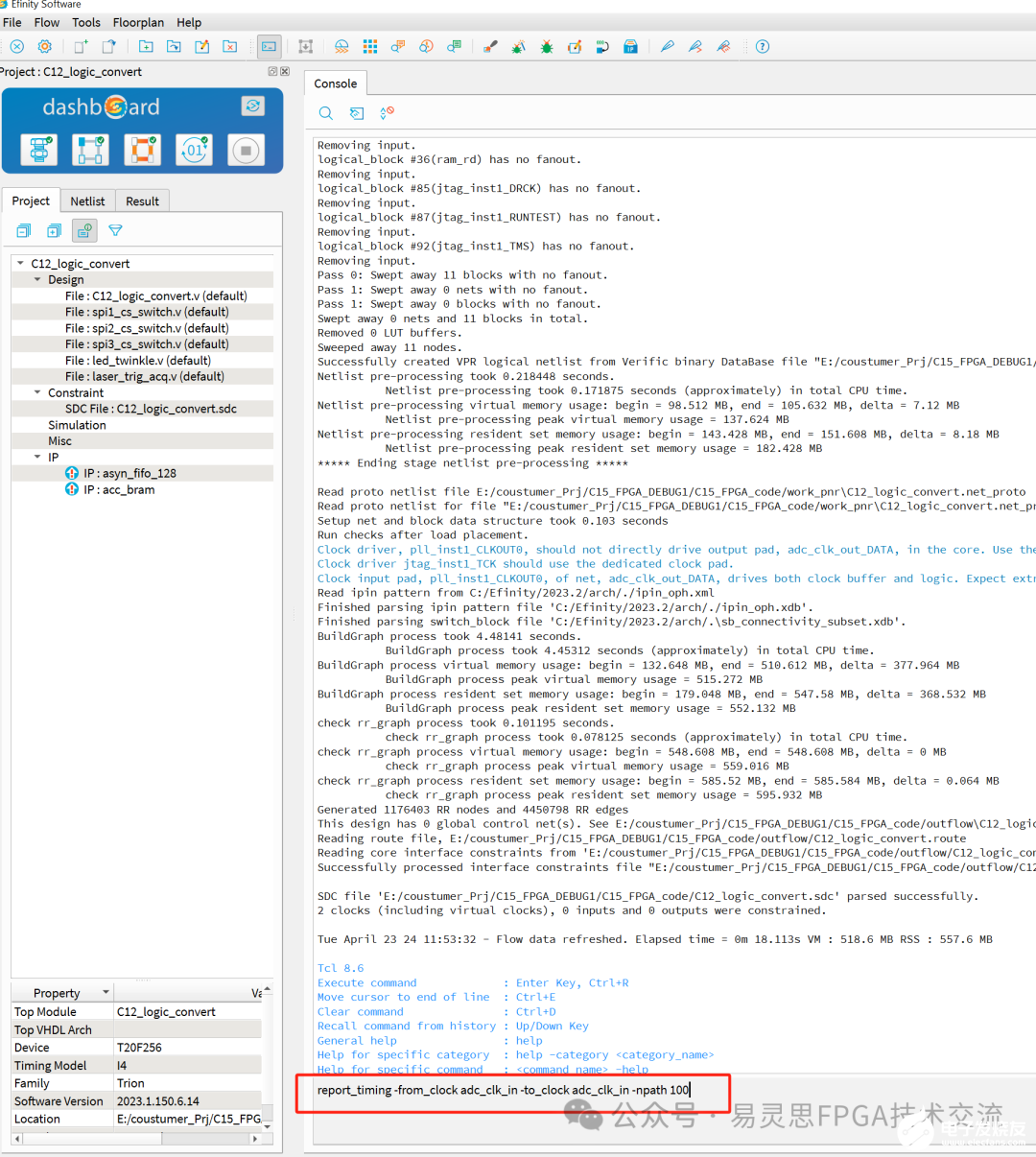

也可以通过report_timing来报告具体的时序路径及数量。

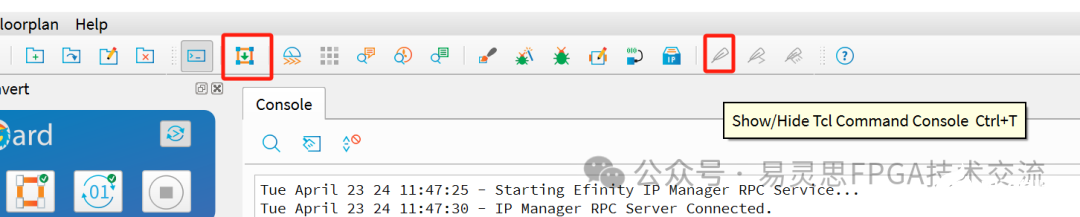

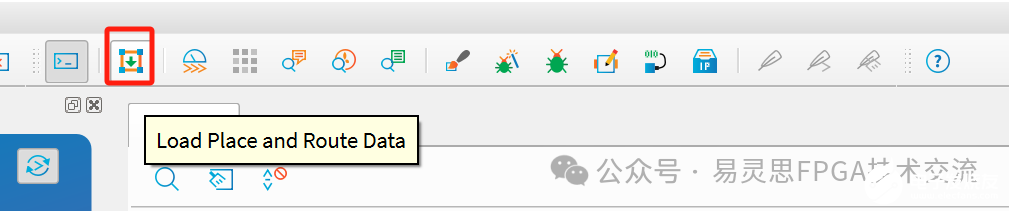

先打开Tcl CommandConsole,如果Show/Hide Tcl commandConsole是灰色的,要先点击Load Place and Route Data加载布局和布线的数据。

打开Tcl commandconsolel,使用report_timing命令来查看需要的路径。

具体report_timing的用法,请参考EfinityTiming Closure UserGuide.pdf。

-

FPGA

+关注

关注

1638文章

21852浏览量

609155 -

pll

+关注

关注

6文章

785浏览量

135603 -

时钟

+关注

关注

11文章

1761浏览量

132273 -

时序约束

+关注

关注

1文章

115浏览量

13502

发布评论请先 登录

相关推荐

气密性测试仪使用方法实操技巧:提高测试准确性的秘诀

北京迅为iTOP-RK3568开发板OpenHarmony系统南向驱动开发实操-HDF驱动配置LED

新手必看!SMA 插头 PCB 原理图连接实操指南

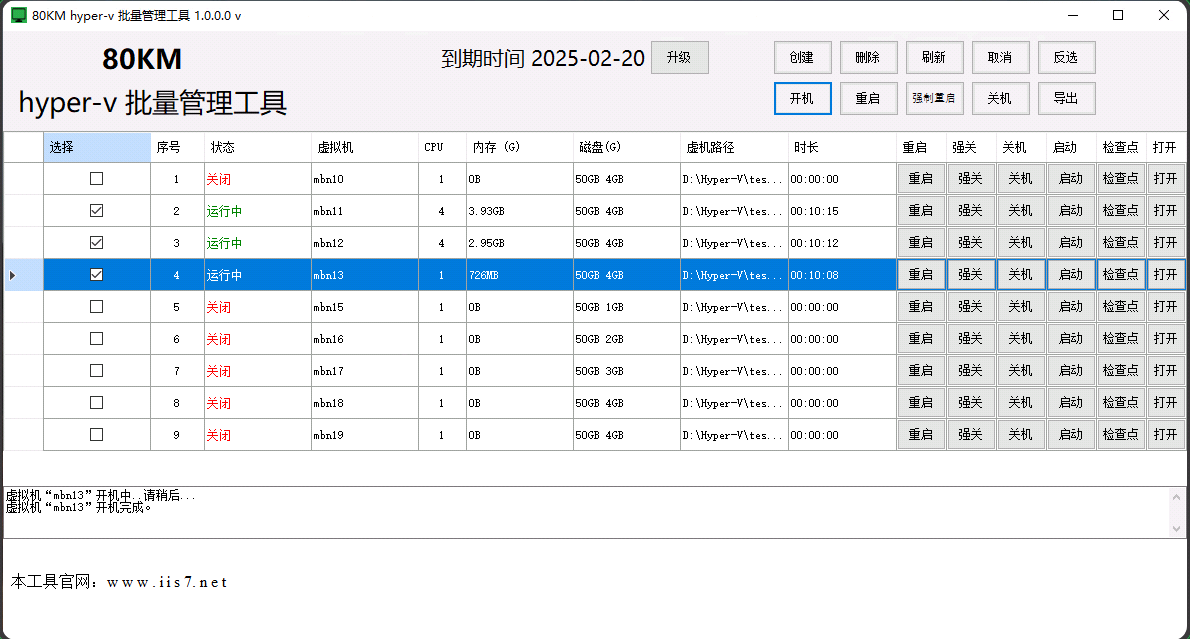

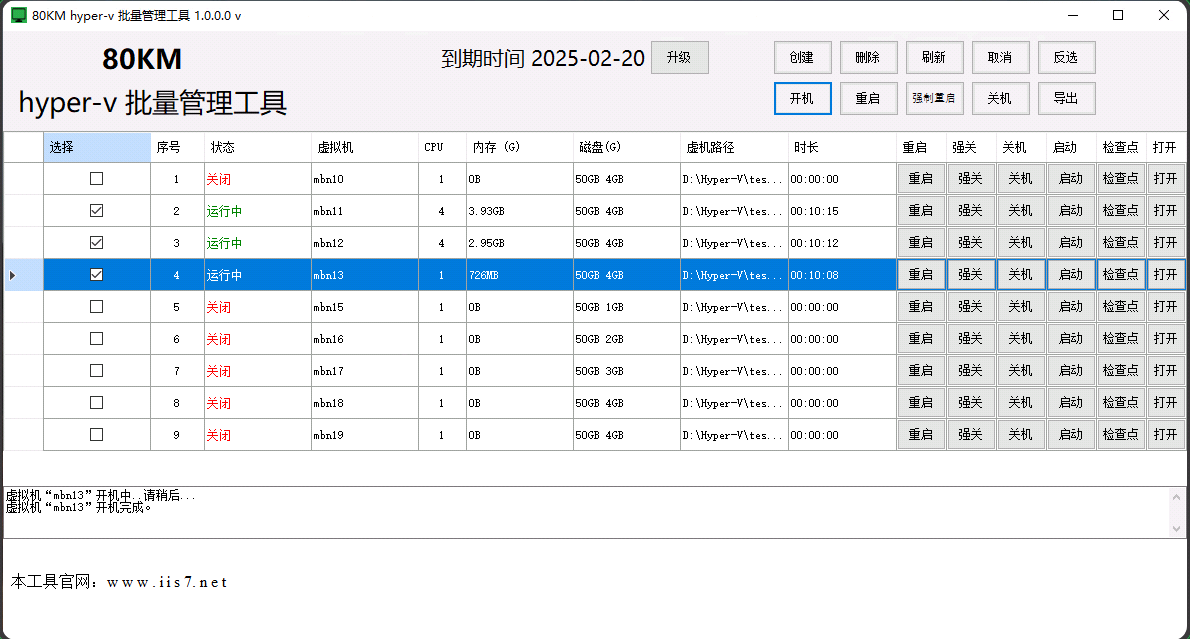

hyper v for win10,hyper v for win10的实操流程,hyper-v批量管理工具的使用指南

hyper 网卡,hyper 网卡的实操流程,hyper-v批量管理工具的使用指南

termius 中文,termius 中文的实操步骤,linux服务器远程连接的实用教程

时序约束一主时钟与生成时钟

常用时序约束使用说明-v1

【实操文档】在智能硬件的大模型语音交互流程中接入RAG知识库

FPGA 高级设计:时序分析和收敛

Xilinx FPGA编程技巧之常用时序约束详解

FPGA工程的时序约束实践案例

Xilinx FPGA的约束设置基础

时序约束实操

时序约束实操

评论