SOC(System on Chip,片上系统)设计中,时钟信号的控制对于整个系统的性能和功耗至关重要。本文将带您了解SOC设计中的一种时钟控制技术——Clock Gating,通过Verilog代码实例的讲解,让您对其有更深入的认识。

一、Clock Gating基本原理

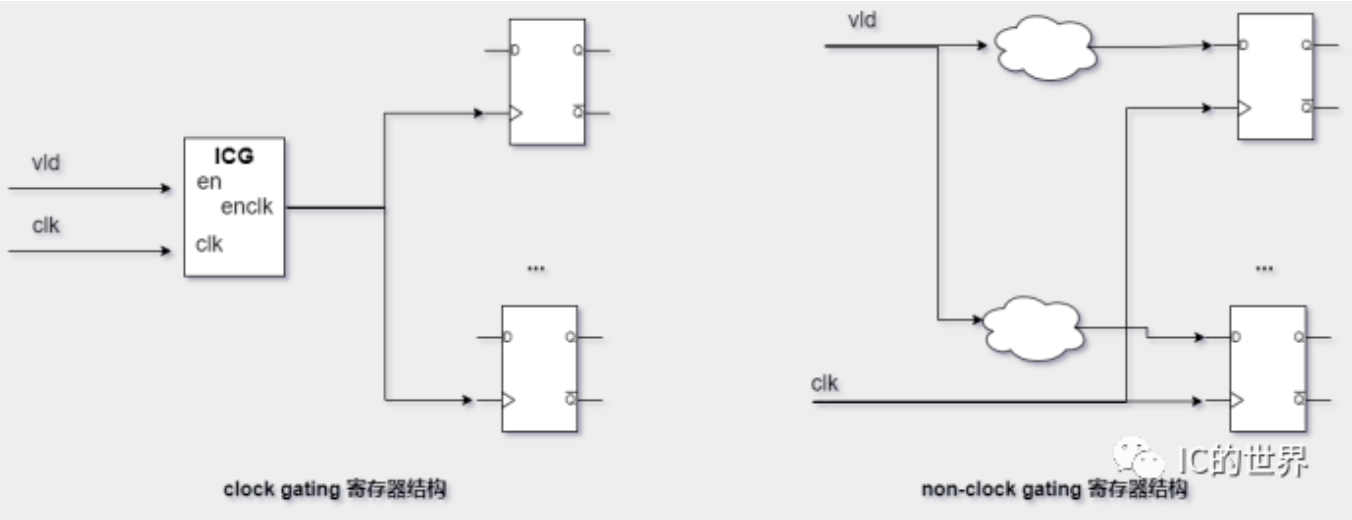

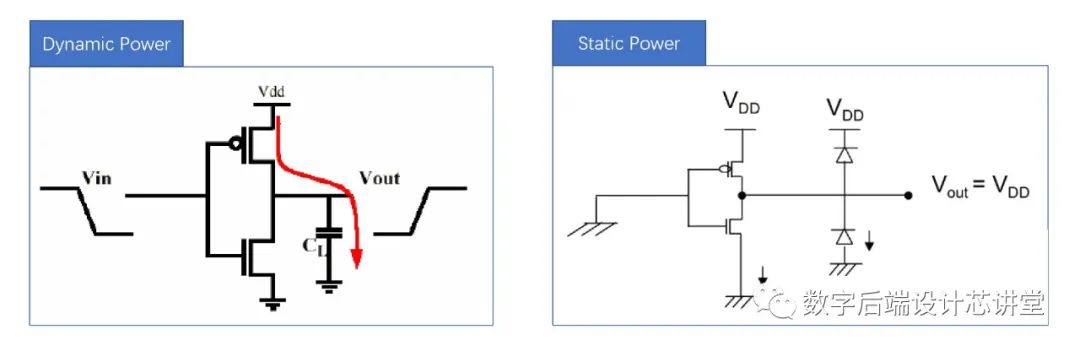

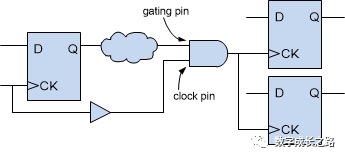

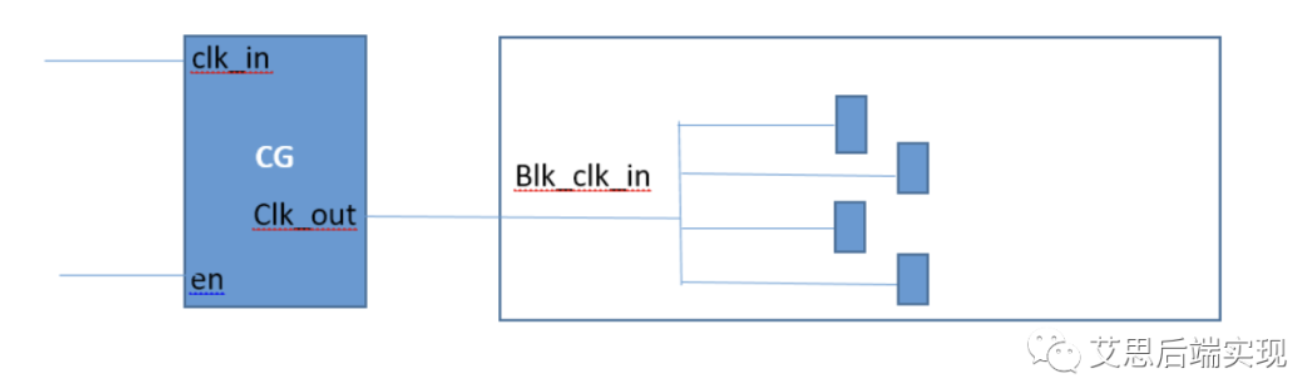

Clock Gating,即时钟门控,是一种在数字集成电路设计中常用的低功耗技术。它的基本思想是,在时钟信号传输到寄存器之前,通过控制逻辑来决定时钟信号是否需要传递给寄存器。如果某个寄存器在当前时钟周期内不需要进行操作,那么就可以通过Clock Gating技术关闭该寄存器对应的时钟信号,从而减少不必要的功耗。

二、Verilog实现Clock Gating

接下来,我们将通过一个简单的Verilog代码实例来讲解Clock Gating的实现。

假设我们有一个简单的2-to-1多路复用器(MUX),它有一个选择信号(SEL)、两个数据输入(A和B)和一个输出(Y)。我们希望在SEL无效时关闭多路复用器的时钟,以节省功耗。

以下是一个简单的Verilog代码示例:

module clock_gating_example(

input wire clk,

input wire rst_n,

input wire sel,

input wire a,

input wire b,

output reg y

);

wire gated_clk;

// Clock Gating Cell

assign gated_clk = clk & ~sel;

// 2-to-1 MUX

always @(posedge gated_clk or negedge rst_n) begin

if (!rst_n) begin

y <= 1'b0;

end else begin

y <= sel ? b : a;

end

end

endmodule

在这个例子中,我们使用了一个简单的Clock Gating单元,它由一个AND门和一个反相器组成。当选择信号(SEL)无效时,经过Clock Gating单元处理后的时钟信号(gated_clk)将关闭,从而停止多路复用器的时钟。

审核编辑:刘清

-

寄存器

+关注

关注

31文章

5619浏览量

130396 -

SoC设计

+关注

关注

1文章

151浏览量

19598 -

片上系统

+关注

关注

0文章

205浏览量

27727 -

多路复用器

+关注

关注

9文章

1065浏览量

66831 -

时钟信号

+关注

关注

4文章

510浏览量

30078

原文标题:Verilog实战解析:SOC设计中Clock Gating的基本原理与应用

文章出处:【微信号:快乐的芯片工程师,微信公众号:快乐的芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

无刷电机电调的基本原理

双脉冲测试基本原理及意义

串口通信基本原理是什么

线性电源的基本原理是什么

STM32基本原理简介

ASIC的clock gating在FPGA里面实现是什么结果呢?

SOC设计中Clock Gating的基本原理与应用讲解

SOC设计中Clock Gating的基本原理与应用讲解

评论