“GaAs逻辑电路仿真不收敛怎么办?”

使用GaAs工艺设计过逻辑电路的人大概率都遇到过各种各样奇奇怪怪的收敛性问题,比如一个+5V供电的电路竟然出现了几十上百伏的节点电压;又比如一个反相器Transient仿真总是提示Timestep too small。

01

一些典型的不收敛示例

(1)DC仿真时出现明显异常的电压或者电流,作者之前在WIN的诸多工艺上都遇到过节点电压超出电源电压的情况,比如+5V供电,输出电压达到了几十上百伏。

临时又找不到合适的配图了……

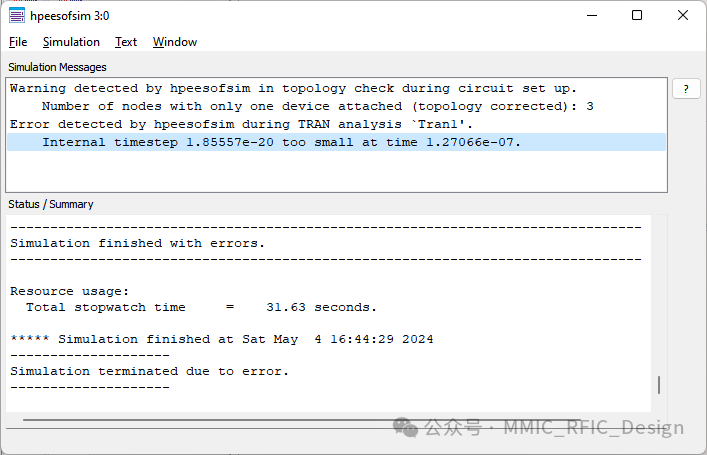

(2)Transient仿真时提示“Internal timestep too small”,如下图所示:

02

不收敛原因分析

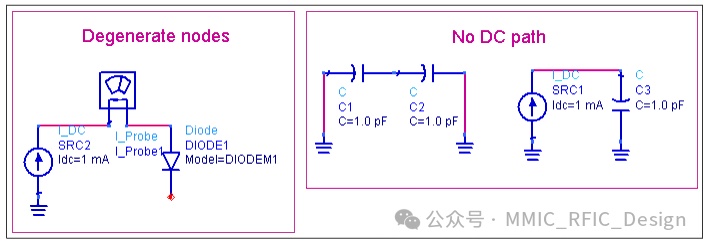

(1)最常见的原因还是在人,例如悬空的节点可能被仿真器自动移除,或者你的电路根本没有直流回路,DC仿真自然无法收敛:

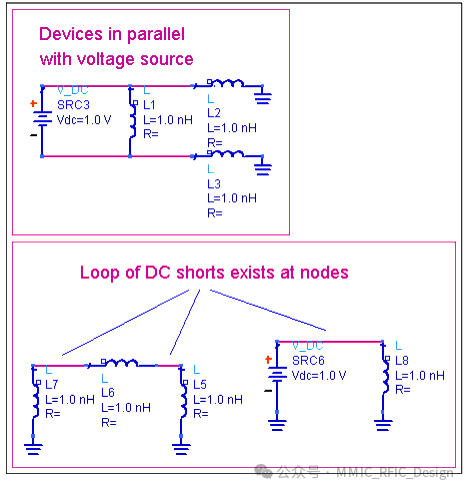

再比如电压源不能与理想电感并联:

还有一些不可能成立(无解)的电路:电压源不能并联、电流源不能串联。

或者设计的参数不合理,工作电压超出了模型的有效范围。

(2)第二常见的原因在于模型,GaAs pHEMT工艺的PDK大多是代工厂与Keysight合作开发的,至少是依赖了Keysight的技术支持,pHEMT器件模型大概率是ADS的EEHEMT模型,而模型参数又是针对RF电路优化的,用来进行S参数或者HB仿真的收敛性没问题,反而DC或Transient仿真时收敛性就表现很差。又比如说一些晶体管模型针对放大器应用做了优化,在合理的偏置点下仿真精度较高,但在接近夹断的甚至低于夹断电压的栅压偏置下仿真精度较差。

(3)仿真器参数设置不合理,通常是仿真精度要求太高,误差太大时就容易出现不收敛的情况。

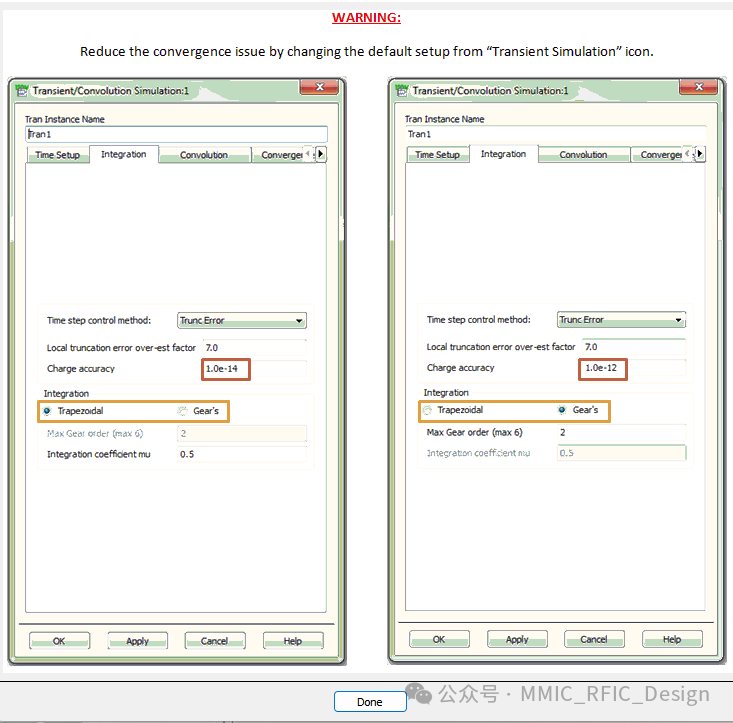

前面所述的EEHEMT模型并不局限于哪一家代工厂,很多家工厂的PDK都有类似的问题,尤其是在进行Transient仿真时,需要对电压或者电流的时域波形进行数值积分运算,而数值积分极容易因误差太大而导致不收敛。作为典型的GaAs代工厂代表,WIN给出的Transient收敛性改善建议是把积分算法由默认的Trapezoidal(梯形法)改为Gear's(预测校正法),同时把电荷精度由默认值1.0e-14改为1.0e-12。

ADS的help文档中有一段话是这样写的:

Like SPICE, this simulator uses the trapezoidal integration method described by the following equation as the default method for calculating derivatives at each time step t in the simulation. 【公式1】 For most circuits, this method will succeed. For those that do not, the simulator also supports Gear's backward difference method: 【公式2】 In this equation, the index k is called the order of the integration. For most circuits, Gear's method is no more accurate than the default trapezoidal integration technique. However, if a circuit analysis fails to converge, Gear's method may succeed where trapezoidal integration fails. In particular, oscillator circuits and any circuit that is characterized by stiff state equations may benefit from Gear's method. For a discussion of Gear's method and stiff state equations, refer to Chua and Lin, Computer-Aided Analysis of Electronic Circuits: Algorithms and Computation Techniques, Prentice-Hall, 1975.

【公式1】

【公式2】

最后一段的大意是:对大多数电路而言,Gear's积分法并不比默认的Trapezoidal 积分法精度更高,但是如果一个电路用Trapezoidal积分法仿真不收敛,那么改用Gear's积分法也许能收敛。特别地,对于振荡电路以及类似具有刚态方程的电路时采用Gear's积分法可能会更有利。

然而上述设置仅仅是对Transient仿真的收敛性有一定改善,并不能保证仿真一定能收敛。

03

个人方法

对于一些简单的GaAs逻辑电路(例如基础门电路,或者3-8译码器规模以下的组合逻辑),通过减小仿真步长、更换积分方法、修改仿真精度等方法基本上都可以解决。但是功能稍微更复杂的触发器、锁存器等很大可能还是不能收敛,例如幅相控制多功能芯片里需要用到的串并转换电路,其逻辑门的规模可能达到500左右的量级,要想跑通Transient仿真是非常困难的。

根据作者的经验,Cadence的Transient仿真器性能比ADS好很多,同样的电路用ADS仿真不收敛,改用Cadence就可能收敛;也可能是虽然用ADS仿真能收敛但是非常慢,而用Cadence仿真的速度就能快上几十倍。奈何绝大部分GaAs工艺的PDK的仿真模型仅支持ADS,Cadence版的PDK通常只支持LVS/DRC而没有电路仿真模型。

基于上述现实痛点,作者只能另辟蹊径。通过观察,作者发现,绝大部分仿真不收敛都发生在数据或始终跳变的时刻,这正是电路中的电压或者电流波形急剧变化的时候,极可能进入器件模型的不连续区间。是否可以自己建立一个简化的模型,仅模拟晶体管开关的结果,而去不关心晶体管开关切换这一瞬时的精确波形,从而改善仿真的收敛性?

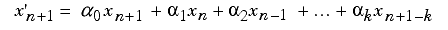

答案是肯定的,我用Verilog-A描述了一个简单的pHEMT模型,只包含三个特性:导通阈值、栅极的寄生肖特基二极管、导通电阻。有了这三个基本的要素,就可以模拟晶体管的开关特性和栅极漏电。而且为了确保电压、电流变化的连续性,我只用最基本的连续函数去描述其IV曲线。

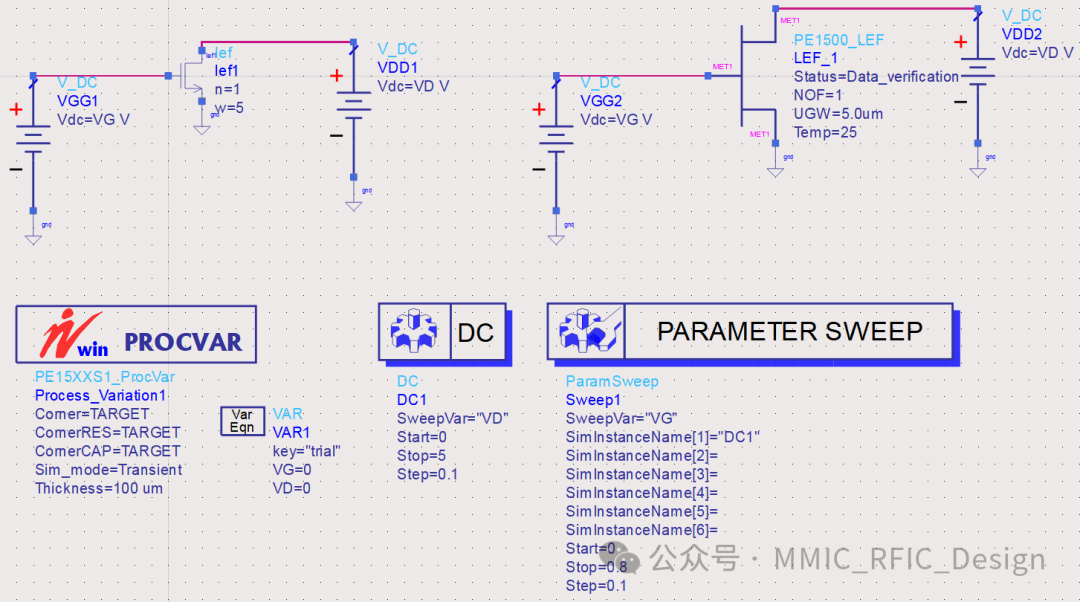

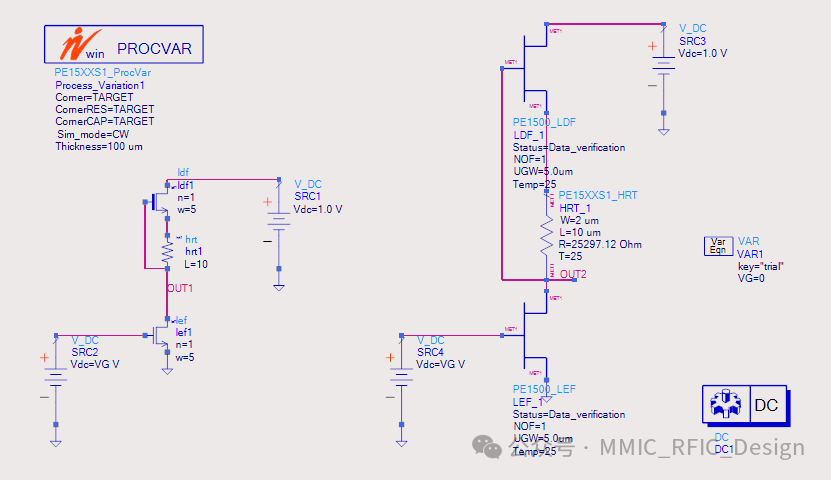

而且,由于上述晶体管模型过于简陋,它甚至完全不能很好地拟合PDK模型的DCIV:

(上图左侧是自定义简化模型,右侧是PDK模型)

(上侧两幅图是自定义简化模型的DCIV曲线,下侧两幅图是PDK模型的DCIV曲线)

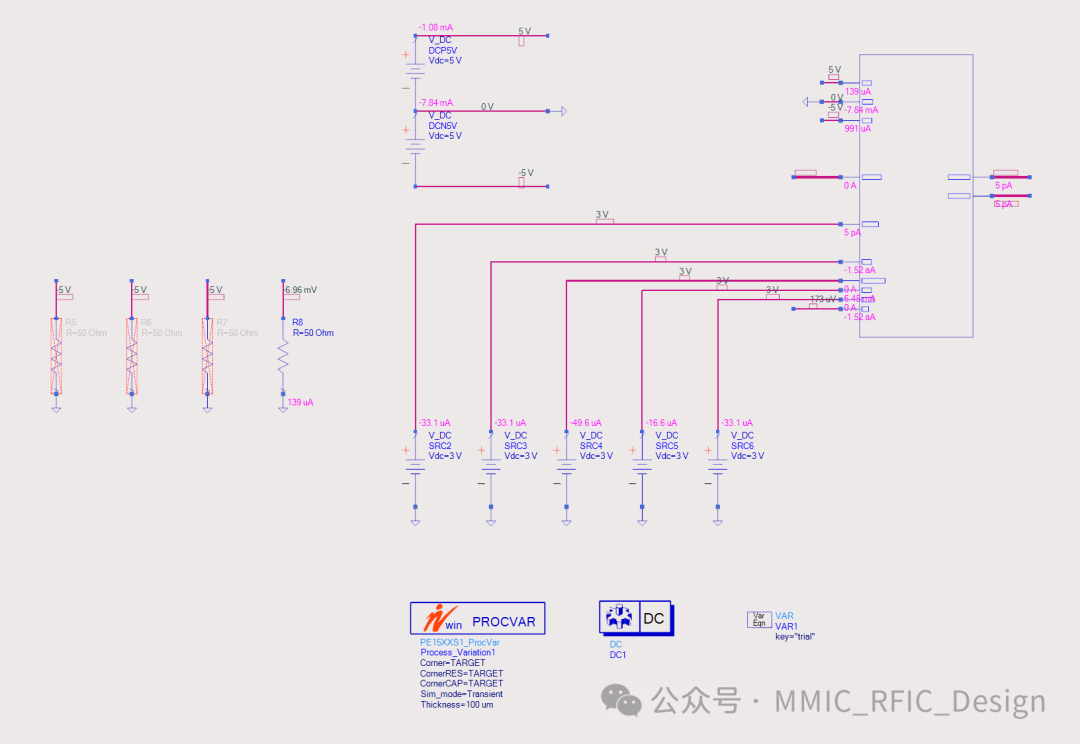

但是,前面说过了,我并不关心它自身有多精准,我更关心作为逻辑门时它能否较好地模拟其开关跳变的结果。因此上述自定义晶体管模型的参数我并不是用原始PDK晶体管模型的DCIV曲线去拟合的,而是让它在一个完整的门电路中、在一个特定的偏置条件下去拟合PDK模型结果,例如下面这个最基础的非门(反相器):

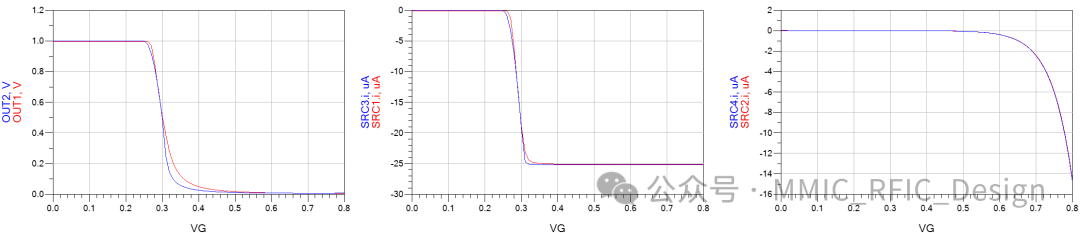

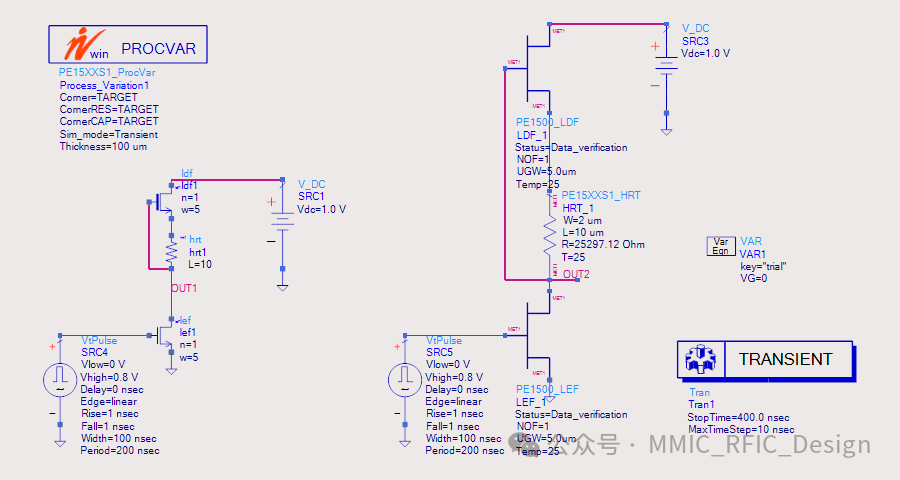

上面是DC仿真结果,下面是Transient仿真结果。可以看到自定义模型能够较为精确地模拟非门的输入逻辑阈值、输出电压、栅极电流、漏极电流。

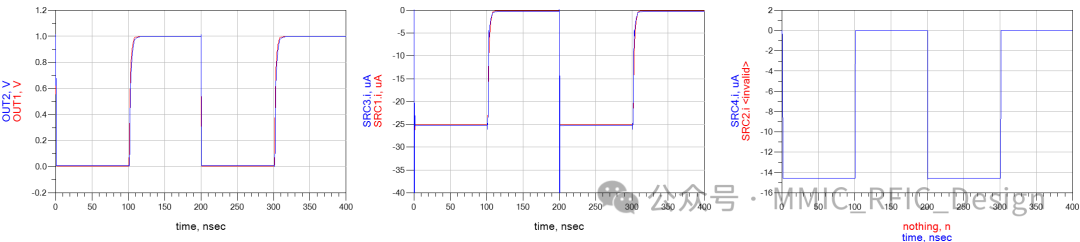

从Transient仿真结果可以清楚地看到自定义模型能够很好的拟合PDK模型在非门中的瞬态波形,正如前文所述,波形跳变的边沿被刻意平滑掉了,没有显著的尖峰,但是电压电流平稳后的波形都能完美重合。

基于类似的思想,我把电阻、电容、二极管、D-mode逻辑管和E-mode逻辑管的模型都做了简化并与原PDK模型进行拟合。这样,诸如串并转换这类对于GaAs来说算是较大规模的逻辑电路仿真也几乎再也没有遇到过不收敛的问题。

所以总结一下,对于比较复杂的GaAs逻辑电路,我的设计思路是:

使用PDK模型设计每个基本的逻辑门,确保每个基本的逻辑门在所有Corner、-55℃~+125℃温度下都能够正常工作,这种规模的逻辑电路基本上不会有太大的收敛性问题;

开始由基础的逻辑门构建更复杂的逻辑单元,比如锁存器、触发器,只要没有收敛性问题就继续使用PDK模型进行设计;

当逻辑复杂度达到一定规模后开始出现收敛性问题(比如由触发器构建移位寄存器时大概率就不容易收敛了),这时候更换成自定义模型(只对TARGET Corner@25℃进行参数拟合),并且对比更换前后的DC仿真状态是否一致,主要就是看静态电流和静态电压;

使用自定义的模型完成全部逻辑电路的时序功能验证,最后再更换为PDK模型检验一下完整电路的DC静态电压和静态电流是否吻合。

上述自定义模型仅在TARGET Corner@25℃进行参数拟合,仅仅是为了验证整体逻辑功能的正确性,无法全面反映全部逻辑电路在任意Corner/温度下的是否都能正常工作。当然,硬要针对每一个Corner、每一个温度极限都去进行参数拟合,再分别验证整体逻辑功能此时是否正常也是可以的,但实在是太麻烦了。

基于以上设计思路,作者已在WIN的PD25XX、PE15XX工艺上完成过多款串并转换与开关驱动电路的开发,经实测三温逻辑功能均正常,各项指标符合预期。

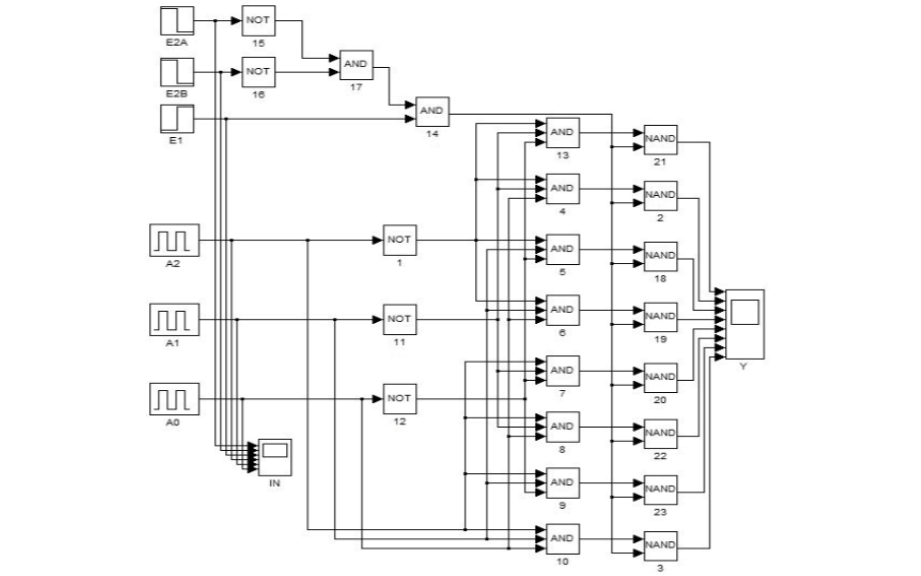

下面给出一个串并转换电路的仿真示例:

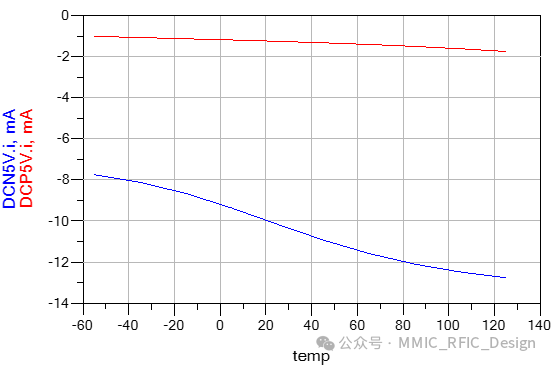

使用原始PDK模型仿真的工作电流随温度变化的曲线是:

而更换为自定义简化模型前后,在TARGET@25℃这一个点处,DC仿真得到的静态电流对比为:

•WIN

•+5V电流:1.31mA

•-5V电流:10.2mA

•自定义简化模型

•+5V电流:1.31mA •-5V电流:10.3mA

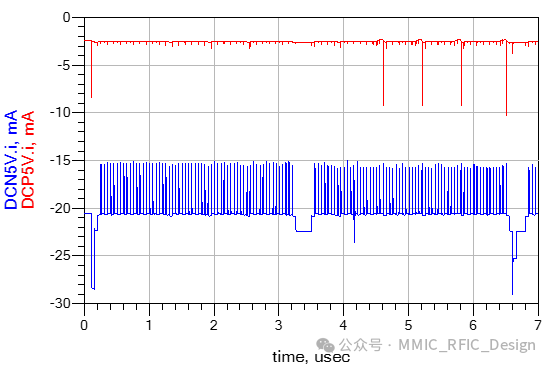

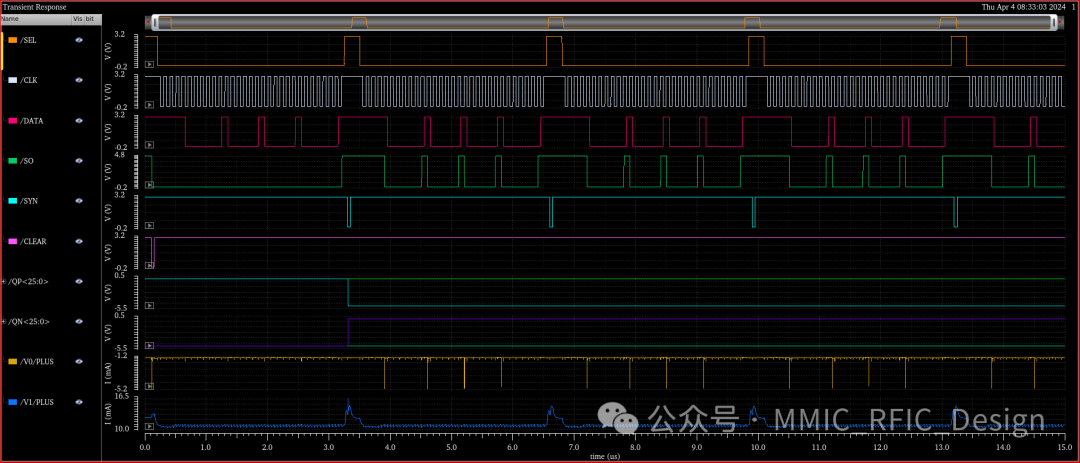

使用PDK模型Transient仿真无法收敛,使用自定义模型Transient仿真的+5V和-5V电源瞬态电流波形:

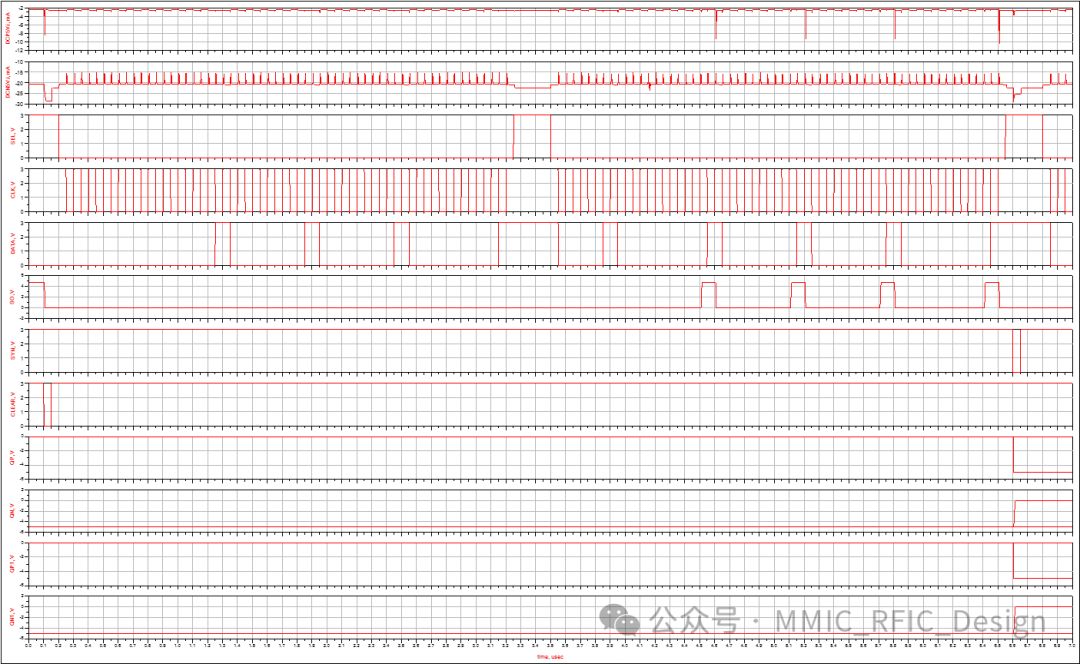

完整串并转换逻辑电路整体的仿真波形:

最后,使用自定义Verilog-A模型的另一个好处是,Cadence环境下也能进行设计和仿真了。

至于仿真速度上,同样的Verilog-A自定义模型,同一台电脑、同一个CentOS系统环境:在ADS下根据激励条件不同,Transient仿真大概需要40min~80min不等;在Cadence下根据激励条件不同,Transient仿真大概需要30s~60s不等。这两者在速度上的天壤之别读者自行体会吧!

审核编辑:刘清

-

逻辑电路

+关注

关注

13文章

494浏览量

42698 -

反相器

+关注

关注

6文章

311浏览量

43493 -

仿真器

+关注

关注

14文章

1019浏览量

83923 -

电源电压

+关注

关注

2文章

991浏览量

24073 -

ADS仿真

+关注

关注

1文章

71浏览量

10504 -

GaAs

+关注

关注

2文章

510浏览量

23063

原文标题:经验分享——GaAs逻辑电路ADS仿真不收敛怎么办?

文章出处:【微信号:芯片设计之路,微信公众号:芯片设计之路】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

求大佬帮忙解答使用tl494设计的开关型电源设计输出结果不收敛的问题

搭了一个临界模式的PFC电路,但是仿真显示不收敛,是哪里的问题?

请问ada4938仿真不收敛是否是我的电路图连接的问题

为什么s参数不收敛?有哪些方式导入s参数使得其仿真能够收敛?

Multisim的时序逻辑电路设计仿真

组合逻辑电路和时序逻辑电路比较_组合逻辑电路和时序逻辑电路有什么区别

使用Matlab实现组合逻辑电路的设计与仿真

GaAs逻辑电路ADS仿真不收敛怎么办?

GaAs逻辑电路ADS仿真不收敛怎么办?

评论