近日,新思科技对外透露,三星电子已使用新思科技的 Synopsys.ai EDA 工具,成功研发出基于 GAA 晶体管架构(包括 3nm 及更小制程)的“高端移动 SoC”,其中包含高端的 CPU 以及 GPU,并具备生成式 AI 功能。

据新思科技介绍,他们的 Synopsys.ai EDA 套件专为 CPU 高效运行而设计,为三星的 GAA 节点带来了卓越的 PPA(性能、功耗和面积)表现。

具体来看,新思科技的解决方案不但让三星电子省去了几周的手动设计时间,还使这款 SoC 的频率提高至 300MHz,动态功耗降低了 10%。

三星电子系统 LSI 部门副总裁 Kijoon Hong 对此表示:“我们与新思科技的长期合作,使得我们能够在最尖端的移动 CPU 核心和 SoC 设计中达到最佳的 PPA,这是一项重大突破;

“我们不仅证实了 AI 驱动的解决方案能助力我们达成 GAA 工艺技术的 PPA 目标,而且通过此次合作,我们构建了一个超高效率的设计系统,并持续取得显著成果。”

-

eda

+关注

关注

71文章

2758浏览量

173241 -

三星

+关注

关注

1文章

1525浏览量

31234 -

生成式AI

+关注

关注

0文章

503浏览量

474

发布评论请先 登录

相关推荐

三星芯片代工新掌门:先进与成熟制程并重

新思科技7月份行业事件

新思科技携手英特尔推出可量产Multi-Die芯片设计解决方案

三星电子将为日本Preferred Networks生产人工智能芯片

三星电子重塑北美AI版图:集结精锐力量,打造AI新篇章

三星电子正按计划推进eMRAM内存制程升级

新思科技物理验证解决方案已获得台积公司N3P和N2工艺技术认证

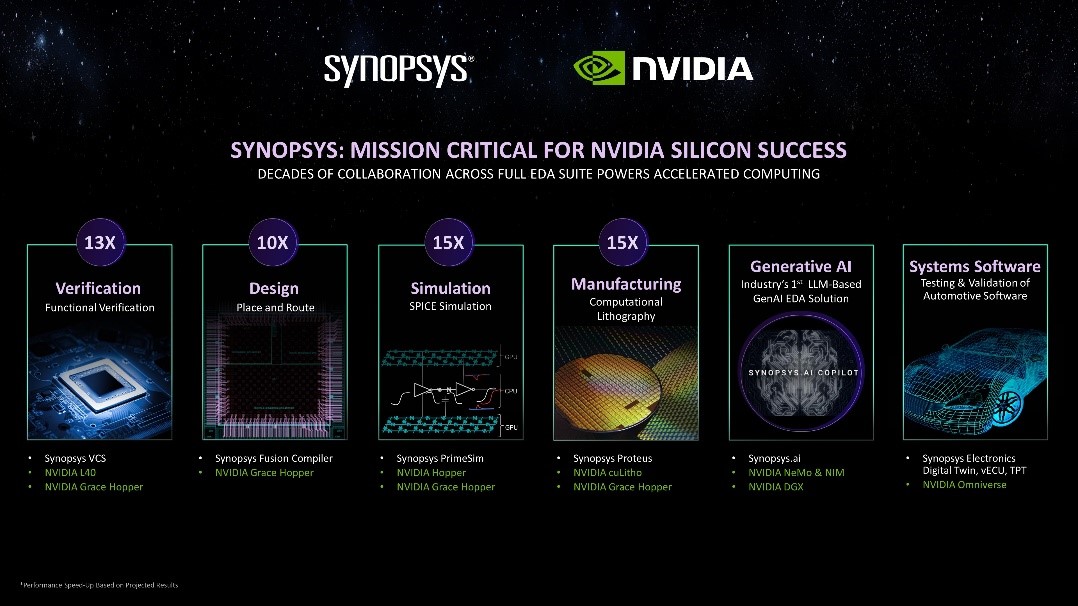

新思科技携手英伟达:基于加速计算、生成式AI和Omniverse释放下一代EDA潜能

三星电子采纳新思科技Synopsys.ai EDA套件,完成GAA制程验证

三星电子采纳新思科技Synopsys.ai EDA套件,完成GAA制程验证

评论