在数字集成电路设计中,Synopsys Design Constraints(SDC)是一种重要的约束语言,用于指导综合、布局布线等后续流程。本文将详细讲解SDC语法中的set_input_delay和set_output_delay,解释它们的原理、作用,并通过实例进行说明。

一、set_input_delay和set_output_delay的基本原理

1. 时序约束:在数字集成电路设计中,时序约束是一个重要的概念。它定义了信号从一个时钟边沿到另一个时钟边沿之间的时间延迟。时序约束有助于确保设计满足性能要求,如时钟周期、时钟偏斜、时钟抖动等。

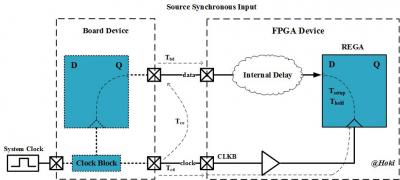

2. set_input_delay和set_output_delay:在SDC语法中,set_input_delay和set_output_delay是两种常用的时序约束命令。它们分别用于设置输入信号的建立时间和保持时间,以及输出信号的建立时间和保持时间。

3. 建立时间和保持时间:在时序分析中,建立时间和保持时间是两个关键参数。建立时间是指信号从低电平跳变到高电平,并在时钟边沿之后保持一段时间的最小要求。保持时间是指信号从高电平跳变到低电平,并在时钟边沿之前保持一段时间的最小要求。

二、set_input_delay和set_output_delay的作用

1. 确保信号正确传输:通过设置输入输出信号的建立时间和保持时间,可以确保信号在时钟边沿之前和之后都保持一段时间,从而保证信号的正确传输。

2. 优化设计性能:合理的设置输入输出信号的建立时间和保持时间,可以优化设计性能,提高电路的可靠性。

3. 支持时序分析:set_input_delay和set_output_delay是时序分析的重要组成部分,有助于确保设计满足时序要求。

三、set_input_delay和set_output_delay的举例说明

1. set_input_delay: 假设我们设计了一个简单的时序电路,包含一个时钟信号clk和一个输入信号A。为了确保信号A能够在时钟边沿之前和之后保持一段时间,我们可以使用set_input_delay命令进行设置。

set_input_delay -clock clk -max 2 [get_ports A]这条命令设置了输入信号A的最大建立时间为2ns,确保信号A在时钟边沿之前至少保持2ns。

2. set_output_delay: 同样,为了确保信号A在时钟边沿之后保持一段时间,我们可以使用set_output_delay命令进行设置。

set_output_delay-clockclk-min1[get_portsA]这条命令设置了输入信号A的最小保持时间为1ns,确保信号A在时钟边沿之后至少保持1ns。

四、总结

set_input_delay和set_output_delay是SDC语法中常用的时序约束命令,它们有助于确保信号的正确传输,优化设计性能,并支持时序分析。通过合理的设置输入输出信号的建立时间和保持时间,可以提高电路的可靠性。在数字集成电路设计中,了解和使用set_input_delay和set_output_delay是设计者必备的技能。

审核编辑:刘清

-

集成电路

+关注

关注

5391文章

11618浏览量

362981 -

SDC

+关注

关注

0文章

49浏览量

15574 -

时钟信号

+关注

关注

4文章

452浏览量

28653 -

CLK

+关注

关注

0文章

127浏览量

17228

原文标题:深入解析SDC语法中的set_input_delay和set_output_delay

文章出处:【微信号:快乐的芯片工程师,微信公众号:快乐的芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA的IO约束如何使用

Vivado IP核心约束错误的解决办法?

IC中inout port需要同时设置input_delay和output_delay吗?

input_delay应该设置为多少?

FPGA设计约束技巧之XDC约束之I/O篇 (上)

set_max_delay被覆盖的解决办法

Xilinx Vivado I/O延迟约束介绍

时序约束中如何精确找到匹配的template?

FPGA的虚拟时钟用于什么地方?

创建输入输出接口时序约束的窍门

set_output_delay的本质是什么?浅谈set_ouput_delay时序

怎样查看input/output delay是否生效

详细讲解SDC语法中的set_input_delay和set_output_delay

详细讲解SDC语法中的set_input_delay和set_output_delay

评论