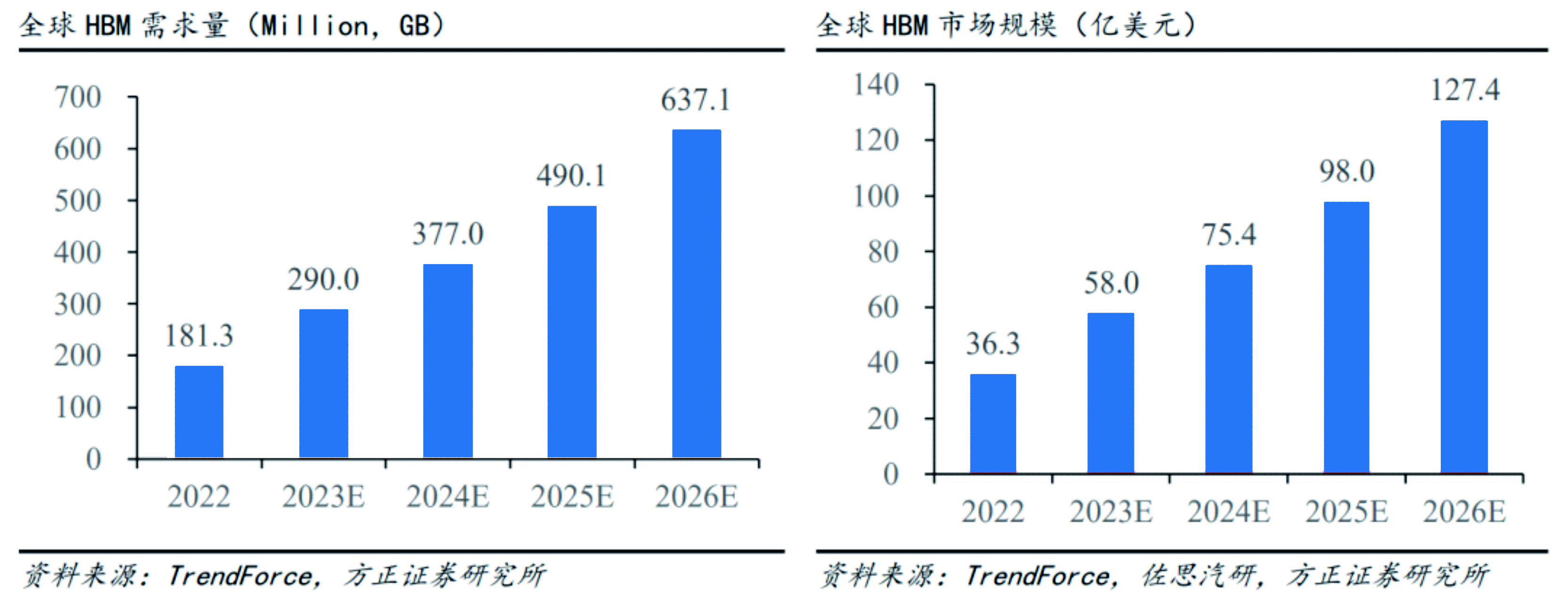

电子发烧友网报道(文/周凯扬)作为存储行业当下的新宠,HBM在AI的推动下,已经陷入了前所未有的市场狂热。最大的噱头自然是产能之争,比如SK海力士表示明年的HBM芯片产能已经基本卖完了,台积电今明两年的CoWoS先进封装产能也基本被巨头承包了,订单能见度已经从2027年延长至2028年。

对于存储大厂而言,这无疑是难能可贵的市场机遇,为了抓住这个机遇,他们也在加紧产能扩张,但除了产能上的竞争外,其HBM芯片本身的堆叠封装技术也决定了HBM的容量与性能,对订单产生了一定影响。

SK海力士-回流焊提高产能

过去,HBM DRAM芯片堆叠往往采用预填充绝缘膜的方式,借助韩美半导体等厂商提供的热压缩设备实现TC键合。通过在DRAM芯片之间放置一层NCF绝缘膜,通过热压缩(TC)使焊料熔化与凸点发生反应。

但这种传统的封装方式存在不少局限性,首先考虑到DRAM的厚度,如果出现研磨不均匀的情况,就会使得应力发生变化,从而出现弯曲等缺陷。同时,TC-NCF是一个对每个芯片施加压力的过程,所以不可能一次性实现多芯片的堆叠。

与此同时,为了在保持厚度的同时增加HBM容量,也就是垂直堆叠更多DRAM芯片,就势必需要减薄DRAM芯片40%,但这也会带来芯片本身容易弯曲等问题。为此,SK海力士先进封装开发团队自研了一种先进MR-MUF(批量回流模制底部填充)技术,并在HBM2e以上的产品中广泛使用。

借助合作伙伴日本纳美仕提供的环氧树脂模塑料(EMC)芯片封装用填充胶,在模塑过程中将其作为液体底部填充材料和散热,不必担心热量和应力对凸点造成影响,可以一次性形成多芯片间的焊点,同时具有高导热性,据SK海力士强调,这种先进MR-MUF技术,相比过去传统的MR-MUF技术效率提高三倍,散热能力提高了近2.5倍。

三星-TC-NCF与混合键合技术

在HBM3时代,SK海力士一直牢牢占据着第一的位置,这并非毫无来由,毕竟三星和美光两家厂商主要还是在使用TC-NCF的传统方案。据透露,三星的HBM3芯片良率只有10%到20%,而SK海力士的良率已经达到60%到70%。为此,三星也在竭力追赶,推进更大容量的HBM。今年2月底,三星发布了业内首个36GB的HBM3E 12H DRAM。

通过12层DRAM芯片堆叠,三星将其性能和容量均提升了50%。为了解决与8层标准HBM封装高度相同的要求,同时避免芯片弯曲,三星采用的也是SK海力士过去所用的热压缩绝缘薄膜的技术。不过很明显他们通过进一步降低NCF薄膜的厚度,实现更高层数的DRAM芯片堆叠。

但此前提到的TC-NCF技术劣势依然存在,尤其是在效率上。因此除了TC-NCF技术外,三星还准备了另外一条技术路线,也就是混合键合技术。混合键合技术采用Cu-Cu键合来替代HBM内部的焊料,从而实现更窄的间隙,这样即便是16层HBM,也可以采用更厚的DRAM芯片。

在近日举办的KMEPS会议上,三星宣布已经采用混合键合技术生产了16层HBM3的样品,不过在HBM4上的量产仍需要一定时间,他们还需要进一步改善这一技术的良率。

SK海力士也不例外,他们同样认为混合键合技术会是未来HBM提高密度和性能的关键,毕竟随着凸点数量、I/O引脚数量的增加,凸点间隙越来越窄,NUF填充胶能否穿透凸点也会成为问题。所以在未来的HBM4上,SK海力士也计划采用混合键合技术。

写在最后

不过考虑到设备、材料和封装技术尚不成熟,同时JEDEC将12层和16层HBM4的厚度规范放宽至775mm,混合键合技术的普及还需要一定时间,或许HBM厂商在HBM4上会继续沿用上一代的封装方案。

-

DRAM

+关注

关注

40文章

2310浏览量

183434 -

HBM

+关注

关注

0文章

378浏览量

14742 -

先进封装

+关注

关注

2文章

399浏览量

241

发布评论请先 登录

相关推荐

三星电子计划新建封装工厂,扩产HBM内存

三星电子或向英伟达供应先进HBM

2025年全球HBM产能预计大涨117%

三星电子调整HBM内存产能规划,应对英伟达供应延迟

台积电先进封装产能加速扩张

三星、SK海力士及美光正全力推进HBM产能扩张计划

台积电加速先进封装产能建设应对AI芯片需求

剑指HBM及AI芯片,普莱信重磅发布Loong系列TCB先进封装设备

产能之外,HBM先进封装的竞争

产能之外,HBM先进封装的竞争

评论